Изобретение относится к полупроводниковой микроэлектронике и может быть использовано при формировании СБИС ЗУ на арсениде галлия.

Цель изобретения повышение выхода годных путем увеличения точности задания пороговых напряжений транзисторов посредством влияния на степень нестехиометрии поверхностного слоя арсенида галлия.

П р и м е р 1. Используют структуру, содержащую подложку из полуизолирующего арсенида галлия с последовательно расположенными на ней: слоем n-типа арсенида галлия (концентрация носителей 1015 см-3 и толщина слоя 6000 ), сильно легированным слоем n-типа арсенида галлия (концентрация носителей 1015 см-3 и толщина слоя 150

), сильно легированным слоем n-типа арсенида галлия (концентрация носителей 1015 см-3 и толщина слоя 150 ), слоем n-типа арсенида галлия (концентрация носителей 1015 см-3 толщина слоя 1000

), слоем n-типа арсенида галлия (концентрация носителей 1015 см-3 толщина слоя 1000 ) и сильно легированным слоем п-типа арсенида галлия (концентрация носителей 1018 см-3 и толщина слоя 350

) и сильно легированным слоем п-типа арсенида галлия (концентрация носителей 1018 см-3 и толщина слоя 350 ). Со стороны эпитаксиальных слоев маскируют, например, слоем,полученным катодным распылением. В маске вскрывают окна в подзатворной области н/з транзистора, проводят термическое окисление в атмосфере кислорода при 530oС в течение 40 мин. Затем удаляют оксид путем отжига в атмосфере водорода (точка росы не ниже 70oС) при температуре 680oС в течение 35 мин. Затем вскрывают дополнительные окна в маске в подзатворной области н/о ПТШ, проводят термическое окисление в атмосфере кислорода при 530oС в течение 60 мин. Затем удаляют оксид путем отжига в атмосфере водорода при 680oС в течение 50 мин. При этом происходит углубление канавок и в подзатворной области н/з ПТШ, что необходимо учитывать при выборе времени окисления подзатворной области н/з ПТШ на первой стадии формирования канавок. Затем наносят затворный металл и по взрывной технологии формируют затворы н/о и н/з ПТШ (нормально-открытый и нормально-закрытый полупроводниковый транзистор Шоттки).

). Со стороны эпитаксиальных слоев маскируют, например, слоем,полученным катодным распылением. В маске вскрывают окна в подзатворной области н/з транзистора, проводят термическое окисление в атмосфере кислорода при 530oС в течение 40 мин. Затем удаляют оксид путем отжига в атмосфере водорода (точка росы не ниже 70oС) при температуре 680oС в течение 35 мин. Затем вскрывают дополнительные окна в маске в подзатворной области н/о ПТШ, проводят термическое окисление в атмосфере кислорода при 530oС в течение 60 мин. Затем удаляют оксид путем отжига в атмосфере водорода при 680oС в течение 50 мин. При этом происходит углубление канавок и в подзатворной области н/з ПТШ, что необходимо учитывать при выборе времени окисления подзатворной области н/з ПТШ на первой стадии формирования канавок. Затем наносят затворный металл и по взрывной технологии формируют затворы н/о и н/з ПТШ (нормально-открытый и нормально-закрытый полупроводниковый транзистор Шоттки).

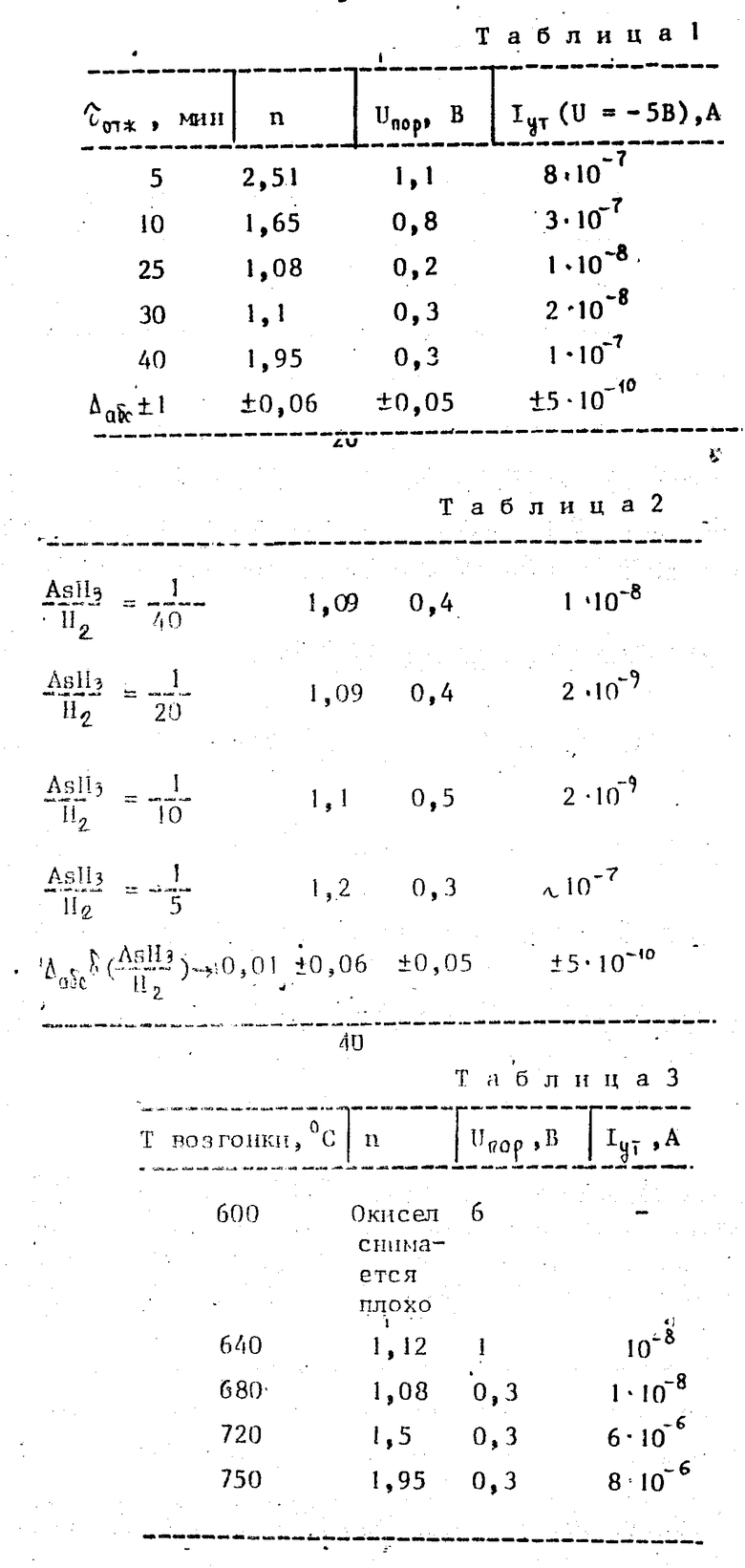

Экспериментальные результаты для различных режимов обработки сведены в табл.1-3.

П р и м е р 2. При формировании структуры проводят все операции, описанные в примере 1, но удаление оксида проводят в смешанной атмосфере водорода и арсина при относительных расходах последних 10 1.

П р и м е р 3. При формировании структуры проводят все операции, описанные в примере 1, но термическое окисление проводят при 400oС в течение 60 мин. При этом, как показывают результаты измерений электрофизических характеристик барьера Шоттки (БШ), для оптимизированной длительности отжига (τотж ≈ 20 мин) токи утечки обратно-смещенного БШ имеют практически тот же порядок величин, но разброс относительных величин пороговых напряжений ("пятки") на прямосмещенных ВАХ и коэффициентов неидеальности ВАХ БШ превышает 2% Средняя величина коэффициента неидеальности составляет при этом 1,1.

П р и м е р 4. При формировании структуры проводят все операции, описанные в примере 1, но термическое окисление проводят при 600oС в течение 25 мин. При этом, как показывают результаты измерений электрофизических характеристик БШ, для оптимизированной длительности отжига (τотж ≈ 15-20 мин), коэффициент неидеальности ВАХ БШ составляет величину 1,2, а величина пороговых напряжений ("пятка") на прямосмещенных ВАХ возрастает до величины 0,9-1,0 В. Повышение коэффициента неидеальности ВАХ БЩ и величины "пятки" связано, по-видимому, с появлением при более высокотемпературных отжигах термического оксида других модификаций.

Таким образом, оптимальные режимы следующие 1. Окисление Ток 530oС±5 в атмосфере "сухого" кислорода в течение 30 мин. 2. Отжиг Тотж 680oС±5 в атмосфере водорода в течение 25 мин (см.табл.1). 3. Отжиг Тотж 680oС±5 в течение 25 мин в атмосфере  (см.табл.2).

(см.табл.2).

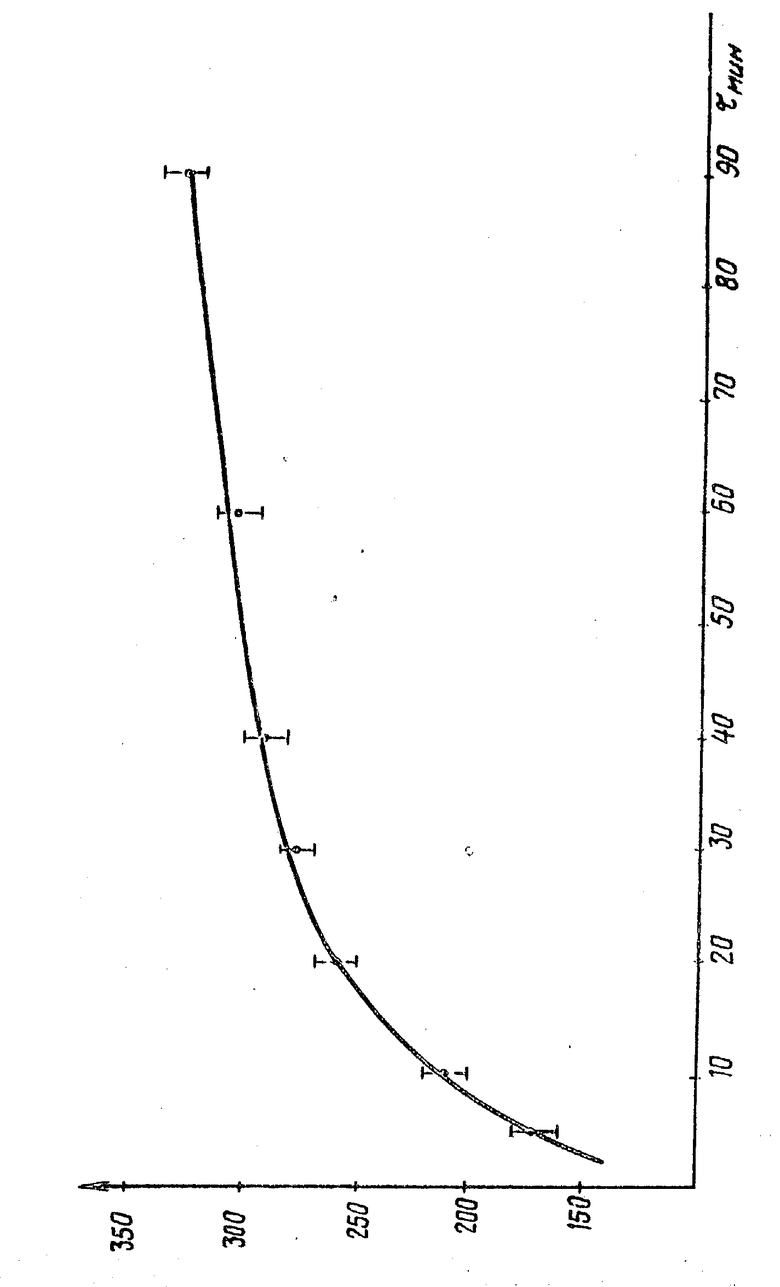

На чертеже показана зависимость глубины формируемых канавок от времени, которая обеспечивает точность глубины формирования канавок ≈1% а также нужную стехиометрию приповерхностного слоя GaAs области затвора. Время окисления для табл.1, 2 составляет 30 мин, температура окисления 53oС, τ - время возгонки окисла; n коэффициент неидеальности; Uпор - пороговое напряжение; Iут токи утечки барьера Шоттки; Δабс - абсолютное отклонение параметра; δ относительная ошибка.

В табл.1 дана характеристика алюминиевого барьера Шоттки (Тотж 680oС).

В табл. 2 дано изменение характеристик алюминиевого барьера Шоттки при отжиге в смеси мышьяка и водорода ( Тотж 680oС, tотж 25 мин). В табл.3 показан выбор оптимальной температуры возгонки (при Токис 530oС, 30 мин и τвозг 25 мин для алюминиевого контакта SячБИС ≈ 5•10-3 см-2).

Установлено, что в пограничной области термический оксид-арсенид галлия наблюдаются некоторые отклонения в величинах показателя преломления (W 4,8) и коэффициента поглощения (К 0,6), что связано с некоторой нестехиометрией пограничного слоя.

Для обеспечения возможности управления величиной порогового напряжения транзисторов через посредство влияния на степень нестехиометрии поверхностного слоя арсенида галлия (GaAs) в предлагаемом способе оксид удаляют путем отжига в атмосфере водорода и арсина при их относительных расходах 40 1-4 молярных объемов.

Диапазон заявляемых при термическом окислении температур снизу ограничен малыми скоростями окисления и большой неоднородностью полученных оксидных слоев, а сверху появлением модификаций оксида, удаление которых указанным способом не представляется возможным. Так, при температуре окисления 380oС скорость окисления, хотя и составляет  /мин, но однородность окисления по площади пластины является крайне неудовлетворительной (относительный разброс достигает 100-200%), что обусловлено неоднородностью исходного "природного" оксида на поверхности пластины. При температурах окисления 630oС (и далее, вплоть до 800oС) скорость окисления становится чрезмерно большой ( 300-500

/мин, но однородность окисления по площади пластины является крайне неудовлетворительной (относительный разброс достигает 100-200%), что обусловлено неоднородностью исходного "природного" оксида на поверхности пластины. При температурах окисления 630oС (и далее, вплоть до 800oС) скорость окисления становится чрезмерно большой ( 300-500  /мин), граница раздела оксид-полупроводниковый слой имеет сильную нестехиометрию (К ≈ 0,8-0,9, N 5,0), а полученный термический окисел не удаляется термическим отжигом в атмосфере водорода, либо в смеси водорода и арсина. Соотношение расходов водорода и арсина определено из возможности получения нужной стехиометрии состава поверхности GaAs. Диапазон заявляемых температур удаления оксида снизу ограничен минимальной температурой разложения оксидов галлия, а сверху нарушением стехиометрии GaAs. Время окисления (toк) выбирается согласно графику зависимости глубины окисления от времени и конкретных электрофизических и геометрических параметров эпитаксиальных слоев рабочей структуры с использованием известных соотношений. Глубина канавки при tок< 5 мин слишком мала, выбор toк>90 мин, нецелесообразен, так как глубина окисления не растет. Время отжига (τотж) влияет на качество (стехиометрию и наличие остаточных пленок оксида) поверхности формируемых канавок, в указанном температурном диапазоне слабо зависит от температуры и времени предварительного окисления. Его оптимальные значения составляют величины 20-40 мин, что демонстрируется результатами полученных электрофизических параметров характеристик барьеров Шоттки, представленных в табл. 1 и 2. При τотж>40 мин и τотж<10 мин Uпор выходит за допустимые пределы.

/мин), граница раздела оксид-полупроводниковый слой имеет сильную нестехиометрию (К ≈ 0,8-0,9, N 5,0), а полученный термический окисел не удаляется термическим отжигом в атмосфере водорода, либо в смеси водорода и арсина. Соотношение расходов водорода и арсина определено из возможности получения нужной стехиометрии состава поверхности GaAs. Диапазон заявляемых температур удаления оксида снизу ограничен минимальной температурой разложения оксидов галлия, а сверху нарушением стехиометрии GaAs. Время окисления (toк) выбирается согласно графику зависимости глубины окисления от времени и конкретных электрофизических и геометрических параметров эпитаксиальных слоев рабочей структуры с использованием известных соотношений. Глубина канавки при tок< 5 мин слишком мала, выбор toк>90 мин, нецелесообразен, так как глубина окисления не растет. Время отжига (τотж) влияет на качество (стехиометрию и наличие остаточных пленок оксида) поверхности формируемых канавок, в указанном температурном диапазоне слабо зависит от температуры и времени предварительного окисления. Его оптимальные значения составляют величины 20-40 мин, что демонстрируется результатами полученных электрофизических параметров характеристик барьеров Шоттки, представленных в табл. 1 и 2. При τотж>40 мин и τотж<10 мин Uпор выходит за допустимые пределы.

Способ позволяет увеличить процент выхода годных СБИС, так как зависимость глубины формируемых канавок от времени имеет логарифмический характер, а поверхность канавок после возгонки термического оксида свободна от сторонних и собственных оксидов.

Увеличение процента выхода годных на стадии корректировки каналов ПТШ составляет: в случае допустимого разброса глубин травления ( ) до 10% с 5 до 90% в случае допустимого разброса глубин травления (

) до 10% с 5 до 90% в случае допустимого разброса глубин травления ( )≅1% с 0,1 до 50% ТТТ1

)≅1% с 0,1 до 50% ТТТ1

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛЕВЫХ ТРАНЗИСТОРОВ С САМОСОВМЕЩЕННЫМ ЗАТВОРОМ | 1989 |

|

SU1628766A1 |

| ПОЛЕВОЙ ТРАНЗИСТОР ШОТТКИ | 1991 |

|

RU2025831C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОЩНЫХ СВЧ ПОЛЕВЫХ ТРАНЗИСТОРОВ С БАРЬЕРОМ ШОТТКИ | 2002 |

|

RU2227344C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ | 1992 |

|

RU2029413C1 |

| СПОСОБ ПОЛУЧЕНИЯ ДИЭЛЕКТРИЧЕСКИХ ПОКРЫТИЙ | 1980 |

|

SU940601A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ВЫПРЯМЛЯЮЩИХ КОНТАКТОВ К АРСЕНИДУ ГАЛЛИЯ ЭЛЕКТРОХИМИЧЕСКИМ ОСАЖДЕНИЕМ РУТЕНИЯ | 2016 |

|

RU2666180C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛЕВЫХ ТРАНЗИСТОРОВ С САМОСОВМЕЩЕННЫМ ЗАТВОРОМ | 1988 |

|

SU1565292A1 |

| СПОСОБ ПОЛУЧЕНИЯ ЭПИТАКСИАЛЬНЫХ СТРУКТУР НА ОСНОВЕ АРСЕНИДА ГАЛЛИЯ | 1990 |

|

RU1771335C |

| СПОСОБ ИЗГОТОВЛЕНИЯ МДП-ТРАНЗИСТОРОВ | 1989 |

|

SU1597018A1 |

| ЭЛЕМЕНТ ПАМЯТИ | 1984 |

|

SU1153768A1 |

Изобретение относится к полупроводниковой электронике и может быть использовано при формировании СБИС ЗУ на арсениде галлия. Цель изобретения - повышение выхода годных путем увеличения точности задания пороговых напряжений транзисторов посредством влияния на степень нестехиометрии поверхностного слоя aрсенида галлия. Осуществляют формирование канавок для подзатворных областей нормально закрытых транзисторов путем термического окисления областей эпитаксиальных слоев через окна в маске, в будущих местах расположения канавок, на заданную глубину в атмосфере сухого кислорода при 400-600oС с длительностью 5-20 мин с последующим удалением оксида посредством отжига структуры в атмосфере водорода при 600-700oС в течение 10-40 мин. Отжиг также может проводиться в атмосфере смеси водорода и арсина при их относительных расходах 40 : 1-4. Способ позволяет на 50-90% повысить выход годных схем. 1 з.п.ф-лы, 3 табл., 1 ил.

| Способ получения молочной кислоты | 1922 |

|

SU60A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Bent G | |||

| et al | |||

| Remtojule logic circuit using normally of GaAs mcS | |||

| j.t.s | |||

| Electronics lett, 1977, v.13, n 21, p.644. | |||

Авторы

Даты

1996-07-10—Публикация

1987-07-06—Подача