Изобретение относится к вычислительной технике и может быть исполь- зовано для управления передачей информации в резервированных многопроцессорных вычислительных системах, построенных на базе системного интерфейса И41,

Целью изобретения является упрощение устройства за счет использования арбитража магистрали системы для управления передачей информации.

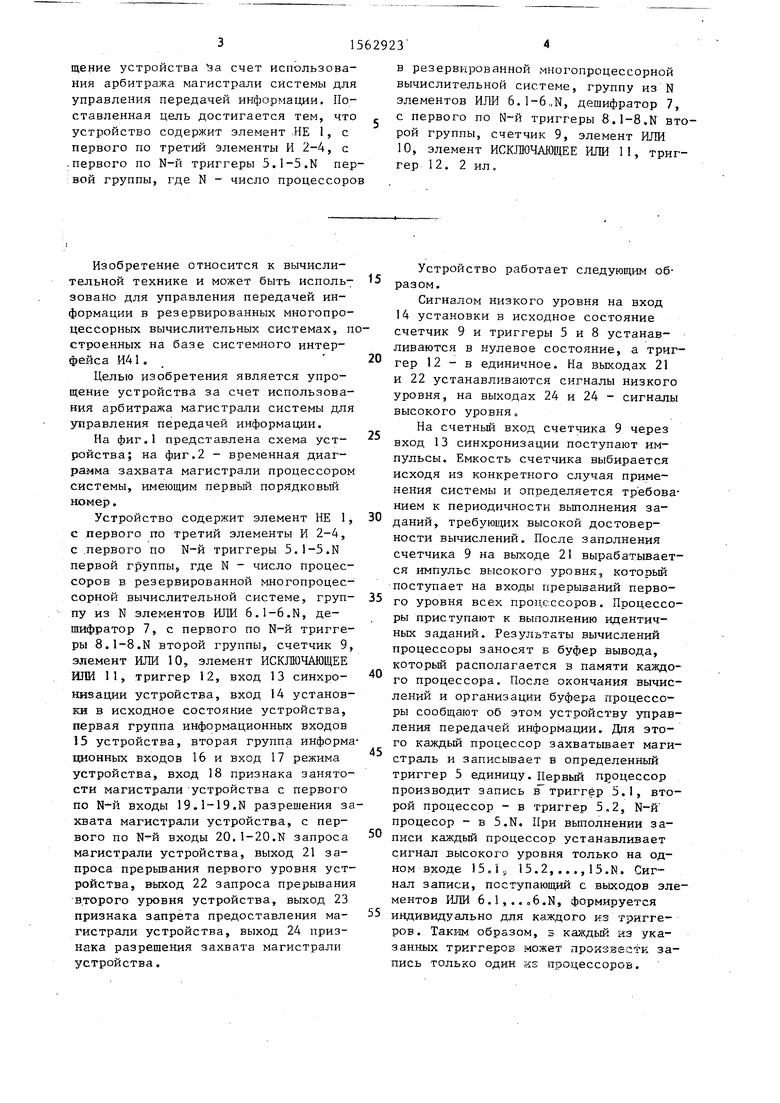

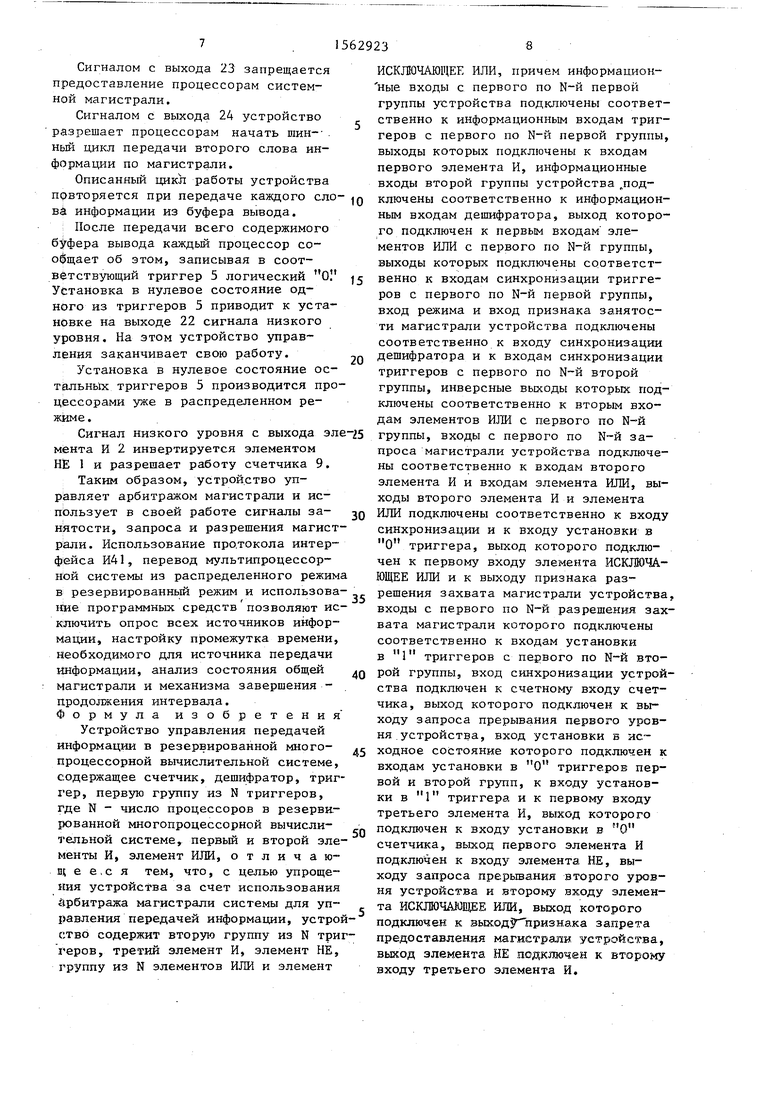

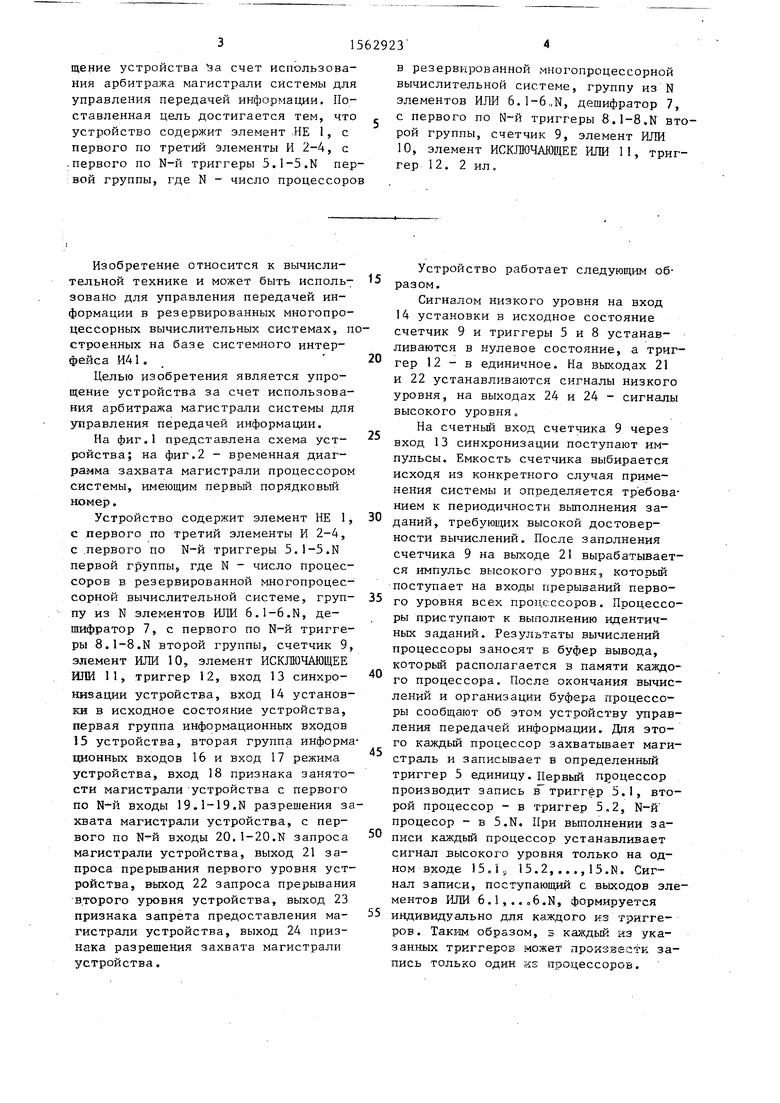

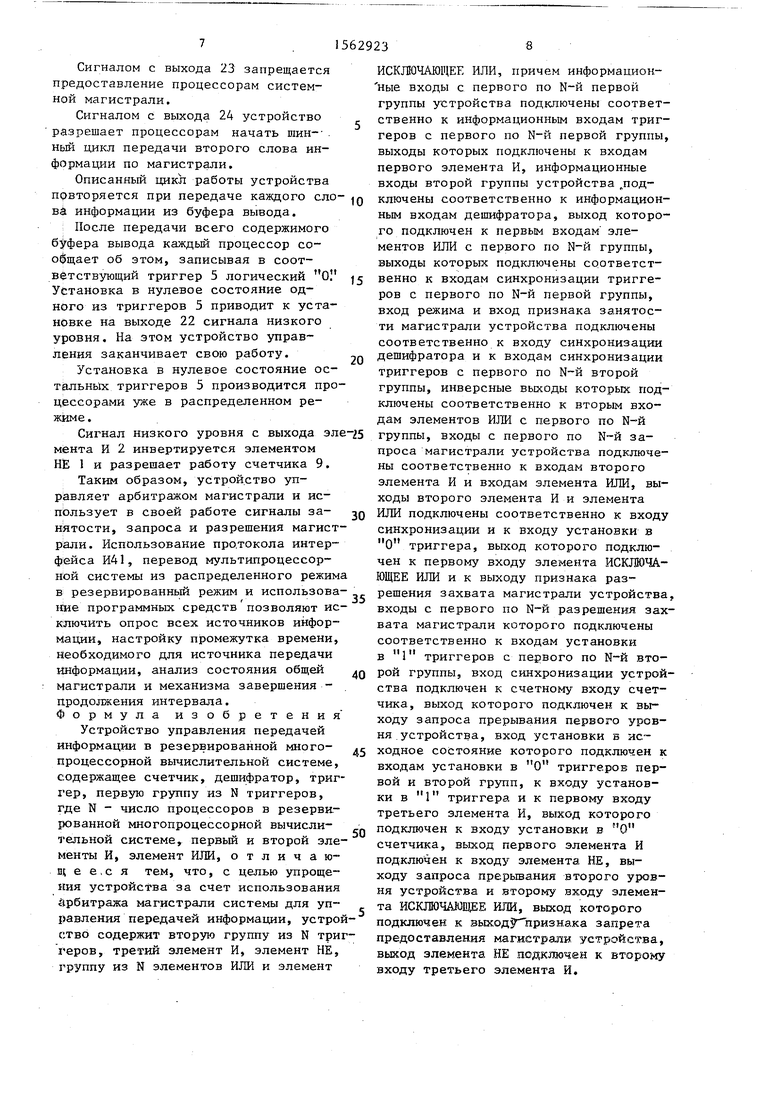

На фиг о 1 представлена схема уст- ройства; на фиг.2 - временная диаграмма захвата магистрали процессором системы, имеющим первьй порядковый номер.

Устройство содержит элемент НЕ 1, с первого по третий элементы И 2-4, с первого по N-й триггеры 5.1-5.N первой группы, где N - число процессоров в резервированной многопроцессорной вычислительной системе, труп- пу из N элементов ИЛИ 6.1-6.N, дешифратор 7, с первого по N-й триггеры 8.1-8.N второй группы, счетчик 9, элемент ИЛИ 10, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 11, триггер 12, вход 13 синхро- низации устройства, вход 14 установки в исходное состояние устройства, первая группа информационных входов 15 устройства, вторая группа информационных входов 16 и вход 17 режима устройства, вход 18 признака занятости магистрали устройства с первого по N-й входы 19.1-19.N разрешения захвата магистрали устройства, с первого по N-й входы 20.1-20.N запроса магистрали устройства, выход 21 запроса прерывания первого уровня устройства, выход 22 запроса прерывания второго уровня устройства, выход 23

признака запрета предоставления ма гистрали устройства, выход 24 признака разрешения захвата магистрали устройства.

-

5 0 0

5

5

Устройство работает следующим образом.

Сигналом низкого уровня на вход 14 установки в исходное состояние счетчик 9 и триггеры 5 и 8 устанавливаются в нулевое состояние, а триггер 12 - в единичное. На выходах 21 и 22 устанавливаются сигналы низкого уровня, на выходах 24 и 24 - сигналы высокого уровня.

На счетньй вход счетчика 9 через вход 13 синхронизации поступают импульсы. Емкость счетчика выбирается исходя из конкретного случая применения системы и определяется требованием к периодичности выполнения заданий, требующих высокой достоверности вычислений. После заполнения счетчика 9 на выходе 21 вырабатывается импульс высокого уровня, который поступает на входы прерываний первого уровня всех процессоров. Процессоры приступают к выполнению идентичных заданий. Результаты вычислений процессоры заносят в буфер вывода, который располагается з памяти каждого процессора. После окончания вычислений и организации буфера процессоры сообщают об этом устройству управления передачей информации. Для этого каждый процессор захватывает магистраль и записывает в определенный триггер 5 единицу. Первый процессор производит запись в триггер 5.1, второй процессор - в триггер 5.2, N-й процесор - в 5.N. При выполнении записи каждый процессор устанавливает сигнал высокого уровня только на одном входе 15,I; 15.2,...,15.N. Сигнал записи, поступающий с выходов элементов ИЛИ 6.1,..,6.N, формируется индивидуально для каждого кз триггеров. Таким образом, Б каждый из указанных триггеров может произвести запись только один из процессоров.

Рассмотрим формирование сигналов записи в триггеры 5.1...5.N на примере первого процессора системы. Сигналом низкого уровня на входе 19.1 процессору разрешается овладеть магистралью Этим сигналом триггер 8.1 по S-входу устанавливается в единичное состояние и на его инверсном выходе устанавливается сигнал низкого уровня. Процессор захватывает системную магистраль и устанавливает на входе 18 признака занятости сигнал низкого уровня. Затем процессор уста

соры начинают выполнение подпрограммы передачи информации по магистрали.

Каждый процессор начинает шинный цикл передачи первого слова информации из буфера вывода. Для этого процессоры выдают на входы 20 запроса магистрали сигналы низкого уровня и входят в состояние ожидания„ Наличие на всех входах 20 запроса магистрали сигналов низкого уровня свидетельствует о том, что все процессоры находятся в шинном цикле передачи первого слова информации. В этом случае

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для арбитража запросов | 1988 |

|

SU1596329A1 |

| Процессор для мультипроцессорной системы | 1988 |

|

SU1541626A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1986 |

|

SU1339576A1 |

| Устройство для сопряжения электронной вычислительной машины с общей магистралью | 1987 |

|

SU1411765A1 |

| Устройство для сопряжения вычислительных машин с магистралью | 1988 |

|

SU1647576A1 |

| УСТРОЙСТВО ДЛЯ ПОДКЛЮЧЕНИЯ ИСТОЧНИКА ИНФОРМАЦИИ К ОБЩЕЙ МАГИСТРАЛИ | 1991 |

|

RU2020560C1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1987 |

|

SU1432580A1 |

| УСТРОЙСТВО ДЛЯ ПОДКЛЮЧЕНИЯ ИСТОЧНИКА ИНФОРМАЦИИ К ОБЩЕЙ МАГИСТРАЛИ | 1991 |

|

RU2020561C1 |

| Многоканальное устройство для распределения заданий процессорам | 1987 |

|

SU1427368A1 |

| Система обмена данными в вычислительной сети | 1991 |

|

SU1807493A1 |

Изобретение относится к вычислительной технике и может быть использовано для управления передачей информации в резервированных многопроцессорных вычислительных системах, построенных на базе системного интерфейса И41. Цель изобретения - упрощение устройства за счет использования арбитража магистрали системы для управления передачей информации. Поставленная цель достигается тем, что устройство содержит элемент НЕ 1, с первого по третий элементы И 2 - 4, с первого по N-й триггеры 5.1-5.N первой группы, где N - число процессоров в резервированной многопроцессорной вычислительной системе, группу из H элементов ИЛИ 6.1-6.N, дешифратор 7, с первого по N-й триггеры 8.1-8.N второй группы, счетчик 9, элемент ИЛИ 10, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 11, триггер 12. 2 ил.

20

25

навливает на входе 16 код адреса уст- 15 Ha выходе элемента ИЛИ 10 вырабаты- ройства управления передачей и сигналом низкого уровня на входе 17 режима включает дешифратор 7. На выходе дешифратора 7 появляется сигнал низкого уровня. Так как на обоих входах элемента ИЛИ 6.1 присутствуют сигналы низкого уровня, на его выходе вырабатывается сигнал низкого уровня. Задним положительным фронтом этого сигнала информация с входа 15.1 записывается в триггер 5.1. Информацию на входе 15.1 устанавливает первый процессор.

После этого первый процессор освобождает магистраль и устанавливает на входе 18 занятости высокий уровень сигнала. Положительным фронтом сигнала на этом входе триггер 8.1 устанавливается в нулевое состояние и на его инверсном выходе устанавливается сигнал высокого уровня. Так как сигналы на входах 19 имеют недостаточную длительностьs то триггеры 8 позволяют сохранить информацию о номере процессора, осуществляющего запись в один из триггеров 5.

30

35

,вается сигнал низкого уровня, которым триггер 12 по R-вхсду устанавливается в нулевое состояние. При этом на выходе 23 устанавливается сигнал высокого уровня, а на выходе 24 - сигнал низкого уровня.

Сигналом с выхода 23 разрешается арбитраж магистрали, и процессоры, в порядке присвоенных им приоритетов осуществляют передачу первого слова информации по магистрали.

Сигнал на выходе 24 устанавливает флаг во всех процессорах. Процессор, передавший слово, начинает анализировать этот флаг. При нулевом значении флага передачи следующего слова по магистрали не разрешается. При единичном значении флага процессор выбирает из своего буфера вывода еле дующее слово и начинает шинный цикл передачи его по магистрали.

Таким образом, процессоры, выполнившие передачу первого слова ин40 формации, не начинают передачу второго слова, пока на выходе 24 установлен низкий уровень сигнала. В этом случае на входах 20 запроса магистрали присутствуют как сигналы высокоПосле того, как все процессоры сообщат устройству управления о своей готовности к передаче (запишут единицы во все триггеры 5), на выходе элемента И 2, а значит, и на выходе 22 установится сигнал высокого уровня. Этот сигнал, проинвертированный элементом НЕ 1, устанавливает счетчик 9 в нулевое состояние.

Сигнал с выхода элемента И 2 поступает на один из входов элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 1 и на выходе 23 устройства устанавливается сигнал низкого уровня, которым запрещается предоставление магистрали процессорам.

Сигнал высокого уровня с выхода 22 поступает на входы прерываний второго уровня всех процессоров. Процес

Ha выходе элемента ИЛИ 10 вырабаты-

,вается сигнал низкого уровня, которым триггер 12 по R-вхсду устанавливается в нулевое состояние. При этом на выходе 23 устанавливается сигнал высокого уровня, а на выходе 24 - сигнал низкого уровня.

Сигналом с выхода 23 разрешается арбитраж магистрали, и процессоры, в порядке присвоенных им приоритетов, осуществляют передачу первого слова информации по магистрали.

Сигнал на выходе 24 устанавливает флаг во всех процессорах. Процессор, передавший слово, начинает анализировать этот флаг. При нулевом значении флага передачи следующего слова по магистрали не разрешается. При единичном значении флага процессор выбирает из своего буфера вывода еле- дующее слово и начинает шинный цикл передачи его по магистрали.

Таким образом, процессоры, выполнившие передачу первого слова информации, не начинают передачу второго слова, пока на выходе 24 установлен низкий уровень сигнала. В этом случае на входах 20 запроса магистрали присутствуют как сигналы высокого уровня, так и сигналы низкого уровня. На выходе элемента ИЛИ 10 присутствует сигнал высокого уровня.

После того, как последний процес- сор выполнит передачу первого слова информации и установит свой сигнал запроса магистрали в высокое состояние, на выходе элемента И 3 установится сигнал высокого уровня, положи- тельным фронтом которого триггер 12 устанавливается в единичное состояние. На выходе 23 устанавливается сигнал низкого уровня а на выходе 24 - сигнал высокого уровня.

Сигналом с выхода 23 запрещается предоставление процессорам системной магистрали.

Сигналом с выхода 24 устройство разрешает процессорам начать шинный цикл передачи второго слова информации по магистрали.

Описанный цикл работы устройства повторяется при передаче каждого ело- ЗА информации из буфера вывода.

После передачи всего содержимого буфера вывода каждый процессор сообщает об этом, записывая в соответствующий триггер 5 логический О. Установка в нулевое состояние одного из триггеров 5 приводит к установке на выходе 22 сигнала низкого уровня. На этом устройство управления заканчивает свою работу.

Установка в нулевое состояние остальных триггеров 5 производится процессорами уже в распределенном режиме.

Сигнал низкого уровня с выхода эле мента И 2 инвертируется элементом НЕ 1 и разрешает работу счетчика 9.

Таким образом, устройство управляет арбитражем магистрали и использует в своей работе сигналы за- нятости, запроса и разрешения магистрали. Использование протокола интерфейса И41, перевод мультипроцессорной системы из распределенного режима в резервированный режим и использова- кие программных средств позволяют исключить опрос всех источников информации, настройку промежутка времени, необходимого для источника передачи информации, анализ состояния общей магистрали и механизма завершения - продолжения интервала. Формула изобретения

Устройство управления передачей Информации в резервированной много- процессорной вычислительной системе, содержащее счетчик, дешифратор, триггер, первую группу из N триггеров, Где N - число процессоров в резервированной многопроцессорной вычислительной системе, первый и второй элементы И, элемент ИЛИ, о т л и ч а ю- щ е е с я тем, что, с целью упрощения устройства за счет использования Арбитража магистрали системы для управления передачей информации, устро ство содержит вторую группу из N тригеров, третий элемент И, элемент НЕ, Группу из N элементов ИЛИ и элемент

0

Q

5

Q Q

.,- 50

ИСКЛЮЧАЮЩЕЕ ИЛИ, причем информаштон- ные входы с первого по первой группы устройства подключены соответственно к информационным входам триггеров с первого по N-Й первой группы, выходы которых подключены к входам первого элемента И, информационные входы второй группы устройства .подключены соответственно к информационным входам дешифратора, выход которого подключен к первым входам элементов ИЛИ с первого по N-й группы, выходы которых подключены соответственно к входам синхронизации триггеров с первого по N-Й первой группы, вход режима и вход признака занятости магистрали устройства подключены соответственно к входу синхронизации дешифратора и к входам синхронизации триггеров с первого по N-й второй группы, инверсные выходы которых подключены соответственно к вторым входам элементов ИЛИ с первого по N-й группы, входы с первого по N-й запроса магистрали устройства подключены соответственно к входам второго элемента И и входам элемента ИЛИ, выходы второго элемента И и элемента ИЛИ подключены соответственно к входу синхронизации и к входу установки в О триггера, выход которого подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и к выходу признака разрешения захвата магистрали устройства, входы с первого по N-й разрешения захвата магистрали которого подключены соответственно к входам установки в 1 триггеров с первого по N-й второй группы, вход синхронизации устройства подключен к счетному входу счетчика, выход которого подключен к выходу запроса прерывания первого уровня устройства, вход установки Б исходное состояние которого подключен к входам установки в О триггеров первой и второй групп, к входу установки в 1 триггера и к первому входу третьего элемента И, выход которого подключен к входу установки в О счетчика, выход первого элемента И подключен к входу элемента НЕ, выходу запроса прерывания второго уровня устройства и второму входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к выходу признака запрета предоставления магистрали устройства, выход элемента НЕ подключен к второму входу третьего элемента И.

Фиг. Z

| Устройство управления обменом по магистрали | 1984 |

|

SU1226478A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство управления передачей информации в многопроцессорной системе | 1986 |

|

SU1336024A1 |

Авторы

Даты

1990-05-07—Публикация

1988-10-24—Подача