СЛ

м

Ј to

о

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА КОНТРОЛЯ И УПРАВЛЕНИЯ ВЫСОКОВОЛЬТНЫМИ ЯЧЕЙКАМИ РАСПРЕДЕЛИТЕЛЬНОЙ СЕТИ ШАХТЫ | 1990 |

|

RU2037205C1 |

| Устройство для обмена данными в вычислительной сети | 1988 |

|

SU1599864A1 |

| Устройство для сопряжения процессоров | 1990 |

|

SU1807495A1 |

| Устройство для обнаружения ошибок при передаче информации | 1988 |

|

SU1596333A1 |

| Устройство для сопряжения абонентов с каналом связи | 1987 |

|

SU1432537A1 |

| Устройство для сопряжения периферийного устройства с ЭВМ | 1988 |

|

SU1596339A1 |

| Устройство для сопряжения электронной вычислительной машины с общей шиной | 1983 |

|

SU1144112A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1725223A1 |

| СИСТЕМА КОММУТАЦИИ ПРОЦЕССОРОВ | 1991 |

|

RU2006931C1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании высоконадежных мультипроцессорных систем. Целью изобретения является повышение достоверности решения задач за счет обеспечения селективного контроля информации, передаваемой по системной магистрали. Цель достигается тем, что в процессор, состоящий из блока 7 микропроцессоров, дешифратора 3 адреса, таймера 4, контроллера 5 прерывания, блока 6 формирования резидентной магистрали, блока 8 формирования системной магистрали, локальной памяти 2, введен блок 1 контроля, состоящий из узла захвата, блока сравнения и узла управления. 4 ил.

Фаг.1

Изобретение относится к вычислительной технике и может быть использовано при создании высоконадежных мультипроцессорных систем.

Целью изобретения является повышение достоверности решения задач за счет обеспечения селективного контроля информации, передаваемой по системной магистрали.

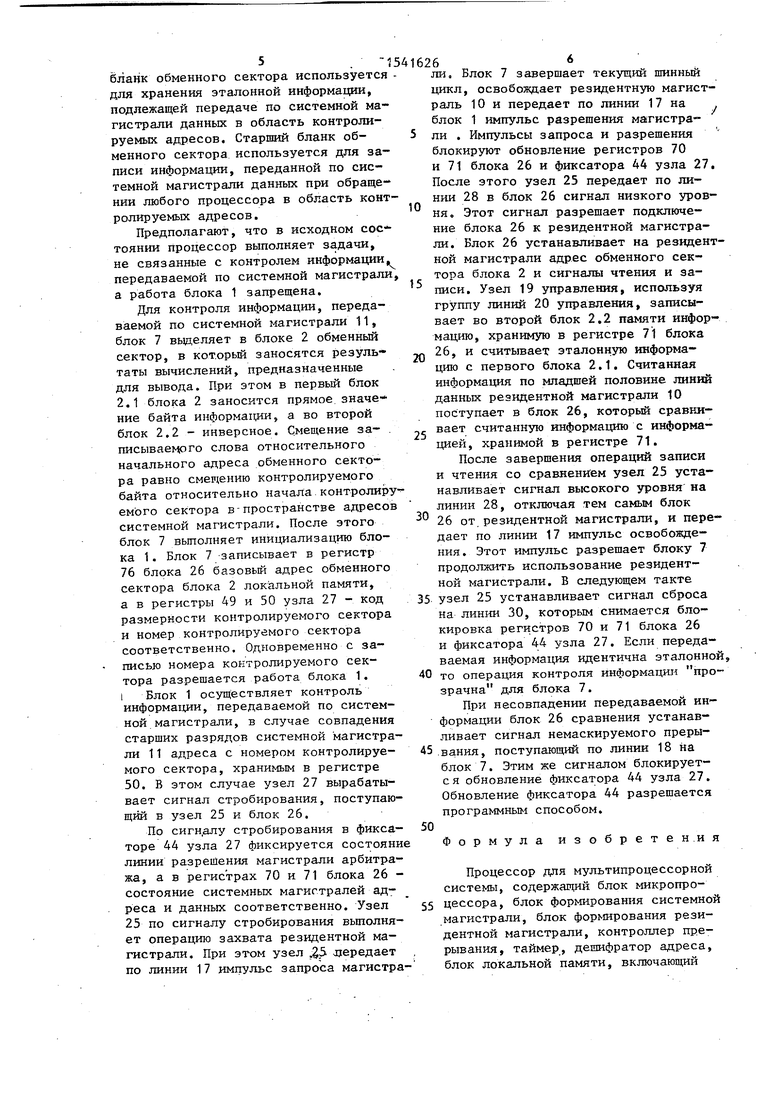

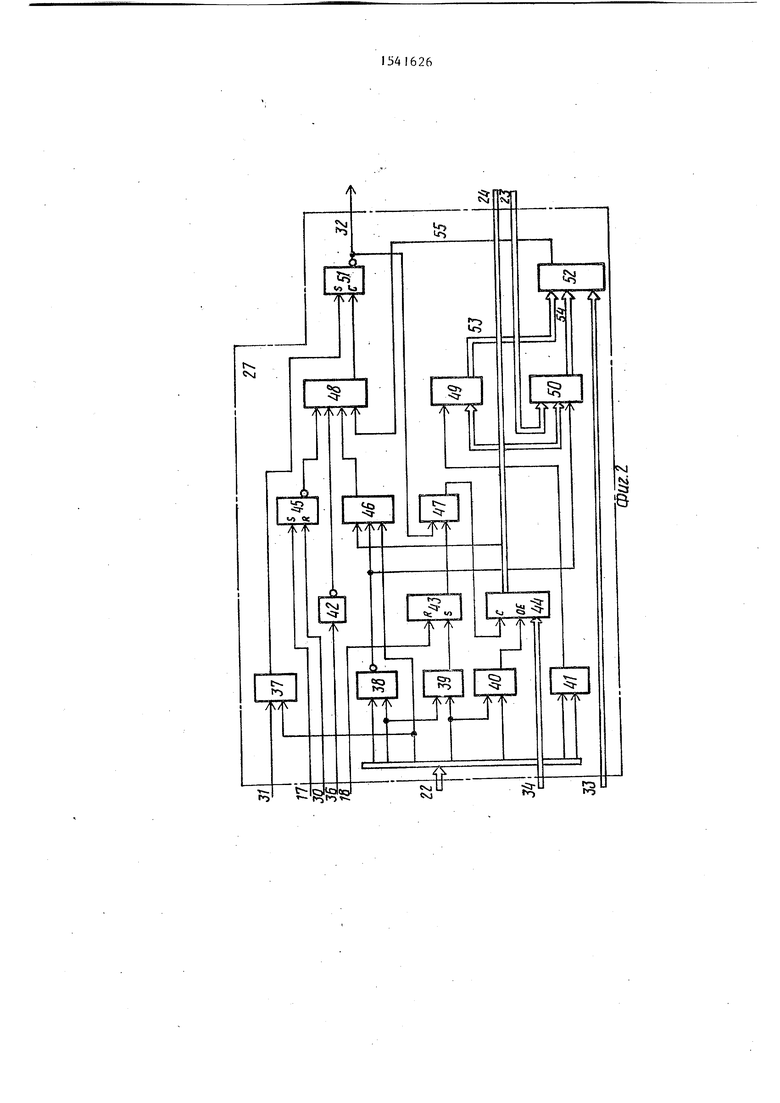

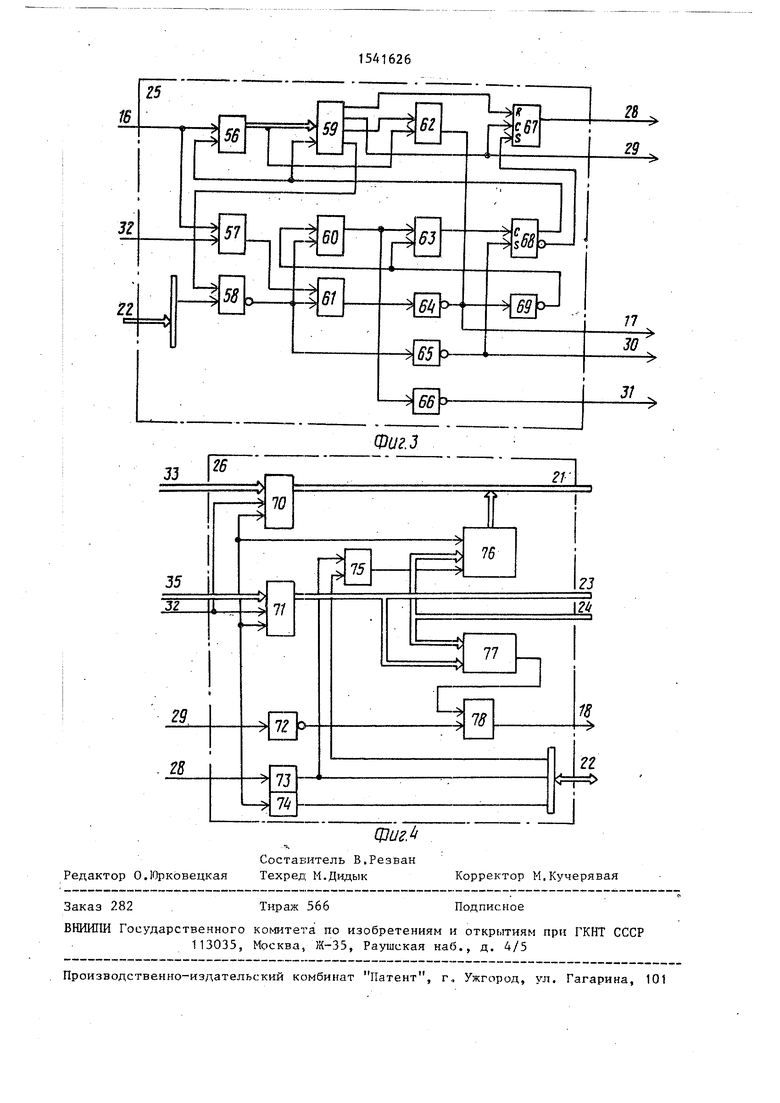

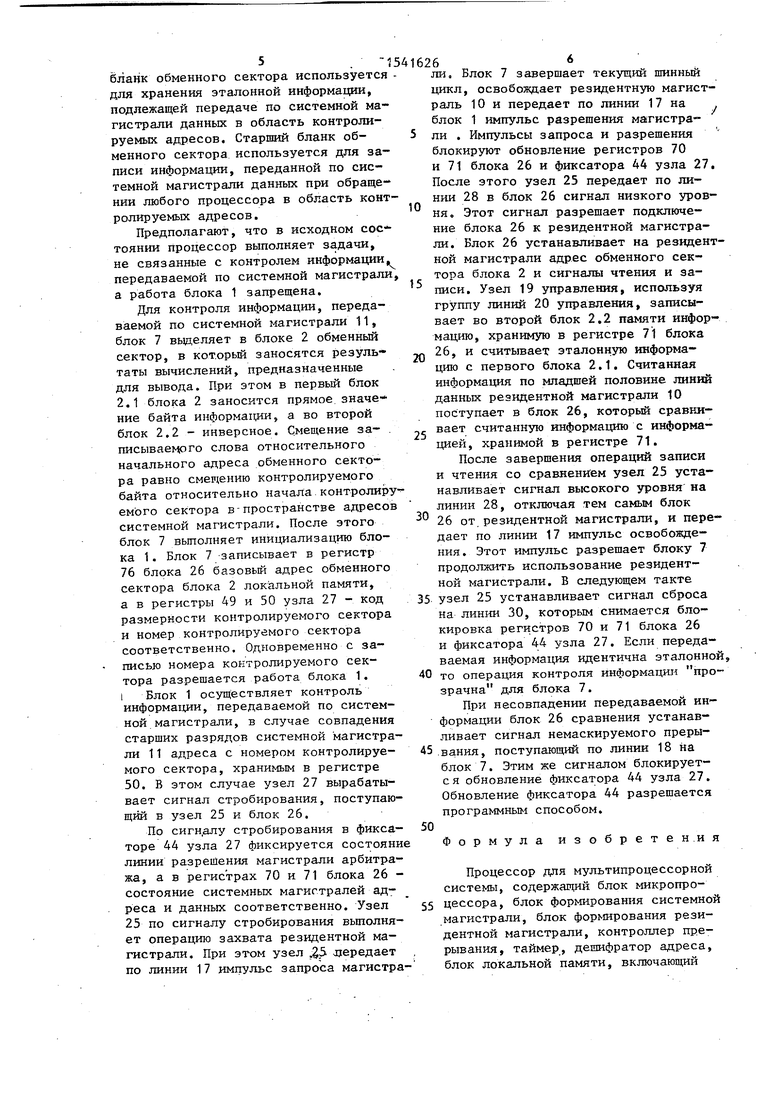

На фиг.1 представлена структурная схема процессора; на фиг„2 - пример реализации узла управления; на фиг.З пример реализации узла захвата; на фиг.4 --пример реализации узла сравнения .

Процессор для мультипроцессорной системы (фиг.1) содержит блок 1 контроля, блок 2 локальной памяти, дешифратор 3 адреса, таймер 4, конт- роллер 5 прерывания, блок 6 формирования резидентной магистрали, блок 7 микропроцессора, блок 8 формирования системной магистрали, локальную магистраль 9, резидентную магистраль 10, системную магистраль 11, линию 12 выбора, группу линий 13 запросов прерываний, втооую группу линий 14 запросов прерываний, линию 15 прерывания, линию 16 синхронизации, линию 17 запроса/разрешения резидентной магистрали и линию 18 немаскируемого прерывания.

Блок 2 локальной памяти содержит узел 19 управления, группу линий 20 управления локальной памятью, первый 2.1 и второй 2.2 блоки оперативной памяти.

Резидентная магистраль 10 содержит группу линий 21 адреса, группу линий 22 управления, первую 23 и вторую 24 группы линий данных.

Блок 1 контроля содержит узел 25 захвата, блок 26 сравнения, узел 27 управления, линию 28 включения, линию 29 проверки, линию 30 сброса, линию 31 подготовки и линию 32 строби рования.

Системная магистраль 11 содержит группу линчи 33 адреса, группу линий 34 арбитража, группу пиний 35 данных и линию 36 вывода.

Узел 27 управления (фиг,2) содержит элемент 2И 37, элемент 2ИПИ-НЕ 385 элементы 2ИЛИ 39 и 40, элемент 2ИЛИ-НЕ 41, элемент НЕ 42, триггер 43, фиксатор 44 состояния линий разрешения системной магистрали, триггеры 45 и 46, элемент 2И 47, этсмент

-

10

15

20

25

5416264

4И 48, регистры 49 и 50, триггер 51, узел 52 сравнения, линии 53 управления, линии 54 данных и линию 55 сравнения.

Узел 25 захвата (фиг.З) содержит счетчик 56, элемент 2И 57, элемент 2И-НЕ 58, дешифратор 59, счетчики 60 и 61, элемент 2ИЛИ 62, элемент 2И 63, элементы НЕ 64-66, триггеры 67 и 68 и элемент НЕ 69.

Блок 26 сравнения (фиг.4) содержит регистры 70 и 71, элемент НЕ 72, элементы И 73 и 74, элемент 2ИЛИ 75, регистр 76, узел 77 сравнения и элемент 2И 78.

Блок контроля предназначен для селективного контроля информации, передаваемой по системной магистрали. Селективность контроля обеспечивается делением пространства, адресуемого по системной магистрали, на группу селекторов. Старшие разряды системной магистрали адреса интерпретируются при этом как номер сектора, а младшие разряды - как смещение в секторе. Блок 1 контролирует передачу информации по адресам, старшие разряды которых совпадают с выбранным номером селектора. Номер контрочируемого сектора устанавливается программным способом. Контроль информации, передаваемой по системной магистрали, основан на записи в блок 2 локальной памяти эталонной информации, программировании блока 1 на слежение за программируемым пространством адресов и сравнении передаваемой информации с эталонной. При этом блок 1 использует 16- разрядную резидентную магистраль данных и контролирует передачи по 8- разряцной младшей половине системной магистрали данных. С этой целью в блоке 2 локальной памяти выделяется обменный сектор, доступ к которому имеет как блок 7, так и блок 1. Размерность обменного сектора равна удвоенной размерности контролируемого пространства адресов. Начало обменного сектора может быть размещено по 50 адресам, кратным длине сектора. Младшая часть (четные адреса) и старшая часть (нечетные адреса) адресного пространства, ограниченного обменным сектором, являются точными копиями 55 контролируемого адресно о пространства. Каждому бай-Tv контролируемого адресного пространств соответствует в обменном секторе сюво. Младший

30

35

40

45

бланк обменного сектора используется для хранения эталонной информации, подлежащей передаче по системной магистрали данных в область контролируемых адресов. Старший бланк обменного сектора используется для записи информации, переданной по системной магистрали данных при обращении любого процессора в область контролируемых адресов.

Предполагают, что в исходном сое- тоянии процессор выполняет задачи, не связанные с контролем информации, передаваемой по системной магистрали а работа блока 1 запрещена.

Для контроля информации, передаваемой по системной магистрали 11, блок 7 выделяет в блоке 2 обменный сектор, в который заносятся результаты вычислений, предназначенные для вывода. При этом в первый блок 2.1 блока 2 заносится прямое значе- ние байта информации, а во второй блок 2.2 - инверсное. Смещение записываемого слова относительного начального адреса обменного сектора равно смещению контролируемого байта относительно начала контролируемого сектора в-пространстве адресов системной магистрали. После этого блок 7 выполняет инициализацию блока 1. Блок 7 записывает в регистр 76 блока 26 базовый адрес обменного сектора блока 2 локальной памяти, а в регистры 49 и 50 узла 27 - код размерности контролируемого сектора и номер контролируемого сектора соответственно. Одновременно с записью номера контролируемого сектора разрешается работа блока 1. I Блок 1 осуществляет контроль информации, передаваемой по системной магистрали, в случае совпадения старших разрядов системной магистрали 11 адреса с номером контролируемого сектора, хранимым в регистре 50. В этом случае узел 27 вырабатывает сигнал стробирования, поступающий в узел 25 и блок 26.

По сигн.алу стробирования в фиксаторе 44 узла 27 фиксируется состояни линии разрешения магистрали арбитража, а в регистрах 70 и 71 блока 26 - состояние системных магистралей адреса и данных соответственно. Узел 25 по сигналу стробирования выполняет операцию захвата резидентной магистрали. При этом узел .2JJ лередает по линии 17 импульс запроса магистра ,

е541626

/

10

15

20

25

ли. Блок 7 завершает текущий шинный цикл, освобождает резидентную магистраль 10 и передает по линии 17 на блок 1 импульс разрешения магистрали . Импульсы запроса и разрешения блокируют обновление регистров 70 и 71 блока 26 и фиксатора 44 узла 27. После этого узел 25 передает по линии 28 в блок 26 сигнал низкого уровня. Этот сигнал разрешает подключение блока 26 к резидентной магистрали. Блок 26 устанавливает на резидентной магистрали адрес обменного сектора блока 2 и сигналы чтения и записи. Узел 19 управления, используя группу линий 20 управления, записывает во второй блок 2.2 памяти информацию, хранимую в регистре 71 блока 26, и считывает эталонную информацию с первого блока 2.1. Считанная информация по младшей половине линий данных резидентной магистрали 10 поступает в блок 26, который сравнивает считанную информацию с информацией, хранимой в регистре 71.

После завершения операций записи и чтения со сравнением узел 25 устанавливает сигнал высокого уровня на линии 28, отключая тем самым блок 26 от резидентной магистрали, и передает по линии 17 импульс освобождения . Этот импульс разрешает блоку 7 продолжить использование резидентной магистрали. В следующем такте

35 узел 25 устанавливает сигнал сброса на линии 30, которым снимается блокировка регистров 70 и 71 блока 26 и фиксатора 44 узла 27. Если передаваемая информация идентична эталонной,

40 то операция контроля информации прозрачна для блока 7.

При несовпадении передаваемой информации блок 26 сравнения устанавливает сигнал немаскируемого преры45 вания, поступающий по линии 18 на блок 7. Этим же сигналом блокирует- с я обновление фиксатора 44 узла 27. Обновление фиксатора 44 разрешается программным способом.

50

Формула изобретения

Процессор для мультипроцессорной системы, содержащий блок микропро- 55 цессора, блок формирования системной магистрали, блок формирования резидентной магистрали, контроллер прерывания, таймер, дешифратор адреса, блок локальной памяти, включающий

30

7

узел управления и два блока памяти, причем первые входы-выходы адреса даных и входы-выходы управления блока микропроцессора через локальную магистраль соединены с одноименными первыми входами блока формирования системной магистрали и блока формирования резидентной магистрали, вход адреса и вход управления дешифратора адреса соединены с одноименными вторыми входами-выходами формирователя резидентной магистрали, входы-выходы адреса данных и входы-выходы управления контроллера прерывания, таймера и локальной памяти через резидентную магистраль соединена с одноименными вторыми входами формирователя резидентной магистрали, выход запросов прерывания таймера соединен с одноименным первым входом контроллера прерываний, выход прерывания которого соединен с одноименным входом блока микропроцессора, отличающийся тем, что, с цель повышения достоверности решения задач за счет обеспечения селективного контроля информации, передаваемой по системной магистрали, в него включен блок контроля, содержащий узел захвата, блок сравнения и узел управления, выход стробирования которого соединен с одноименными входами блок сравнения и узла захвата, выходы вклчения и проверки которого соединены с одноименными входами блока сравнения, выход немаскируемого прерывания которого соединен с одноименными входами узла управления блока контроля и блока микропроцессора, выход синхронизации которого соединен с одноименным входом узла захвата, вход

8

to

15

0

5

0

5

0

выход запроса разрешения которого соединен с одноименными входами-выходами блока микропроцессора и узла управления блока контроля, вторые входы-выходы адреса блока формирования системной магистрали через системную магистраль соединены с одноименными первыми входами-выходами блока сравнения и узла управления блока контроля и являются входами-выходами адреса процессора, вторые входы-выходы данных блока формирования системной магистрали соединены через системную магистраль с одноименными первыми входами-выходами блока сравнения и являются входами-выходами данных процессора, входы-выходы запроса прерывания блока формирования системной i магистрали через системную магистраль

соединены с одноименными вторыми входами контроллера прерываний и являются входами-выходами запроса прерывания процессора, входы-выходы арбитража и вывода блока формирования магистрали через системную магистраль соединены с одноименными входами-выходами узла управления блока контроля и являются входами-выходами арбитража и вывода процессора, вторые входы-выходы адреса, входы-выходы данных и входы-выходы управления узла управления блока контроля, вторые входы- выходы адреса данных и входы-выходы управления блока сравнения, входы- выходы управления узла захвата соединены через резидентную магистраль с одноименными входами-выходами блока локальной памяти и одноименными вторыми входами-выходами блока формирования резидентной магистрали.

чС гм

чО

г г

Составитель В.Резван Редактор О.Юрковецкая Техред М.Дидык

Заказ 282

Тираж 566

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г, Ужгород, ул. Гагарина, 101

фиг4

Корректор М.Кучерявая

Подписное

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Коммутатор без переговорно-вызывных ключей с применением автоматических искателей | 1924 |

|

SU1810A1 |

| Прибор для передачи импульсов тока | 1924 |

|

SU2204A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-02-07—Публикация

1988-05-03—Подача