тельный преобразователь кода, сигналь- j$ стартовый выход которого подключен к

ный выход которого соединен с входом первого блока задержки, выход которого соединен с установочным входом триггера, тактовый вход которого подключен к первому выходу делителя частоты, фазирующий вход которого подключен к выходу первого блока совпадения, первый вход которого соединен с выходом триггера, первыми входами первых элементов И, первым входом второго элемента И и блокирующим входом делителя частоты, второй выход которого соединен со стирающим входом наборного блока, информационные выходы которого соединены с вторыми входами соответствующих первых элементов И, выходы которых подключены к соответствующим информационным входам параллельно-последовательного преобразователя кода, первый стартовый выход наборного бдока соединен с вторым входом второго элемента И, при этом информационные входы наборного блока являются информационными входами устройства, стартовым входом которого является первый стартовый вход наборного блока, информационным

20

первому входу.второго блока совпадения, выход которого соединен с стартовым входом параллельно-последовательного преобразователя кода, информационные выходы которого подклю- чены к вторым информационным входам блока сравнения, первые информационные входы которого подключены к соответствующим -информационным выходам 25 наборного блока, первый выход блока сравнения соединен с вторым входом четвертого блока совпадения, выход которого подключел к входу ошибки параллельно-последовательного преобразователя- кода, установочный вход которого соединен с вторым входом . первого блока совпадения и выходом третьего блока совпадения, второй вход которого подключен к второму выходу блока сравнения, третий выход делителя частоты подключен к второму входу второго блока совпадения, выход второго элемента И соединен с входом второго блока задержки, при этом выход четвертого блока совпадения является выходом сигнала ошибки устройства.

30

35

40

0

первому входу.второго блока совпадения, выход которого соединен с стартовым входом параллельно-последовательного преобразователя кода, информационные выходы которого подклю- . чены к вторым информационным входам блока сравнения, первые информационные входы которого подключены к соответствующим -информационным выходам 5 наборного блока, первый выход блока сравнения соединен с вторым входом четвертого блока совпадения, выход которого подключел к входу ошибки параллельно-последовательного преобразователя- кода, установочный вход которого соединен с вторым входом . первого блока совпадения и выходом третьего блока совпадения, второй вход которого подключен к второму выходу блока сравнения, третий выход делителя частоты подключен к второму входу второго блока совпадения, выход второго элемента И соединен с входом второго блока задержки, при этом выход четвертого блока совпадения является выходом сигнала ошибки устройства.

0

5

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Стартстопное передающее устройство | 1976 |

|

SU566387A1 |

| Устройство для испытаний датчиков давления | 1983 |

|

SU1129624A1 |

| Приемник телеграфного аппарата с автоконтролером | 1979 |

|

SU900465A2 |

| Цифровой электропривод постоянного тока | 1981 |

|

SU1003282A1 |

| УСТРОЙСТВО ДЛЯ ОБМЕНА ИНФОРМАЦИЕЙ | 1998 |

|

RU2130642C1 |

| Устройство для сопряжения ЭВМ с абонентом | 1986 |

|

SU1334154A1 |

| Устройство для счета штучных изделий,перемещаемых конвейером | 1986 |

|

SU1464184A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU1001098A1 |

| Устройство для моделирования деятельности человека-оператора | 1984 |

|

SU1221661A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

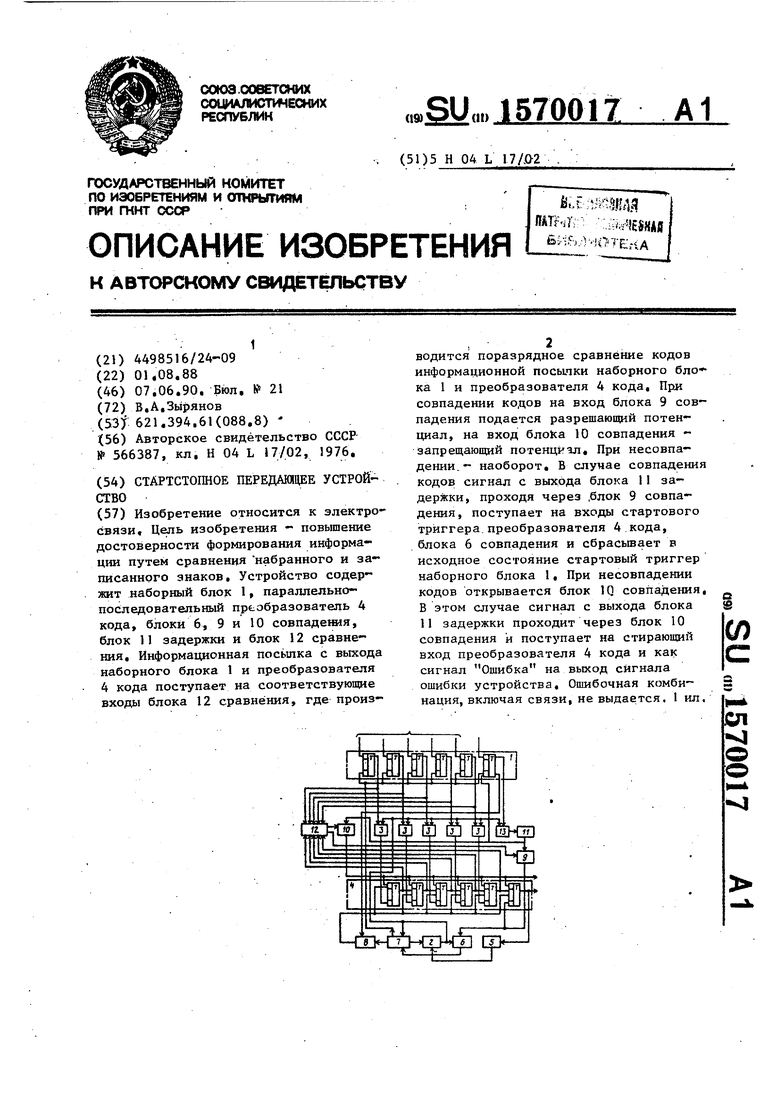

Изобретение относится к электросвязи. Цель изобретения - повышение достоверности формирования информации путем сравнения набранного и записанного знаков. Устройство содержит наборный блок 1, параллельно-последовательный преобразователь 4 кода, блоки 6, 9 и 10 совпадения, блок 11 задержки и блок 12 сравнения. Информационная посылка с выхода набборного блока 1 и преобразователя 4 кода поступает на соответствующие входы блока 12 сравнения, где производится поразрядное сравнение кодов информационной посылки наборного блока 1 и преобразователя 4 кода. При совпадении кодов на вход блока 9 совпадения подается разрешающий потенциал, на вход блока 10 совпадения - запрещающий потенциал. При несовпадении - наоборот. В случае совпадения кодов сигнал с выхода блока 11 задержки, проходя через блок 9 совпадения, поступает на входы стартового триггера преобразователя 4 кода, блока 6 совпадения и сбрасывает в исходное состояние стартовый триггер наборного блока 1. При несовпадении кодов открывается блок 10 совпадения. В этом случае сигнал с выхода блока 11 задержки проходит через блок 10 совпадения и поступает на стирающий вход преобразователя 4 кода и как сигнал Ошибка на выход сигнала ошибки устройства. Ошибочная комбинация, включая связи, не выдается. 1 ил.

Авторы

Даты

1990-06-07—Публикация

1988-08-01—Подача