Изобретение относится к вычислиельной технике и предназначено для спользования в решающих модулях ифровых интегрирующих структур (ПДС) одноразрядными приращениями.

Цель изобретения - расширение ункциональных возможностей за счет беспечения возможности.одновременного суммирования нескольких одноразрядных приращений с разными порядками.

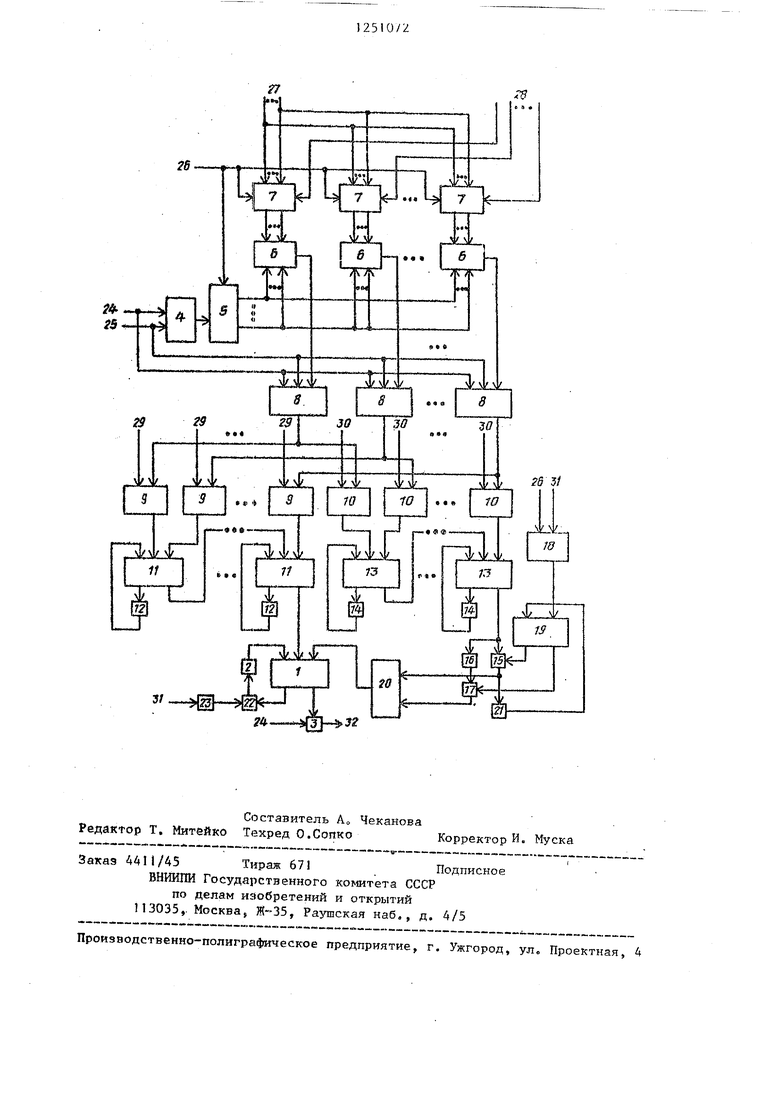

На чертеже представлена.функциональная схема устройства для суммирования одноразрядных приращений.

Устройство для суммирования одноразрядных приращений содержит результирующий одноразрядный сумматор 1, первьй элемент задержки 2, первый элемент И 3, второй элемент И 4, счетчик 5 по модулю К, группу блоков сравнения 6, группу регистров 7, группу управляюпдах элементов И 8j группу элементов И 9 положительных приращений, группу элементов И 10 отрицательргых приращений, первую группу одноразрядных сумматоров I1, первую группу элементов задержки 12, вторую груггпу одноразрядных сумматоров 13, вторую группу элементов задержки 14, третий элемент И 15, первый элемент ИЕ 16, четвертый элемент И 17, первый элемент ЕПИ 8, триггер 9, второй элемент ИЛИ 20, второй элемент задержки 21, пятый элемент И 22, второй элемент НЕ 23, вход 24 разрешения работы устройства, тактирующий вход 25 устройства, вход 26 сброса устройства, входы 27 начальных данных, входы 28 синхронизации данных, группу входов 29 положительных приращений, группу входов 30 отрицательных приращений, вход 31 конца итерации устройства, выход 32 результата суммирования устройства.

Устройство для суммирования одноразрядных приращений работает еле-, дующим образом.

Перед началом работы производится установка устройства для сумми- роваш-гя одноразрядных приращений в исходное состояние, при этом соответствующий сигнал сброса через вход 26 устройства поступает на вход установки нуля счетчика 5 по модулю К, на входы установки нуля регистров 7 группы, на nepBbrfr вход первого элемента ИЛИ 18, а через пос

510722

ледний - на вход установки нуля триггера 19„ В результате счетчик 5, регистры 7 группы и триггер 19 устанавливаются в нулевое состояние, 5 Затем производится ввод масштабных коэффициентов, рассчитанньгх при начальном масштабировании задачи для каждого входного приращения в соответствии с масщтабными соотно- fO .шениями интегрирующих мащиН по формуле

HIj n-m +mdyj ,

где HIj - значение масштабного коэффициента для j-ro входно- 15го приращения, определяющее номер разряда подынтегральной функции со стороны младших разрядов, с которым суммируется j-e 20одноразрядное входное приращение ;

п - количество числовых разрядов в регистре подынтегральной функции (без зна- ковых разрядов);

m - показатель степени двоичного порядка значения подынтегральной функции; ffldyj - показатель степени двоич- 30ного порядка j-ro входного

приращения.

При этом значения масштабных коэффициентов HI у поступают параллельными кодами через группу входов 27 35 устройства на информационные входы регистров 7 группы и по импульсам синхронизации данных, поступающим одновременно со значениями масштабных коэффициентов HIj- через соответ- 40 ствующие входы группы входов 28 последовательно на входы управления записью Соответствующих регистров 7 группы, заносятся в эти регистры 7 группы (количество регистров 7 равно 45 числу одновременно суммируемых входных приращений и на практике рав- но 3 - 5).

По сигналу разрешения работы, поступающему через.вход 24, открывается второй элемент И 4, и на суммирующий вход счетчика 5 по модулю К начинают поступать через открытый элемент И 4 с входа 25 тактирующие импульсы, изменяющие состояние счет- чика 5 по модулю К от О до (К-1), где К - общее количество разрядов с регистра подынтегральной функции, включающее числовые разряды (и) и

3

знаковые разряды (и ). При совпадении значения какого-либо масштабного коэффициента HJj , записанного в соответствующем регистре 7, со значением счетчика 5 по модулю К (счет ,чик срабатывает по заднему фронту входных тактирующих импульсов) на выходе соответствующего блока сравнения 6 группы появляется единичный сигнал длительностью в один такт, который открывает соответствующий трухвходовый элемент И 8 группы (на вторые входы элементов .И 8 группы поступает с входа 24 сигнал разрешения работы), и тактирующий импульс , с входа 25 устройства проходит через элемент И 8 группы и поступает на первый вход соответствующего элемента И 9 группы элементов И положитель ных приращений и на пурвый вход со- ответствующего элемента И 10 группы элементов И отрицательных приращений в качестве масштабного импульса j-ro одноразрядного входного приращения, соответствующего во времени (n-my+ )-му разряду подынтегральной функции. На вторые входы элзмен- тов И 9 группы элементов И положительных приращений и элементов И 10 группы элементов И отрицательных приращений поступают импульсы с входов 29 и 30 устройства, представленные в тернарной системе кодиро- . вания, т,е. принимающие значения +1, О и -1 (положительные или отрицательные значения входньпс одноразрядных приращений соответст- венно). В результате поступающими на , первые входы этих элементов rt 9 и И 10 масштабными импульсами, вы- рабатываемыми отдельно для каждого входного одноразрядного приращения, производится приведение положительных и отрицательных значений соот- ветствуюш 1х одноразрядных прираще- НИИ к масштабу подынтегральной функции решающего модуля и преобразование их в последовательный код. Когда счетчик 5 по модулю К достигает значения (К-1), то вырабатьгеаются-все масштабные сигналы для всех одноразрядных входных приращений в первом цикле вычислений (на первом шаге решения) и в следующем такте Счетчик 5 по модулю К переходит в состояние, равное нулю, и устройство начинает выработку масштабных сигналов для входных приращений следующего цикла

072 -4

вычислений, который для каждого входного п1)иращения производится аналогично первому циклу вычислений затем производится выработка масштабных сигналов для третьего цикла вычисления и т.д.

Суммирование входных одноразрядных приращений, представленных в тернарной системе кодирования, осуществляется раздельно для их положительных и отрицательных значений по двум идентичным каналам. Положительные значения одноразрядных при- раше.иий поступают с входов 29 устройства на вторые входы соответствующих з П ементов И 9 группы элементов И положительных приращений. Физически одноразрядные приращения в тернарной системе кодирования, т.е. принимающие значения +1, О и -1, представляют собой потенциалы, соответствующие +1 или -1, длительностью в одну итерацию или К тактов, где К - длина слова подынтегральной функции, включая знаковые и числовые разряды. Если положительное значение i-ro ВХОДНОГО одноразрядного приращения равно единице, то на выходе i-ro элемента И 9 группы элементов И положительных приращений в момент времени, соответствующий масштабному импульсу i-ro одноразрядного приращения, появляется импульс длиной в один такт, т.е. положительное значение i-ro одноразрядного приращения подынтегральной функциипри-. водится к масштабу- подынтегральной функции и переведено в последовательный код. Суммирование последовательных кодов положительных значений одноразрядных приращений осуществляется параллельно-последовательным сумматором, состоящим из одноразрядных сумматоров 1I первой группы и элементов задержки 12 первой группы. С выхода суммы последнего (m-l)-ro одноразрядного сумматора 11 первой группы получившийся последовательный код суммы положительных значений входных одноразрядных приращений поступает на второй вход результи- рующего одноразрядного сумматора . Сумма отрицательных значений входных одноразрядных приращений образуется аналогично с помощью элементов И 10, одноразрядных сумматоров 13 второй группы и элементов задержки 14 второй группы. Для формирования окончательной суммы положительных и отри - дательных значений одноразрядных приращений необходимо пряной последовательный код сз ьшы отрицательных значений одноразрядных приращений преобразовать в дополнительный код, что осуществляется следующим образом. Первая единица в последовательном коде суммы отрицательмых значений одноразрядных приращений, поступающая с выхода сум№, последнего (m-l)- го одноразрядного сумматора 13 второй группы, пройдя через открытый элемент И 15 (на второй вход этого элемента поступает единичный сигнал с нулевого выхода триггера 19, установленного в н шевое состояние при подготовке устройства к работе сиг-налом сброса с входа 26, а в процессе работы в конце каждой итерации - сигналом конца итерации,, совпадающим по времени с последним тактовым импульсом итерации и поступающим, с входа: 31 устройства через элемент ШШ 18 f и поступает изменения через элемент ИЛИ 20 на третий вход результирующего одноразрядного сумматора 1 , а задержавшись на один такт на элементе задержки 21 эта единица поступает на единичный вход триггера 19 и перебрасывает его в единичное состояние, В результате триггер 19 закрывает элемент И 15 и открывает элемент И 17, н весь оставшийся последовательный код суммы отрицательных значений однораз- рядных приращений поступает через злем.ент НЕ 16, через открытый эле -- мент И 17 и через элемент ИЖ 20 в инверсном виде на третий вход результирующего одноразрядного сумма- тора I. Образованный таким образом дополнительный код суммам отрицательных значений одноразряд.шых приращений,, поступающих с выхода элемента ИЛИ 20, просуммируется на сумматоре I с суммой положительных значений одноразрядных приращений, поступающей с выхода последнего (m-l)-ro одноразрядного сзп мато- ра 11 первой группы, и общая сумма одноразрядных приращений с выхода суммы результирующего одноразрядного сумматора 1 по потенциалу разрешения работы, поступающему с входа 24 устройства на второй вход пер- в ого элемента И 3, поступает на

выход 32 результата суммирования устройства. Сигнал конца итерации, поступающий с входа 31 устройства

через элемент НЕ 28 на вход элемента И 22, запрещает формирование переноса из старщего знакового разряда, сформированного-на предыдущей итератдаи, в младший числовой разряд

следующей итерации, а включенный в цепь переноса слгмматора 1 однотакт- ный элемент задержки 2 служит для образования поразрядного переноса при cyм « poвaнии суммы положительных значений одноразрядных приращений с суммой отрицательных значений этих приращений.

Формула изобретения

5

Устройство для суммирования одноразрядных приращений, содержащее два элемента И, группу элементов И положительных приращений, группу

5 элементов И отрицательных приращений, первую группу одноразрядных сумматоров, вторую группу одноразрядных Сумматоров, результирующий одноразрядный сумматор, элемент за0 держки, элемент НЕ, причем первый вход результирующего одноразрядного сумматора соединен с выходом элемента задержки, а выход суммы результирующего одноразрядного сумматора соединен с первым входом первого элемента И, второй вход которого соединен с входом разрешения работы устройства, выход первого элемента И соединен с выходом результата

д устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения .возможности одновременного суммирования нескольких одно„ разрядных приращений с разными порядками, оно содержит счетчик по модулю К, группу регистров, -группу блоков сравнения, группу управляющих элементов И, две группы элементов

задержки, второй элемент НЕ, третий j4eT - вертый и пятый элементыИ,два элемен та ИЛИ, триггер и второй элемент задержки, причем выход второго элемен- .та И соединен со счетным входом счет- чика по модулю к, выходы которого соединены с первыми входами блоков сравнения группы, вторые входы которых соединены с выходами всех регистров группы, выходы блоков сравнения группы соединены соответственно с первыми входами управляющих элементов И группы, выходы которых соединены с первыми входами элементов И положительных приращений группы и первыми входами элементов И отрицательных приращений группы, выход - го элемента И положительных приращений группы (j-2, 3,..., га, где га - число входных одноразрядных приращений) , соединен с первым входом (j-l) го одноразрядного сумматора первой группы, выход переноса j-ro одноразрядного сумматора первой группы соединен через J-й элемент задержки пер вой группы со вторым входом этого же сумматора, выход суммы i-ro (, 2,о.„, m-2) одноразрядного сумматора первой группы соединен с третьим входом (1+1)-го одноразрядного сумматора первой группы, третий вход первого одноразрядного сумматора первой группы соединен с выходом первого- элемента И положительных приращений группы, выход суммы последнего (m-l)-ro одноразрядного сумматора первой группы соединен с вторым входом результирующего одноразрядного сумматора, выход j-ro элемента И отрицательных приращений группы (j 2, 3,..о, га) соединен с первым входом (j-l)-ro одноразрядного сумматора второй группы, выход переноса j-ro одноразрядного сумматора второй группы соединен через j-й элемент задержки второй группы с вторым входом этого же сумматора, выход суммы i-ro одноразрядного сумматора второй группы (, 2,.о о, m-2) соединен с третьим входом (i+l)-ro одноразрядного сумматора второй группы, третий вход первого одноразрядного сумматора второй группы соединен с выходом первого элемента И отрицательных приращений группы, выход суммы пос леднего (ra-l)-ro одноразрядного сумматора второй группы соединен с первым входом третьего элемента И и через первый элемент НЕ соединен.с

510728

первым входом четвертого элемента И, выход первсто элемента ИЛИ соединен с входом установки, в О триггера, прямой выход которого соединен с 5 вторым входом четвертого элемента И, а инверсный выход триггера соединен с входом третьего элемента И, выход четвертого элемента И соединен с первым входом второго элемента ИЛИ, 10 второй вход которого соединен с выходом третьего элемента И и с входом второго элемента задержки, выход которого соединен с входом установки в 1 триггера, выход второго эле15 мента ИЛИ соединен с третьим входом результирующего одноразрядного сумматора, выход переноса которого соединен с первым входом пятого элемента И, второй вход которого соединен

20 с выходом второго элемента НЕ, а выход пятого элемента И соединен с входом первого элемента задержки, первый вход второго элемента- И и вторые входы управляющих элементов И

5 группы соединены с входом разрешения работы устройства, а второй вход Iвторого элемента И и третьи входы управляющих элементов И группы соединены с тактирующим входом устрой0 ства, вход установки нуля счетчика по модулю К, вход установки нуля регистров группы и первый вход первого элемента ИЛИ соединены с входом сброса устройства, информационные входы .

, регистров группы соединены с входами начальных данных устройства, входы синхронизации регистров группы соединены с входами синхронизации данных устройства, вторые входы i-ro .

Q элемента И положительных приращений группы и i-ro элемента И отрицательных приращений, группы соединены соответственно с входами из групп входов положительных и отрицательных

5 значений одноразрядных приращений устройства, второй вход первого элемента ИЛИ и вход второго элемента НЕ соединены с входом конца итерации устройства.

0

2S

| название | год | авторы | номер документа |

|---|---|---|---|

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| Решающий блок цифровой интегрирующей структуры | 1983 |

|

SU1104514A1 |

| Интегро-вычислительная структура | 1979 |

|

SU857987A1 |

| Интегрирующая вычислительная структура | 1981 |

|

SU1257672A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU960842A1 |

| Устройство масштабирования цифрового дифференциального анализатора | 1983 |

|

SU1156069A1 |

| Устройство для моделирования нейрона | 1979 |

|

SU883927A2 |

Изобретение предназначено для использования в решаюпщх модулях цифровых интегрирующих структур с одноразрядными приращениями. Целью изобретения является расширение функциональных возможностей за счет обеспечения одновременного суммирования нескольких одноразрядных приращений с-разными порядками без предварительного выравнивания порядков, что значительно упрощает программирование задачи и в 1,5-2 раза сокращает время начального масштабирования задачи, поскольку устраняется необходимость в выравнивании порядков входных одноразрядных приращений и тем самым в проведении расчетов масштабных коэффициентов при начальном масштабировании. Поставленная цель достигается введением счетчика по модулю К, группы регистров, группы блоков сравнения, группы трехвходо- вых элементов И., двух групп элементов задержки, второго элемента НЕ, третьего, четвертого и пятого элементов И, двух элементов ИЛИ, триггера и второго элемента задержки. 1 ил. i (Л to ел sl ю

| Авторское свидетельство СССР № 1015571, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| НАГРЕВАТЕЛЬНАЯ ПЕЧЬ | 0 |

|

SU309218A1 |

| Кн | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Домовый номерной фонарь, служащий одновременно для указания названия улицы и номера дома и для освещения прилежащего участка улицы | 1917 |

|

SU93A1 |

Авторы

Даты

1986-08-15—Публикация

1985-01-04—Подача