Изобретение относится к вычислительной технике и может быть использовано в процессорах ЭВМ и цифровым устройствам автоматики,

Цель изобретения - повышение быстродействия накапливающего сумматора.

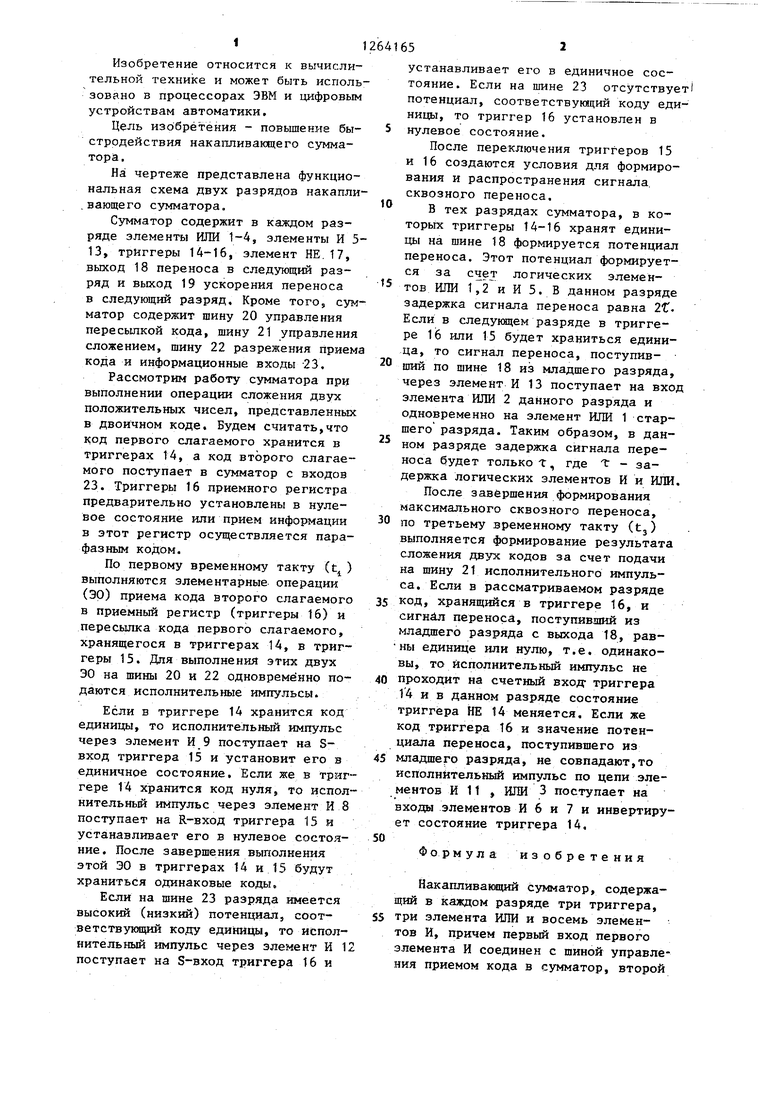

На чертеже представлена функциональная схема двух разрядов накапливающего сумматора.

Сумматор содержит в каждом разряде злементы ИЛИ 1-4, злементы И 513, триггеры 14-16, злемент НЕ. 17, выход 18 переноса в следующий разряд и выход 19 ускорения переноса в следующий разряд. Кроме того, сумматор содержит шину 20 управления пересылкой кода, шину 21 управления сложением, шину 22 разрежения приема кода и информационные входы 23.

Рассмотрим работу сумматора при выполнении операции сложения двух положительных чисел, представленных в двоичном коде. Будем считать,что код первого слагаемого хранится в триггерах 14, а код второго слагаемого поступает в сумматор с входов 23. Триггеры 16 приемного регистра предварительно установлены в нулевое состояние или прием информации в этот регистр осуществляется парафазным кодом.

По первому временному такту (t ) выполняются злементарные операции (эр) приема кода второго слагаемого в приемный регистр (триггеры 16) и пересылка кода первого слагаемого, хранящегося в триггерах 14, в триггеры 15. Для выполнения этих двух ЭО на шины 20 и 22 одновременно подаются исполнительные импульсы.

Если в триггере 14 хранится код единицы, то исполнительный импульс через элемент И 9 поступает на Sвход триггера 15 и установит его в единичное состояние. Если же в триггере 14 хранится код нуля, то испол нительный импульс через элемент И 8 поступает на R-вход триггера 15 и устанавливает его в нулевое состояние. После завершения выполнения этой 30 в триггерах 14 и 15 будут храниться одинаковые коды.

Если на шине 23 разряда имеется высокий (низкий) потенциал, соответствукяций коду единицы, то исполнительный импульс через элемент И 12 поступает на S-вход триггера 16 и

устанавливает его в единичное состояние. Если на шине 23 отсутствует потенциал, соответствукхций коду единицы, то триггер 16 установлен в

нулевое состояние.

После переключения триггеров 15 и 16 создаются условия для формирования и распространения сигнала. cKBO3Ho.ro переноса.

В тех разрядах сумматора, в которых триггеры 14-16 хранят единицы на шине 18 формируется потенциал переноса. Этот потенциал формируется за счет логических злементов ИЛИ 1,2 и И 5. В данном разряде задержка сигнала переноса равна 2t. Если в следукщем разряде в триггере Ii6 или 15 будет храниться единица, то сигнал переноса, поступив шнй по шине 18 из младшего разряда, через элемент И 13 поступает на вход элемента ИЖ 2 данного разряда и одновременно на элемент ИЛИ 1 старшего разряда. Таким образом, в данном разряде задержка сигнала переноса будет только т, где t - задержка логических элементов И и ШШ,

После завершения формирования максимального сквозного переноса,

0 по третьему временному такту (tj) выполняется формирование результата сложения гуаугк кодов за счет подачи на шину 21 исполнительного импульса. Если в рассматриваемом разряде

5 код, хранящийся в триггере 16, и сигнал переноса, поступивший из младшего разряда с выхода 18, равиы единице или нулю, т.е. одинаковы, то исполнительный импульс не

0 проходит на счетный вход- триггера 14 ив данном разряде состояние триггера НЕ 14 меняется. Если же код триггера 16 и значение потенциала переноса, поступившего из

5 младшего разряда, не совпадают,то исполнительный импульс по цепи элементов И 11 , ИЛИ 3 поступает иа входы элементов И 6 и 7 и инвертирует состояние триггера 14,

Формула изобретения

Накапливающий сумматор, содержащий в каждом разряде три триггера, 5 три элемента ШШ и восемь элементов И, причем первый вход первого элемента И соединен с щиной управления приемом кода в сумматор, второй вход соединен с информационным входом данного разряда сумматора, а вы ход первого элемента И подключен к S-входу первого триггера, единичный выход которого соединен с первым входом первого элемента ШШ и с пер вым входом второго элемента И, второй вход которого соединен с шиной управления отношением сумматора, а выход второго элемента И подключен к первому входу второго элемента ИЛ второй вход которого соединен с выходом третьего элемента И, выход вт рого элемента ИЛИ соединен с первым входами четвертого и пятого элементов И, вторые входы которых соединены соответственно с одиночным и нулевым выходами второго триггера, R- и S-входы которого соединены с выходами соответственно шестого и седьмого элементов И, первые входы которых соединены с шиной управления пересылкой кода сумматора, а , вторые входы соединены соответствен но с нулевым и единичным выходами третьего триггера, R- и S-входы которого соединены с выходами соответственно четвертого и пятого элементов И, первый и второй входы третьего элемента ШШ подключены со ответственно к выходу переноса и к выходу ускорения переноса предыдуще го разряда сзгмматора, первый вход 654 третьего элемента И соединен с первым входом третьего элемента ИЛИ, выходы первого и третьего элементов ИЛИ подключены к соответствующим входам восьмогоэлемента И, выход которого соединен с выходом переноса данного раэряда сумматора, отличающийся тем, что, с целью повышения быстродействия, сумматор дополнительно содержит четвертый элемент ИЛИ, девятый элемент И и элемент НЕ, причем третий вход второго элемента И соединен с выходом элемента НЕ, вхед которого соединен с первым входом третьего элемента И, второй вход которого подключен к нулевому выходу первого триггера, а третий вход соединен с шиной управления сложением сумматора, второй вход первого элемента ШШ соединен с выходом ускорения переноса данного разряда и с выходом девятого элемента И, первый вход которого подключен к выходу четвертого элемента ИЛИ, второй вход девятого элемента И соединен с первым входом третьего элемента ИЛИ, третий вход которого соединен с первым входом четвертого элемента ИЛИ и с единичным входом второго триггера, второй вход четвертого элемента ИЛИ соединен с единичным выходом первого триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Накапливающий сумматор | 1985 |

|

SU1262479A1 |

| Накапливающий сумматор | 1982 |

|

SU1043638A1 |

| Двоичный накапливающий сумматор | 1983 |

|

SU1112363A1 |

| Накапливающий сумматор | 1987 |

|

SU1418701A1 |

| Арифметическое устройство | 1979 |

|

SU842794A1 |

| Двухтактный п-разрядный сумматор накапливающего типа | 1974 |

|

SU538365A1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2269153C2 |

| Арифметическое устройство | 1983 |

|

SU1239710A1 |

| Накапливающий сумматор | 1984 |

|

SU1176323A1 |

| Накапливающий сумматор | 1985 |

|

SU1291968A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в процессорах ЭВМ и устройствах цифровой автоматики. Цель изобретения - повышение быстродействия. Накапливающий сумматор в каждом разряде содержит три RS-триггера, девять элементов И, четгфв элемента ИЛИ и шины управления работой сумматора. 1 ил.

| Параллельный накапливающий сумматор | 1979 |

|

SU911517A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Двоичный накапливающий сумматор | 1983 |

|

SU1112363A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-15—Публикация

1985-01-07—Подача