Изобретение относится к технике передачи и приема информации, а именно к устройствам с подавлением помех в приемнике.

Цель изобретения - повышение помехоустойчивости при наличии внеполосных помех.

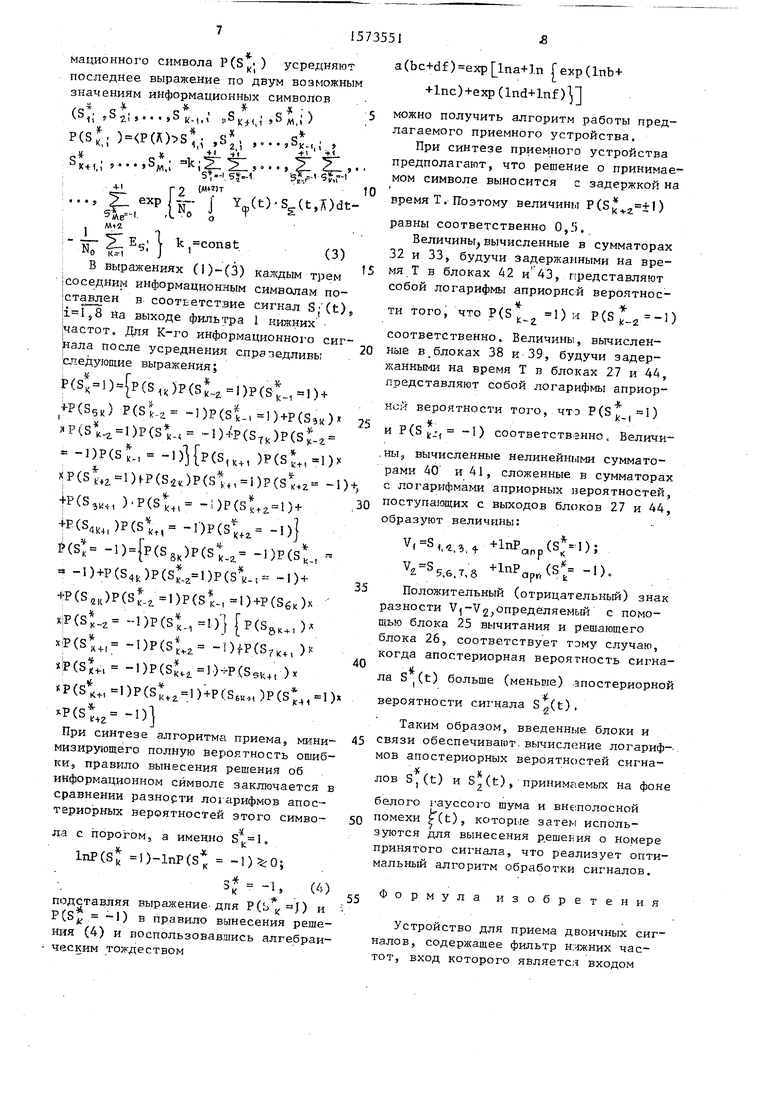

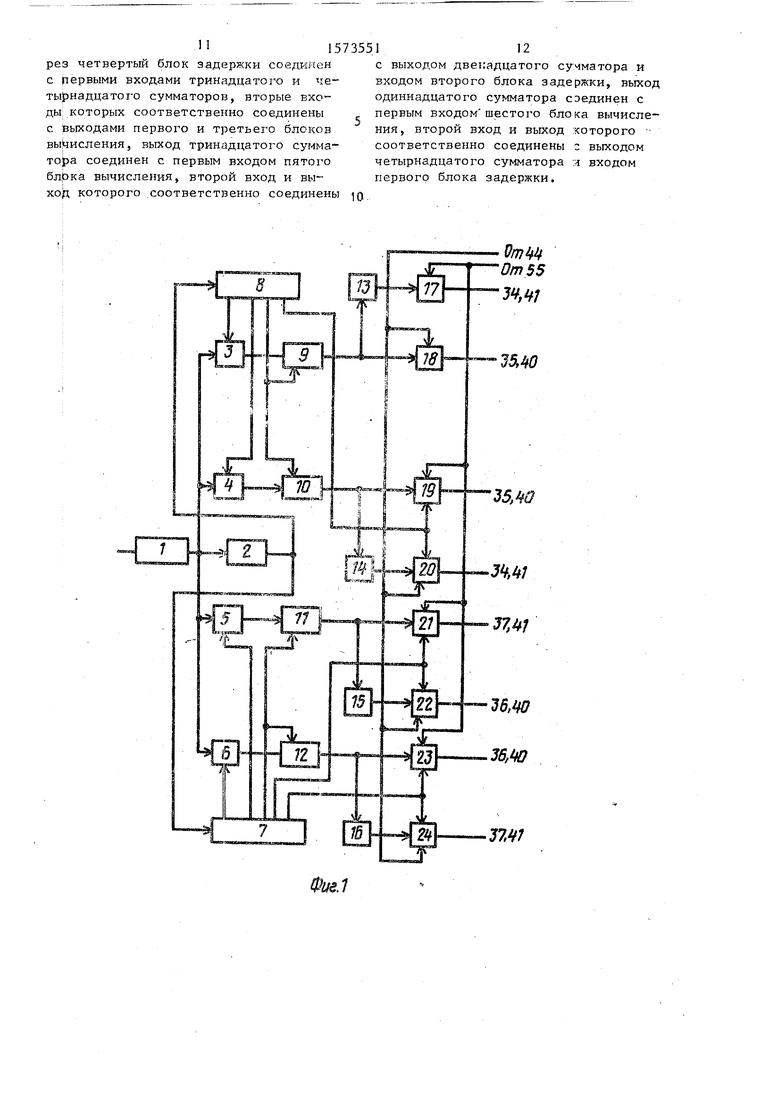

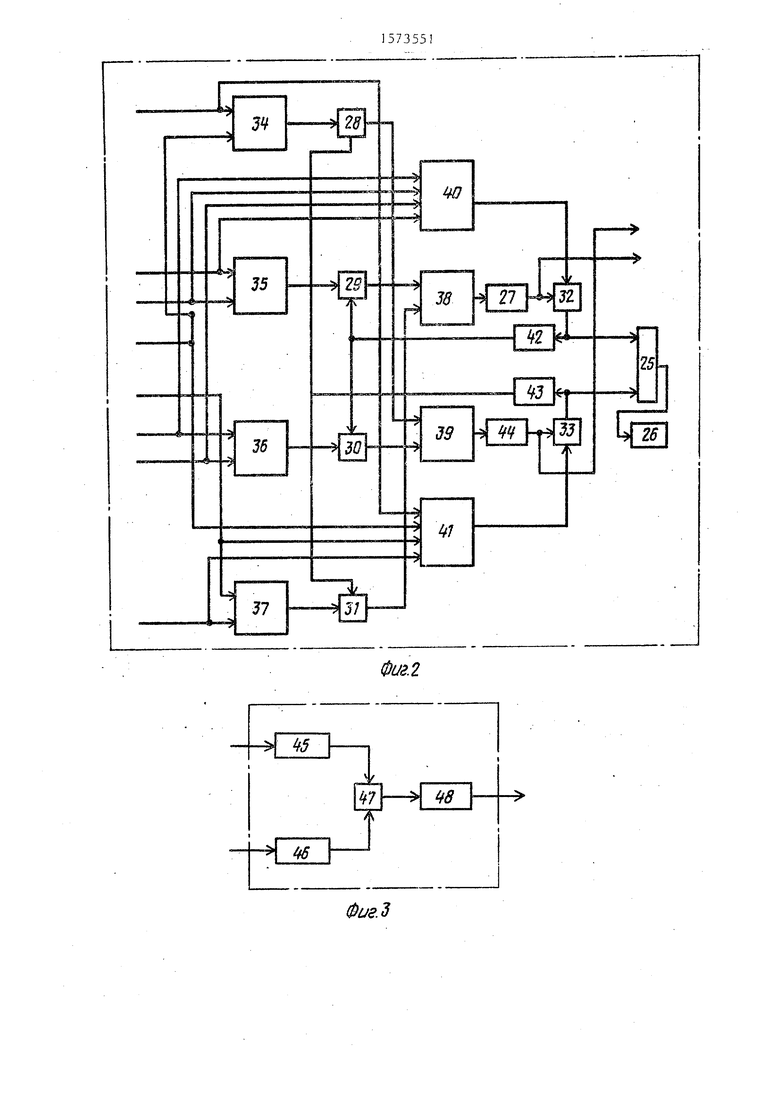

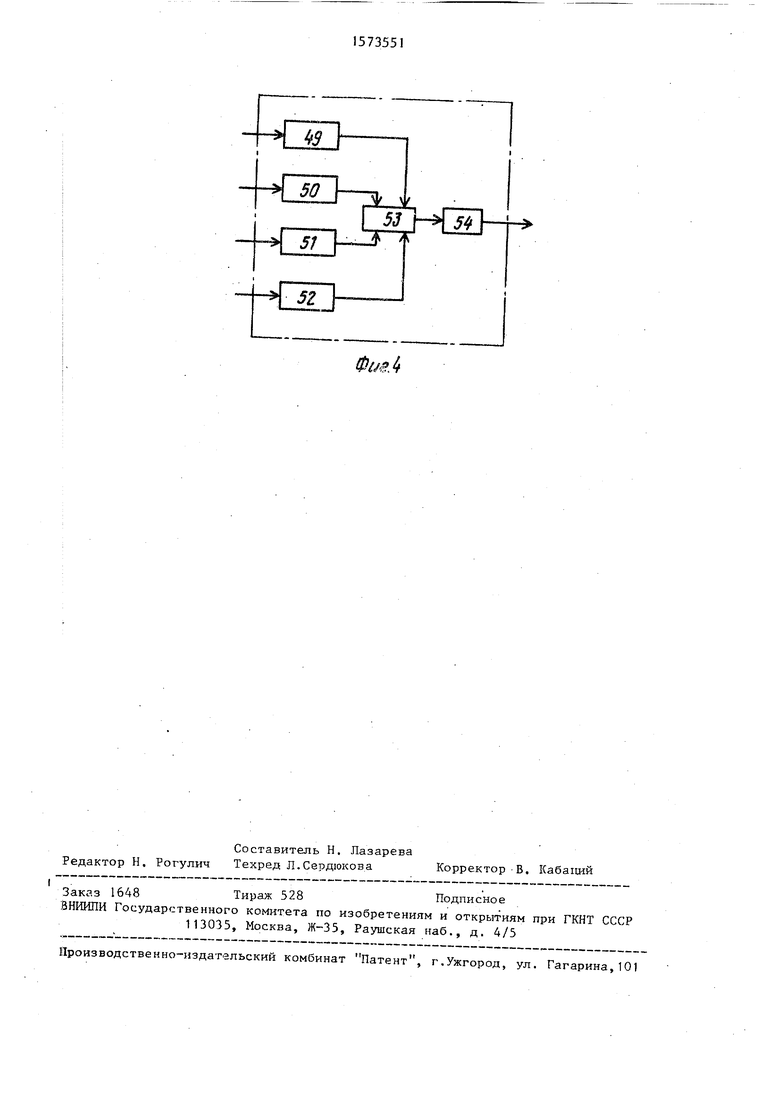

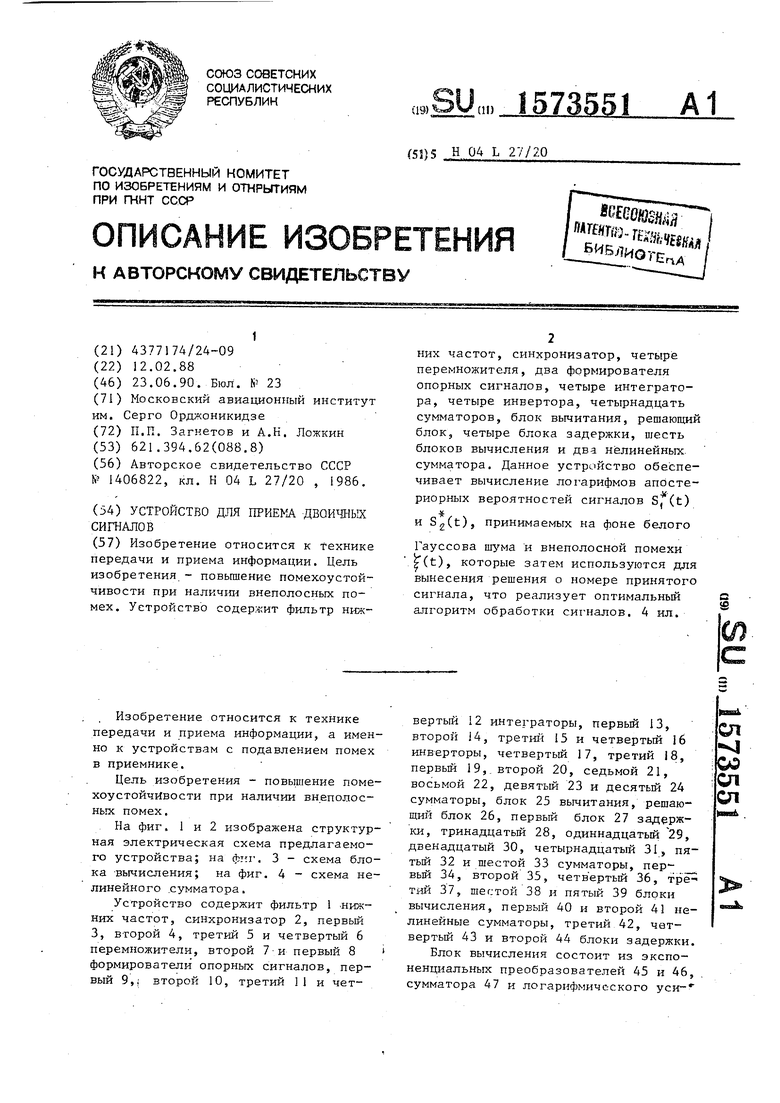

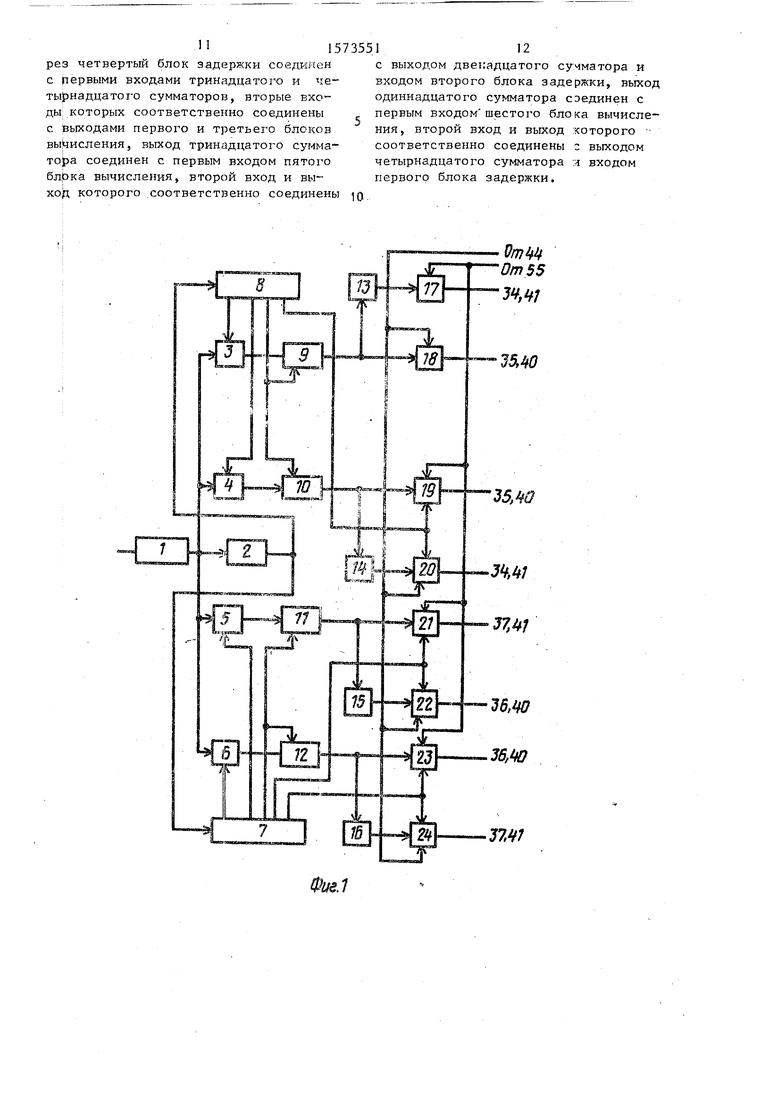

На фиг. 1 и 2 изображена структурная электрическая схема предлагаемого устройства; на . 3 - схема блока вычисления; на фиг. 4 - схема нелинейного сумматора.

Устройство содержит фильтр 1 нижних частот, синхронизатор 2, первый 3, второй 4, третий 5 и четвертый 6 перемножители, второй 7 и первый 8 формирователи опорных сигналов, первый 9,. второй 10, третий 11 и четвертый 12 интеграторы, первый 13, второй 14, третий 15 и четвертый 16 инверторы, четвертый 17, третий 18, первый 19, второй 20, седьмой 21, восьмой 22, девятый 23 и десятый 24 сумматоры, блок 25 вычитания, решающий блок 26, первый блок 27 задержки, тринадцатый 28, одиннадцатый 29, двенадцатый 30, четырнадцатый 31, пятый 32 и шестой 33 сумматоры, первый 34, второй 35, четвертый 36, тре- тий 37, шестой 38 и пятый 39 блоки вычисления, первый 40 и второй 41 нелинейные сумматоры, третий 42, четвертый 43 и второй 44 блоки задержки. Блок вычисления состоит из экспоненциальных преобразователей 45 и 46, сумматора 47 и логарифмического уси-

сл

Ч

оэ

СЛ СП

лителя 48, нелинейные сумматоры тоят из экспоненциальных преобразователей 49-52, сумматора 53 и логарифмического усилителя 54,

Входной сигнал устройства для приема двоичных сигналов

Y(t)s(t)+n(t)+Ј(t)

представляет собой аддитивную смесь

противоположных информационных сиг%налов S.(t), где ,2, длительность

5ОП4

r2(t+2T)+r2(t+T)+r,(t);

0; .

Если дительность импульсного откли- ка g(t), практически определяемая -„ не превышает по длительности величину 2Т, корреляторы, образованные перемножителями 3-6 и интеграторами 9-12, обеспечивают вычисление взаимной кор-, реляции сигналов с выхода фильтра 1 нижних частот и опорных сигналов. При Т+Та„Ј ЗТ последовательность информа

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема двоичных сигналов | 1986 |

|

SU1406812A1 |

| Устройство для приема двоичных последовательностей сигналов с межсимвольной связью | 1988 |

|

SU1660196A1 |

| Устройство для приема цифровых сигналов с непрерывной фазовой модуляцией | 1989 |

|

SU1690211A1 |

| Устройство для приема двоичных сигналов с непрерывной фазовой модуляцией | 1989 |

|

SU1753617A1 |

| Устройство для приема двоичных сигналов | 1989 |

|

SU1709550A1 |

| Стохастический фильтр | 1989 |

|

SU1675905A1 |

| СТОХАСТИЧЕСКИЙ ФИЛЬТР | 1992 |

|

RU2050590C1 |

| Устройство для приема двоичных сигналов | 1987 |

|

SU1506577A1 |

| ПРИЕМНИК ДЛЯ РЕЛЬСОВОЙ ЦЕПИ | 1994 |

|

RU2083410C1 |

| ФУНКЦИОНАЛЬНЫЙ ГЕНЕРАТОР | 2015 |

|

RU2582557C1 |

Изобретение относится к технике передачи и приема информации. Цель изобретения - повышение помехоустойчивости при наличии внеполосных помех. Устройство содержит фильтр нижних частот, синхронизатор, четыре перемножителя, два формирователя опорных сигналов, четыре интегратора, четыре инвертора, четырнадцать сумматоров, блок вычитания, решающий блок, четыре блока задержки, шесть блоков вычисления и два нелинейных сумматора. Данное устройство обеспечивает вычисление логарифмов апостериорных вероятностей сигналов S1(T) и S2(T), принимаемых на фоне белого Гауссова шума и внеполосной помехи ζ (T), которые затем используются для вынесения решения о номере принятого сигнала, что реализует оптимальный алгоритм обработки сигналов. 4 ил.

которых равна Т, белого Гауссового ционных сигналов S.(t), ,2 превра- шума n(t) и внеполосной помехи Ј(t). 75 Форма передаточной характеристики фильтра нижних частот такова, что спектральная плотность мощности смеси шума и помехи на выхода фильтра равномерна. Информационные сигналы, 20 прошедшие через фильтр 1 нижних частот, изменяют свою форму и растягиваются по длительности Вид сигнала ка выходе фш ьтра 1 нижних частот опщается на выходе фильтра 1 нижних частот в последовательность сигналов 2(t), ,8, причем форма этих сигналов соответствует форма опорных сигналов, и справедливы следующие соотношения

S,(t)Son, (t); S2(t) -Sonl(t);

S,(t)Son3(t);

ререляется сверткой сигнала S(t) и импульсного отклика фильтра g(t): r;(t) f S(t)g()du

о

Длительность сигналов г;(t) равна Т+Та, если То - длительность импульсного отклика фильтра 1, При воздействии на последний последовательности

k- сигналов S (t) выходной сигнал пред-

ставляет суперпозиции: сигналов r,(t) Опорные сигналы Son/(t) ,2,3,4 поступают на вторые входы перемножителей 3-6 с выходов формирователей 7 и 8 опорных сигналов, имеют длительность, равную Т, и синхронизированы t началом отклика фильтра 1 нижних

частот на входной сигнал S (t). Форма опорных сигналов определяется формой отклика фильтра 1 нижних частот

на воздействие сигналов S;(t).

г,(t)+r,(t+T)+r,(t+2T); 0; ,

fr,(t+2T)+r4(t+T)+r2(t); O ti-T; (

Oj ,

fr,(t+2T)+r2(t+T)+r((t); 06tЈT; s

I 0; ,

ционных сигналов S.(t), ,2 превра-

щается на выходе фильтра 1 нижних частот в последовательность сигналов 2(t), ,8, причем форма этих сигналов соответствует форма опорных сигналов, и справедливы следующие соотношения

S,(t)Son, (t); S2(t) -Sonl(t);

ционных сигналов S.(t), ,2 превра-

S,(t)Son3(t);

s4(t-)son4(t);

S5(t) -Son4 (t); S6(t) -Soni(t); Sr(t; Sona(t); Sg(t) -Son (t);

#

Если учесть, что S ,, (t) S2(t) ,то

S((t) -Sg(t); S2(t) -S7(t); S,(t) -Se(t); S4(t) -Sj(t).(2)

Энергии сигналов S;(t) где ,8 на выходе фильтра 1 нижних частот, неравны

Е|-Ег Д1; Е, Е,-Е4 йЗ,

где Е; - энергия сигнала 3;(t). Сигналы Sj(t), ,8 образуются в результате интерференции з фильтре 1 нижних частот, соседних на интервале времени ЗТ входных информационных сигналов S(t). Корреляторы, образован

ные перемножителями 3-6 и интеграторами 9-12, обеспечивают вычисление взаимной корреляции сигналов с выхода фильтра 1 нижних частот и опорных сигналов, причем, если учесть (2), то вместо восьми опорных сигналов можно использовать четыре, а дл вычисления взаимной корреляции с оставшимися сигналами, полученный результат

5

необходимо проинвертировать, как и делается в предлагаемом устройстве с помощью инверторов 13-16.

Последовательность сигналов S;(t) где ,8 на выходе фильтра 1 нижних частот, нельзя считать последовательностью статистически независимых сигналов, как это предполагается отно- сительно последовательности информа- .

аир i

где X. lYcp(t)Snn;(t)dt+lnP

О

,8;

ui-,

,3,4 - смещение, равное раз. ности опорных сигналов вычисляемое в формировационных сигналов S.(t), ,2, поэтому априорные вероятности Рапр; , ,8, появления на выходе фильтра 1 нижних частот сигнала S,.(t), ,8,

нельзя считать одинаковыми, i4

даже если сигналы S (t), ,2 в последовательности сигналов, поступающих на вход фильтра 1 нижних частот, являются статистически независимыми. Вычисленные в корреляторах значения корреляции выходного сигнала фильтра 1 нижних частот и оперных сшналов, пропорциональные логарифму функции правдоподобия сигналов S S-j,Sg,S, поступают на сумматоры 18, 19, 21 и 23, а их инверсии, пропорциональные логарифму функции правдоподобия сигналов Sз,82,86,85- на сумматоры 17,20,22 и 24. Инвертирова ние выходных величин интеграторов 9-12 осуществляется инверторами 13-1

На третьи входы сумматоров 19-24 одновременно на вторые входы сумматоров 17 и 18 поступают величины, пропорциональные логарифму априорных вероятностей сигналов SjCt), ,8, имеющиеся на выходах блоков 27 и 44,

обеспечивающих задержку на время Т.

Учитывая что энергии сигналов S|(t), ,8, не одинаковы, величины Z-, пропорциональные логарифмам апостериорных вероятностей сигналов S,-(t можно записать так

7 -У

/ч -л, ,

гг Ха+А1;

-Z} X3+A2;

Z4 X4+A3;

Z5 X5+A3;

Z6 X6+U2;

Z7 X7+A1;

.

2 1 oni (t)-S on

;(t)dt;

ҐФ

телях 7 и 8 опорных сигналов;

сигнал с выхода фильтра 1 нижних частот. Смещение U1 поступает с четвертого выхода формирователя 8 на вторые входы сумматоров 21 и 22, U3 - на вторые входы сумматоров 23 и 24, Л 2 с четвертого выхода формирователя 7 на вторые входы сумматоров 19 и 20.

Блоки 34-39 индентичны. Каждый из блоков нелинейной обработки вычисляет величину

Wa ln exp(Zk)+exp(Ze); K,

Нелинейные сумматоры 40 и 41 идентичны. Каждый из них вычисляют величину

SK.L.W.N (ZK)+exp(Zt)+exp(ZjV1)-f +exp(ZN); K,L,M,.

Алгоритм работы предлагаемого приемного устройства получен путем усреднения алгоритма работы приемного устройства для приема в целом по двум возможным значениям информационных символов.

Суммарный сигнал на выходе Фильтра 1 нижних частот определяют как

Ss(t,A), где Л s,,...fsJ,

,2 - входная реализация Минформационных сигналов.

Любая реализация суммарного сигнала S(t,A) на выходе фильтра 1 нижних частот занимает интервал времени (0; (M+2). В предположении того, что на выходе фильтра 1 нижних частот присутствует смесь белого шума n(t) со спектральной плотностью N0, апостериорная вероятность реализации суммарного сигнала (или вектора ft) в момент времени t(M+2)T равна

(t,A)K0Pan (Юехр Г- Vu.iVr L О

(«+2lT

/мгг)т 2 ()т

J sЈ(t, + J Y(t)SsCt,A-)

К -const,

где Y(p(t)bЈ(t,l)+n(t) - аддитивная смесь последовательности интерферирующих сигналов и белого шума.

Первое слагаемое в выражении - сумма энергий непрекрывающихся сигналов S(c), 1-М,8, для получения апостериорной вероятности К-го информационного символа P(SK-) усредняют последнее выражение по двум возможным значениям информационных символов

ее с с ч . ч О bi , ьг « « ак-1н DK + ,,

. „х

ii f

:

P(SЈ; )P(K)S ,S. .....SK.,,.,

«-ft,;

И

21 exp

Sle . м+г

L «5- F

No Јi5

-ЧЈ$Г Ј.

{о {м+ )тf 0

r; / .)

k const

(3)

a(bc+df )exp jLna+Jn fe:xp(lnb+ +lnc)+exp(Ind+lnf)

5 можно получить алгоритм работы предлагаемого приемного устройства.

При синтезе приемного устройства предполагают, что решение о принимаемом символе выносится с задержкой на

время Т. Поэтому величины Р()

равны соответственно 0,. i,

Величины,вычисленные в сумматорах 32 и 33, будучи задержанными на вреВ выражениях ()-(3) каждым трем 15 МЯ Т В бЛ°КЗХ А2 И 43 Г РеДставляют

собой логарифмы априорной вероятноесоседним информациейчым символам по- стйЈ3ен в соответствие сигнал S; (t)s ,8 на выходе фильтра 1 нижних частот. Для Кто информационного сигнала после усреднения справедливы следующие выражения;

p(){p(sn)p(sj,)p(st,i)+

/PCSen) P(S.a -I)P()+P(SSK)x я PiS 1 )P(S.« -1 )-/-P(STk)P(Sl-z -OP(sJ., « -l){p(Sm, )P(,-I)x xP(st+zeOfP(S2)t)P(SJ|4,l)P( -l)+t

4-P(S,, ) P(st,, -OP(sItz l) +

ч-ути того, что P(S 1) и P( -l)

соответственно. Величины, вычислен- 20 ные в блоках 38 к 39, будучи задержанными на время Т в блоках 27 и 44, представляют собой логарифмы априорнсл вероятности того, чтэ P(Sk 1}

25

30

4P(S«4|)P(, -OP( -I)j

P(st (s8K)p(st. -DP(st., -O+P(s4k)p()p(sVi-- -D+

+P(S4R)P()P(S.)+P(S6K)x

KP( OP( )} {P(S&K+, ) xP(, -1)P(SJ.2 -i)fP(S7K4l )x

«p(s, -DPCs -D-PCSe, )x

IK + 2.1/ V%J6KH v - /c i

и P(Sj,( -1) соответствгнно. Величины, вычисленные нелинейными сумматорами 40 и 41, сложенные в сумматорах с логарифмами априорных вероятностей, поступающих с выходов блоков 27 и 44, образуют величины:

,.4i3i4. +lnPanp();

ЪвЈЧб.т,в -

35 Положительный (отрицательньй) знак разности ,определяемый с помощью блока 25 вычитания и решающего блока 26, соответствует тэму случаю, когда апостериорная вероятность сигна40

Р()Р(81 ,1)+P(S6KM)P(S ,-)«

P(S

х-к %

If+Z

-о

ла S (t) больше (меньпю) апостериорной

вероятности сигнала S2(t),

Таким образом, введенные блоки и

При синтезе алгоритма приема, мини- 45 связи обеспечивают вычисление логарифмов апостериорных вероятностей сигнамизирующего полную вероятность ошибки, правило вынесения решения об информационном символе заключается в сравнении разности лохарифмов апостериорных вероятностей этого симво«л.а с порогом, а именно

lnP(sJ l)-lnP(S -1)0;

3j -1, (4)

подставляя выражение для Р(Ь к aj) и PCS - I) в правило вынесения решения (4) и воспользовавшись алгебраическим тождеством

#it

лов SjCt) и S2(t), принимЈ1емых на фоне

белого гауссого шума и вне полосной 5Q помехи Mt), которые затем используются для вынесения решения о номере принятого сигнала, что реализует оптимальный алгоритм обработки сигналов.

55

Формула изобретения

Устройство для приема двоичных сигналов, содержащее фильтр нижних частот, вход которого являете входом

a(bc+df )exp jLna+Jn fe:xp(lnb+ +lnc)+exp(Ind+lnf)

можно получить алгоритм работы предлагаемого приемного устройства.

При синтезе приемного устройства предполагают, что решение о принимаемом символе выносится с задержкой на

время Т. Поэтому величины Р()

равны соответственно 0,. i,

Величины,вычисленные в сумматорах 32 и 33, будучи задержанными на вреч-ути того, что P(S 1) и P( -l)

соответственно. Величины, вычислен- ные в блоках 38 к 39, будучи задержанными на время Т в блоках 27 и 44, представляют собой логарифмы априорнсл вероятности того, чтэ P(Sk 1}

и P(Sj,( -1) соответствгнно. Величины, вычисленные нелинейными сумматорами 40 и 41, сложенные в сумматорах с логарифмами априорных вероятностей, поступающих с выходов блоков 27 и 44, образуют величины:

,.4i3i4. +lnPanp();

ЪвЈЧб.т,в -

Положительный (отрицательньй) знак разности ,определяемый с помощью блока 25 вычитания и решающего блока 26, соответствует тэму случаю, когда апостериорная вероятность сигна

ла S (t) больше (меньпю) апостериорной

вероятности сигнала S2(t),

Таким образом, введенные блоки и

#it

лов SjCt) и S2(t), принимЈ1емых на фоне

белого гауссого шума и вне полосной помехи Mt), которые затем используются для вынесения решения о номере принятого сигнала, что реализует оптимальный алгоритм обработки сигналов.

Формула изобретения

Устройство для приема двоичных сигналов, содержащее фильтр нижних частот, вход которого являете входом

устройства, а выход соединен с входом синхронизатора и первыми входами первого и второго перемножителей, выход синхронизатора соединен с входом пер- вого формирователя опорных сигналов, первый и второй выходы которого соединены соответственно с вторыми входами первого и второго перемножителей, выходы которых соответственно соеди- йены с первыми входами первого и второго интеграторов, вторые входы которых соединены с третьим выходом формирователя опорных сигналов, четвертый выход которого соединен с первыми входами первого и второго сумматоров, выход первого интегратора соединен с первым входом третьего сумматора и через первый инвертор с первым входом четвертого сумматора, выход вто- рого интегратора соединен с вторым входом первого сумматора и через второй инвертор с вторым входом второго сумматора, четыре блока вычисления, первый блок задержки, выход которого соединен с первым входом пятого сумматора, вторым входом третьего сумматора и третьим входом второго сумматора, выход пятого сумматора соединен с первым входом блока вычитания, вто- рой вход которого соединен с выходом шестого сумматора, первый вход которого, второй вход четвертого сумматора и третий вход первого сумматора соединены с выходом второго блока за- держки, выход блока вычитания соединен с входом решающего блока, выход которого является выходом устройства, выходы четвертого и третьего сумматоров соединены соответственно с первыми входами первого и второго блоков вычитания, отличающееся тем, что, с целью повышения помехоустойчивости при наличии внеполостных помех, введены второй формирователь опорных сигналов, третий, четвертый перемножители, третий, четвертый интеграторы, третий, четвертый инверторы, седьмой - четырнадцатый сумматоры, пятый}шестой блоки вычисления, первый, второй нелинейные сумматоры, третий, четвертый блоки задержки, причем выход фильтра нижних частот соединен с первыми входами третьего и четвертого перемножи- телей, выходы которых соответственно соединены с первыми входами третьего и четвертого интеграторов, выход синхронизатора соединен с входом второго формирователя опорных сигналов, первый, второй, третий, четвертый у. пятый выходы которого соединены соответственно с вторым входом четвертого перемножителя, вторым входом третьего перемножителя, вторыми входами-1 третьего и четвертого интеграто ров, первыми входами седьмого и вось мсго сумматоров, первыми входами де- , десятого сумматоров, выход третьего интегратора соединен с вторым входом седьмого сумматора и чере третий инвертор с вторым входом восьмого сумматора, выход четвертого интегратора соединен с вторым входом девятого сумматора и через четвертый инвертор с вторым входом десятого сумматора, выход первого блока задержки соединен с третьими входами восьмого и десятого сумматоров, выход второго блока задержки соединен с третьими входами седьмого и девятого сумматоров, выход первого сумматора соединен с вторым входом второго блока вычисления и первым входом первого нелинейного сумматора, выход второго сумматора соединен с вторым входом первого блока вычисления и первым входом второго нелинейного сумматора, выход седьмого сумматора соединен с вторым входом второго нелинейного сумматора и первым входом третьего блока вычисления, выход восьмого сумматора соединен с вторым входом первого нелинейного сумматора и первым входом четвертого блока- вычисления, выход девятого сумматора соединен с третьим входом первого нелинейного сумматора и вторым входом четвертого блока вычисления, выход десятого сумматора соединен с вторым входом третьего блока вычисления и третьим входом второго нелинейного сумматора, четвертый вход которого соединен с выходом четвертого сумматора, выход третьего сумматора соединен с четвертым входом первого нелинейного сумматора, выход которого соединен с вторым входом пятого сумматора, выход которого через третий блок задержки соединен с первыми входами одиннадцатого и двенадцатого сумматоров, вторые входы которых соответственно соединены с выходами второго и четвертого блоков вычисления, выход второго нелинейного сумматора соединен с вторым входом шестого сумматора, выход которого че1115

рез четвертый блок задержки соединен с первыми входами тринадцатого и четырнадцатого сумматоров, вторые входы которых соответственно соединены с выходами первого и третьего блоков вычисления, выход тринадцатого сумматора соединен с первым входом пятого блока вычисления, второй вход и выход которого соответственно соединены

112

с выходом двенадцатого сучматора и входом второго блока задержки, выход одиннадцатого сумматора сэединен с первым входом шестого блока вычисления, второй вход и выход оторого соответственно соединены ; выходом четырнадцатого сумматора входом первого блока задержки.

ОтМ От 55

nw

nw

Фиг.3

Ы-H jtfJ--CiD-3

ЮATM лН-п

0//.4

| Устройство стабилизации уровня видеосигнала | 1987 |

|

SU1406822A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-06-23—Публикация

1988-02-12—Подача