Изобретение относится к технике передачи и приема информации, а именно к устройствам приема сигналов с межсимвольной связью.

Цель изобретения - упрощение устройства.

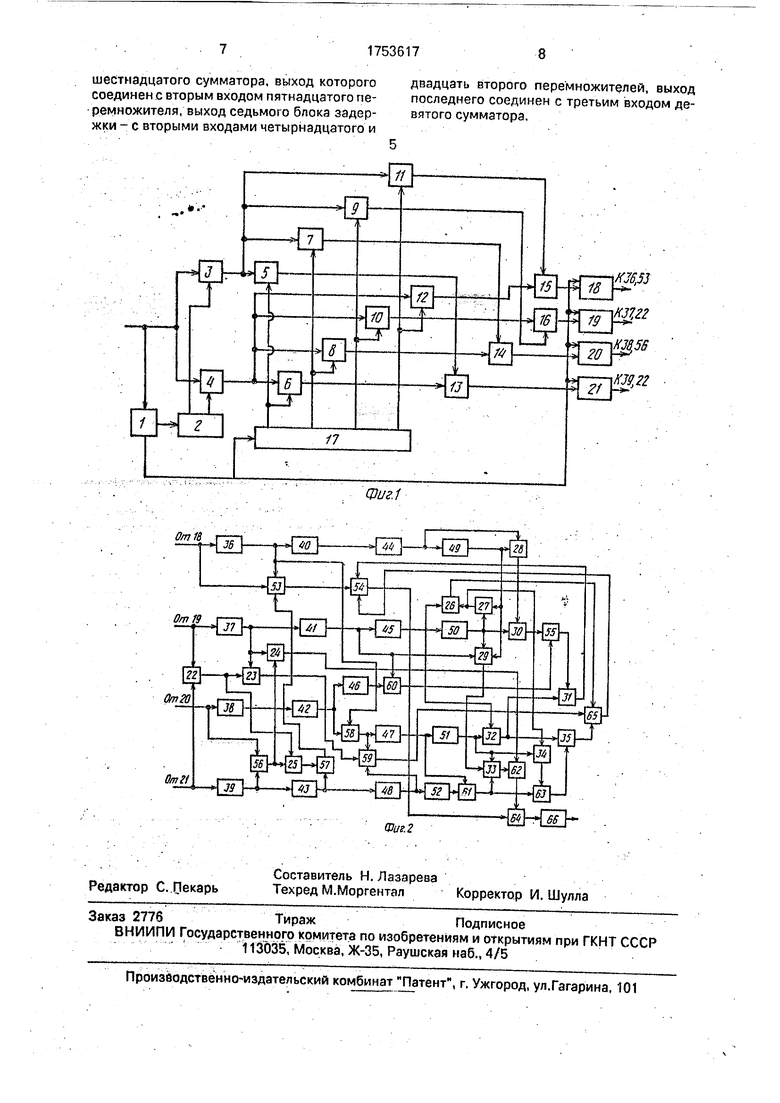

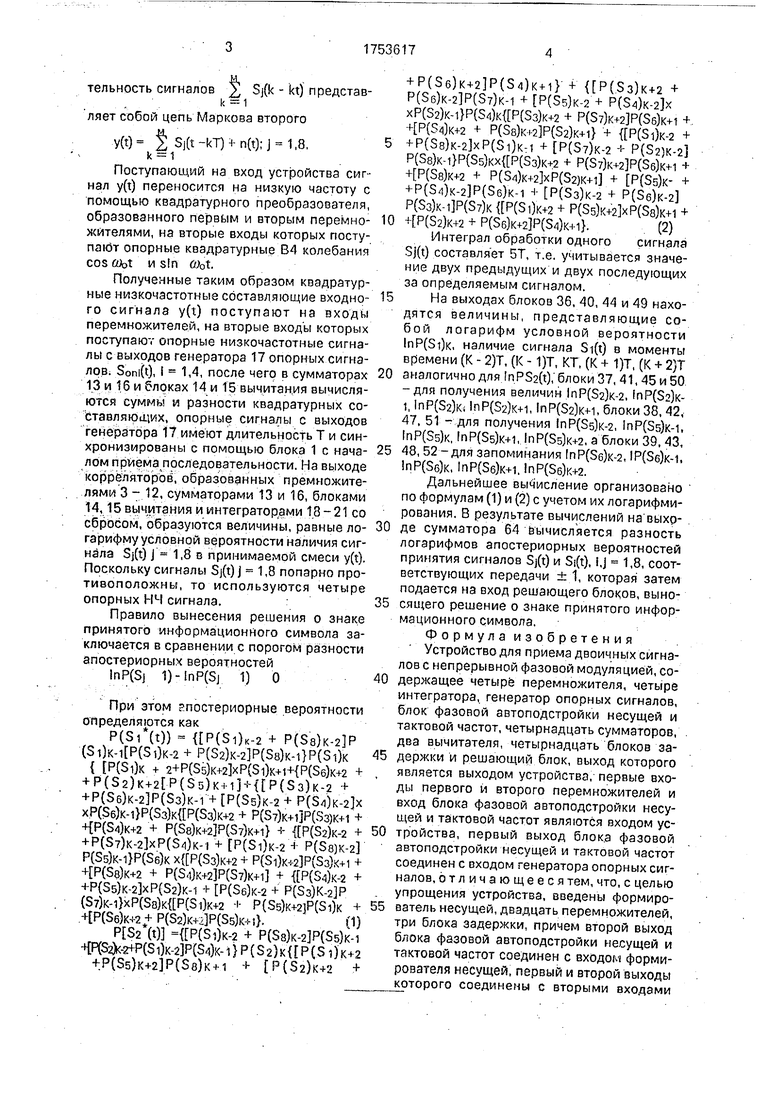

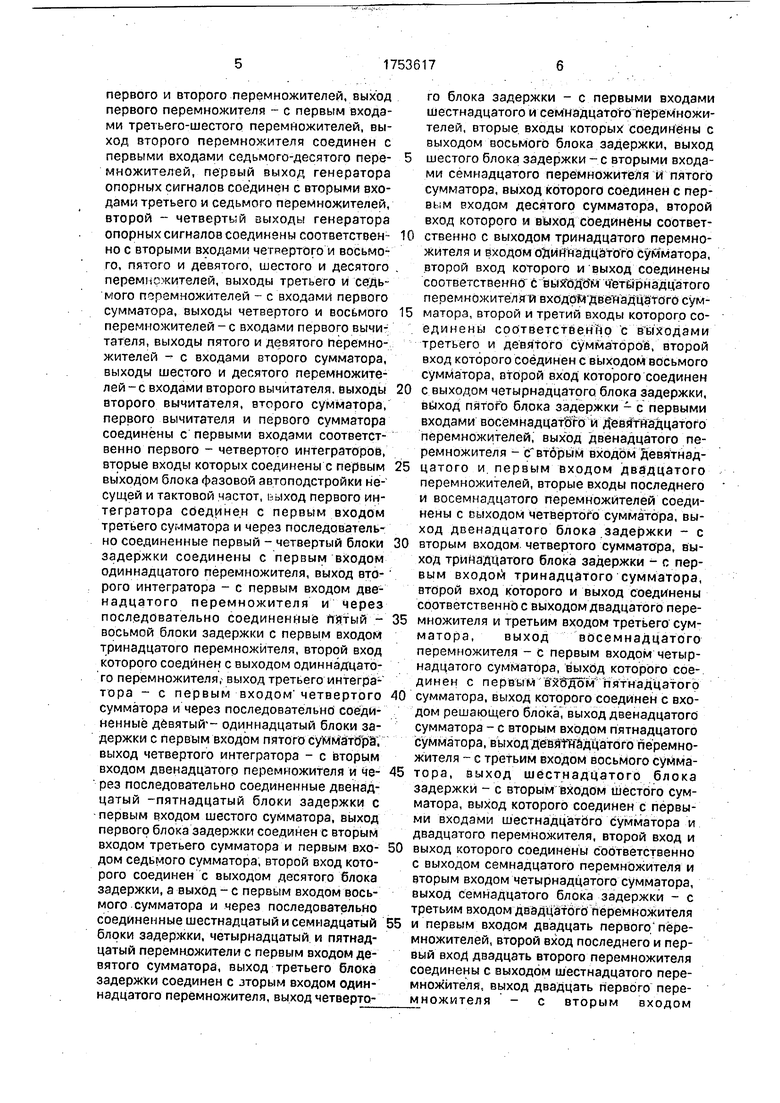

На фиг.1 и 2 изображена структурная электрическая схема предлагаемого устройства.

Устройство содержит блок 1 фазовой автоподстройки несущей и тактовой частот, формирователь 2 несущей, первый, второй, третий, седьмой, четвертый, восьмой, пятый, девятый, шестой, десятый, перемножители 3-12, первый сумматор 13, первый вычитатель 14, второй вычитатель 15, вто- рой-сумматор 16, генератор 17опорныхсигналов, первый - четвертый интеграторы 18 - 21, двенадцатый, девятнадцатый, восемнадцатый, двадцатый, двадцать второй, шестнадцатый, одиннадцатый, семнадцатый,

тринадцатый, перемножители 22 - 30, одиннадцатый сумматор 31, четырнадцатый пе- ремножитель32, двадцатый, двадцать первый, пятнадцатый перемножители 33 - 35, первый, пятый, девятый, двенадцатый, йторой, шестой, десятый, тринадцатый, третий, седьмой, одиннадцатый, шестнадцатый, четырнадцатый, четвертый, восьмой, семнадцатый, пятнадцатый блоки 36 - 52 задержки, третий, двенадцатый, десятый, четвертый, тринадцатый, седьмой, восьмой, пятый, шестой, четырнадцатый, шестнадцатый, пятнадцатый, девятый сумматоры 53 - 65, решающий блок 66.

Устройство работает следующим образом.

На вход устройства поступает аддатив- ная смесь y(t) последовательности сигналов Sj(t); j 1,8 и белого гауссового шума n(t) со спектральной плотностью М0. Сформированная с помощью модулятора последовая

со о

VJ

тельность

сигналов 2 Sj(k kt) представk 1

ляет собой цепь Маркова второго УЮ- | Sj()-i-n(t);j 1,8,

Поступающий на вход устройства сигнал y(t) переносится на низкую частоту с помощью квадратурного преобразователя, образованного первым и вторым перемножителями, на вторые входы которых поступают опорные квадратурные В4 колебания cos и stn (Dot

Полученные таким образом квадратурные низкочастотные составляющие входного сигнала y(t) поступают на входы перемножителей, на вторые входы которых поступают опорные низкочастотные сигналы с выходов генератора 17 опорных сигналов. Soni(t), I 1,4, после чего в сумматорах 13 и 16 и блоках 14 и 15 вычитания вычисляются суммы и разности квадратурных составляющих, опорные сигналы с выходов генератора 17 имеют длительность Т и синхронизированы с помощью блока 1 с началом приема последовательности. На выходе корреляторов, образованных премножите- лями 3 - 12, сумматорами 13 и 16, блоками 14,15 вычитания и интеграторами 18-21 со сбросом, образуются величины, равные логарифму условной вероятности наличия сигнала Sj(t) j 1,8 в принимаемой смеси y(t). Поскольку сигналы Sj(t) j 1,8 попарно противоположны, то используются четыре опорных НЧ сигнала.

Правило вынесения решения о знаке принятого информационного символа заключается в сравнении с порогом разности апостериорных вероятностей InPfSj 1)-InP(Sj 1) О

При этом апостериорные вероятности определяются как

P(Si(t)J - (Si)K-2 + Р(88)

(Sl)(St)K-2 + P(S2)(S8)K-1}P(S1)K

{ P(Sl)K + 2+P(S5)(Sl)K+1+{P(S6)K+2 + + P(S2)(S5)KM + (S3)K-2 +

+ Р(5б)(5з)к-1 + P(Ss)K-2 + Р(54) хР(56)к-1}Р(5з)(5з)к+2 + Р(57)(5з)к+1 +

+{P(S4)K+2 + Р(58)(57)ш} + (S2)K-2 + + P(S)(S4)K-1 + P(Sl)K-2 - P(S8)K-2 P(S5)K-l}P(S6)(S3)K+2+ P(Sl)(S3kM + (Ss)K+2 + P(S4)(S)K+1 + (S4)K-2 + +P(S5)(S2)K-1 + P(Se)K-2 + P(S3) (S7)K-l}xP(S8))K+2 -I- P(S5)(Sl)K + (S6}K+2 + P(S2)K+JP(S5)K+l).(1)

(t) (Sl)K-2 + P(S8)(S5)K-1 -t{P(S2(-2+P(Sl)(S4}K-l} P(S2)(S 1)к+2 + P(S5)K+2JP(Se) + P(S2)K+2 +

+ P(S6)K + (S4) + (S3)K + 2 + P(S6)(S7)K-1 + P(S5)K-2 + P(S4) xP(S2)K-l}P(S4)(S3)K+2 + P(S7)(S6)K+1 + (4)K+-2 + P(SS)(S2)K+1} + (Sl)K-2 + +P(S8)(S1)K-1 + P(S)K-2 + P(S2)K-2 P(S8)K-l}P(S5)(S3)K+2 + Р(57)(56)Ш + (S8)K+2 + P(S4)(S2)K+1 + P{S5)K- + + P(S4)(S6)K-1 H P(S3)K-2 + P(S6)K-2

Р(5з)(57)к (Si)K+2 + Р(85)(8в)к+1 +

(52)к+2 + Р(8б)($4)кч1}.(2)

Интеграл обработки одного сигнала Sj(t) составляет 5Т, т.е. учитывается значение двух предыдущих и двух последующих за определяемым сигналом.

5 На выходах блоков 36, 40, 44 и 49 находятся величины, представляющие собой логарифм условной вероятности lnP(Si)K, наличие сигнала Si(t) в моменты времени (К - 2)Т, (К - 1)Т, КТ, (К + 1)1, (К + 2}Т

0 аналогично для nPS2(t), блоки 37, 41, 45 и 50 -для получения величин 1пР(52)к-2, 1пР($2)к- 1,1пР($2)к, 1пР(52)к+1, lnP(S2)K+i, блоки 38, 42, 47, 51 - для получения lnP(Ss)K-2, 1пР(35)к-1, lnP(Ss)K, 1пР(5б)к+1, пР(55)к+2, а блоки 39, 43,

5 48, 52-для запоминания (пР(5б)к-2, Р(Зб)к-1. пР(5б)к, 1пР(5б)к+1. пР(5е)к+2.

Дальнейшее вычисление организовано по формулам (1) и (2) с учетом их логарифмирования. В результате вычислений на выхо0 де сумматора 64 вычисляется разность логарифмов апостериорных вероятностей принятия сигналов Sj(t) и Si(t), i,j 1,8, соответствующих передачи ± 1, которая затем подается на вход решающего блоков, выно5 сящего решение о знаке принятого информационного символа.

Формула изобретения Устройство для приема двоичных сигналов с непрерывной фазовой модуляцией, со0 держащее четыре перемножителя, четыре интегратора, генератор опорных сигналов, блок фазовой автоподстройки несущей и тактовой частот, четырнадцать сумматоров, два вычитателя, четырнадцать блоков за5 держки и решающий блок, выход которого является выходом устройства, первые входы первого и второго перемножителей и вход блока фазовой автоподстройки несущей и тактовой частот являются входом ус0 тройства, первый выход блока фазовой автоподстройки несущей и тактовой частот соединен с входом генератора опорных сигналов, отличающееся тем, что, с целью упрощения устройства, введены формиро5 ватель несущей, двадцать перемножителей, три блока задержки, причем второй выход блока фазовой автоподстройки несущей и тактовой частот соединен с входом формирователя несущей, первый и второй выходы которого соединены с вторыми входами

первого и второго перемножителей, выход первого перемножителя - с первым входами третьего-шестого перемножителей, выход второго перемножителя соединен с первыми входами седьмого-десятого перемножителей, первый выход генератора опорных сигналов соединен с вторыми входами третьего и седьмого перемножителей, второй - четвертый выходы генератора опорных сигналов соединены соответствен - но с вторыми входами четвертого и восьмого, пятого и девятого, шестого и десятого перемнскителей, выходы третьего и седьмого поремножителей - с входами первого сумматора, выходы четвертого и восьмого перемможителей-с входами первого вычи- тателя, выходы пятого и девятого перемножителей - с входами второго сумматора, выходы шестого и десятого перемножителей-с входами второго вычитателя, выходы второго вычитателя, второго сумматора, первого вычитателя и первого сумматора соединены с первыми входами соответственно первого - четвертого интеграторов, вторые входы которых соединены с первым выходом блока фазовой автоподстройки несущей и тактовой частот, ьыход первого интегратора соединен с первым входом третьего сумматора и через последовательно соединенные первый - четвертый блоки задержки соединены с первым входом одиннадцатого перемножителя, выход второго интегратора - с первым входом двенадцатого перемножителя и через последовательно соединенные пятый - восьмой блоки задержки с первым входом тринадцатого перемножителя, второй вход которого соединен с выходом одиннадцатого перемножителя, выход третьего интегратора - с первым входом четвертого сумматора и через последовательно соединенные девятый4- одиннадцатый блоки задержки с первым входом пятого сумматора, выход четвертого интегратора - с вторым входом двенадцатого перемножителя и через последовательно соединенные двенадцатый -пятнадцатый блоки задержки с первым входом шестого сумматора, выход первого блока задержки соединен с вторым входом третьего сумматора и первым входом седьмого сумматора, второй вход которого соединен с выходом десятого блока задержки, а выход - с первым входом восьмого сумматора и через последовательно соединенные шестнадцатый и семнадцатый блоки задержки, четырнадцатый и пятнадцатый перемножители с первым входом девятого сумматора, выход третьего блока задержки соединен с зторым входом одиннадцатого перемножителя, выход четвертого блока задержки - с первыми входами шестнадцатого и семнадцатого перемножи- телей, вторые входы которых соединены с выходом восьмого блока задержки, выход 5 шестого блока задержки - с вторыми входами семнадцатого перемножителя и пятого сумматора, выход которого соединен с пер- вь.м еходом десятого сумматора, второй вход которого и выход соединены соответ10 ственно с выходом тринадцатого перемножителя и входом одиннадцатого сумматора, второй вход которого и выход соединены соответственно с выЯодочм четырнадцатого перемножителята входом двенадцатого сум15 маторз, второй и третий входы которого соединены соответственно с выходами третьего и девятого сумматоров, второй вход которого соединен с выходом восьмого сумматора, второй вход которого соединен

0 с выходом четырнадцатого блока задержки, выход пятого блока задержки - с первыми входами восемнадцатой и Девятнадцатого перемножителей, выход двенадцатого перемножителя - с вторым входом девятнад5 цатого и первым входом двадцатого перемножителей, вторые входы последнего и восемнадцатого перемножителей соединены с выходом четвертого сумматора, выход двенадцатого блока задержки - с

0 вторым входом четвертого сумматора, выход тринадцатого блока задержки - с первым входом тринадцатого сумматора, второй вход которого и выход соединены соответственное выходом двадцатого пере5 множителя и третьим входом третьего сумматора, выход восемнадцатого перемножителя - с первым входом четырнадцатого сумматора, выход которого соединен с первым в хвдом пятнадцатого

0 сумматора, выход которого соединен с входом решающего блока, выход двенадцатого сумматора - с вторым входом пятнадцатого сумматора, выход девятнадцатого перемножителя - с третьим входом восьмого сумма5 тора, выход шестнадцатого блока задержки - с вторым входом шестого сумматора, выход которого соединен с первыми входами шестнадцатого сумматора и двадцатого перемножителя, второй вход и

0 выход которого соединены соответственно с выходом семнадцатого перемножителя и вторым входом четырнадцатого сумматора, выход семнадцатого блока задержки - с третьим входом двадцатого перемножителя

5 и первым входом двадцать первого перемножителей, второй вход последнего и первый вход двадцать второго перемножителя соединены с выходом шестнадцатого перемножителя, выход двадцать первого пере- множителя - с вторым входом

шестнадцатого сумматора, выход которого двадцать второго перемножителей, выход соединен с вторым входом пятнадцатого пе- последнего соединен с третьим входом де- ремножителя, выход седьмою блока задер- вятого сумматора. жки - с вторыми входами четырнадцатого и

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема цифровых сигналов с непрерывной фазовой модуляцией | 1989 |

|

SU1690211A1 |

| Устройство для приема двоичных сигналов | 1988 |

|

SU1573551A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2018 |

|

RU2708956C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ (N, 3) КОДА И (N, 4)КОДА С ИСПОЛЬЗОВАНИЕМ СИМПЛЕКСНЫХ КОДОВ | 2001 |

|

RU2234187C2 |

| Моментный электродвигатель постоянного тока с ограниченным углом поворота | 1990 |

|

SU1757038A1 |

| Устройство для приема двоичных сигналов | 1986 |

|

SU1406812A1 |

| Устройство для измерения активной мощности основной гармоники прямой последовательности фаз трехфазной сети | 1984 |

|

SU1250974A1 |

| Устройство для приема двоичных последовательностей сигналов с межсимвольной связью | 1988 |

|

SU1660196A1 |

| СПОСОБ СОГЛАСОВАНИЯ МОМЕНТА СРАБАТЫВАНИЯ НЕКОНТАКТНОГО ДАТЧИКА ЦЕЛИ И ОБЛАСТИ ВОЗМОЖНОГО ПОРАЖЕНИЯ ЦЕЛИ (ВАРИАНТЫ) И СИСТЕМА ДЛЯ ЕГО РЕАЛИЗАЦИИ (ВАРИАНТЫ) | 2006 |

|

RU2334193C1 |

| САМОНАСТРАИВАЮЩИЙСЯ ЭЛЕКТРОПРИВОД МАНИПУЛЯЦИОННОГО РОБОТА | 2015 |

|

RU2593735C1 |

Изобретение относится к технике передачи и приема информации. Целью изобретения является упрощение устройства. В качестве модулятора предлагается использовать устройства, обеспечивающие непрерывность фазы передаваемого сигнала на всем интервале передачи соотношения. Высокая помехоустойчивость достигается за счет оптимальной посимвольной обработки принимаемого группового сигнала с учетом межсимвольной частотно-фазовой связи. Критерием оптимальности является минимум полной ошибки при приеме двоичных сигналов, 2 ил.

ОтГЗ

М6&

щгг

Фиг 2

| Устройство для приема цифровых сигналов с непрерывной фазовой модуляцией | 1989 |

|

SU1690211A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-08-07—Публикация

1989-06-14—Подача