Изобретение относится к технике передачи и приема информации.

Цель изобретения - повышение помехоустойчивости при наличии внеполосных помех.

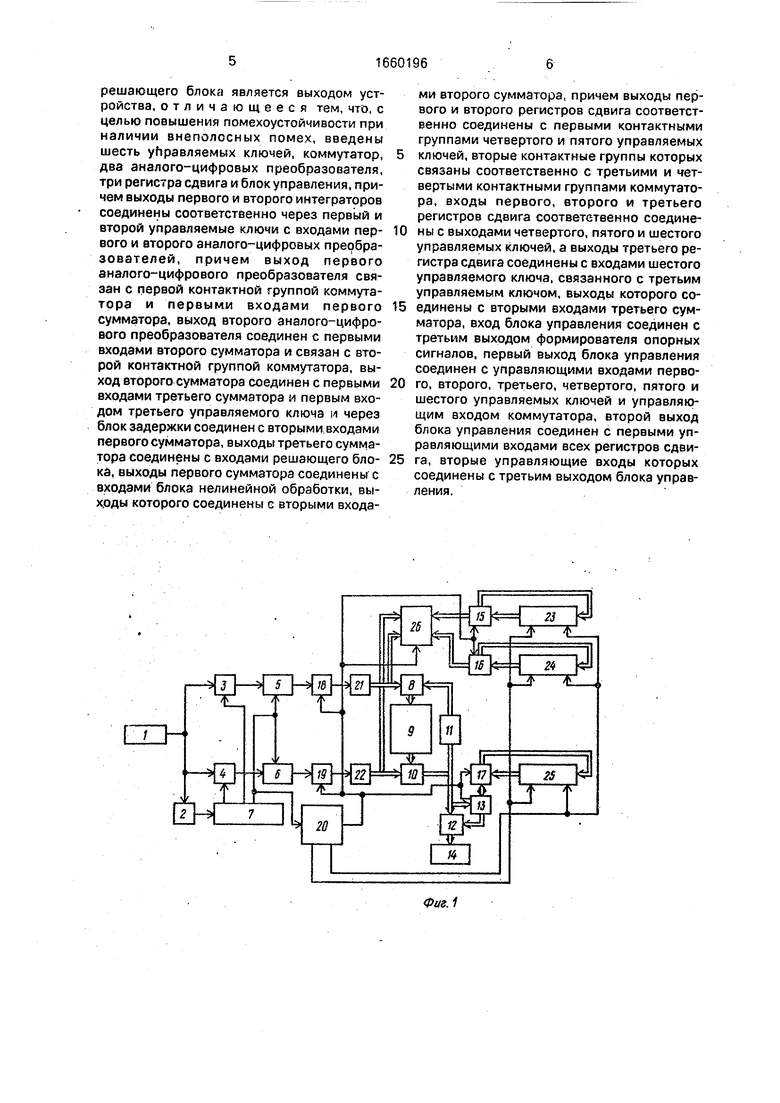

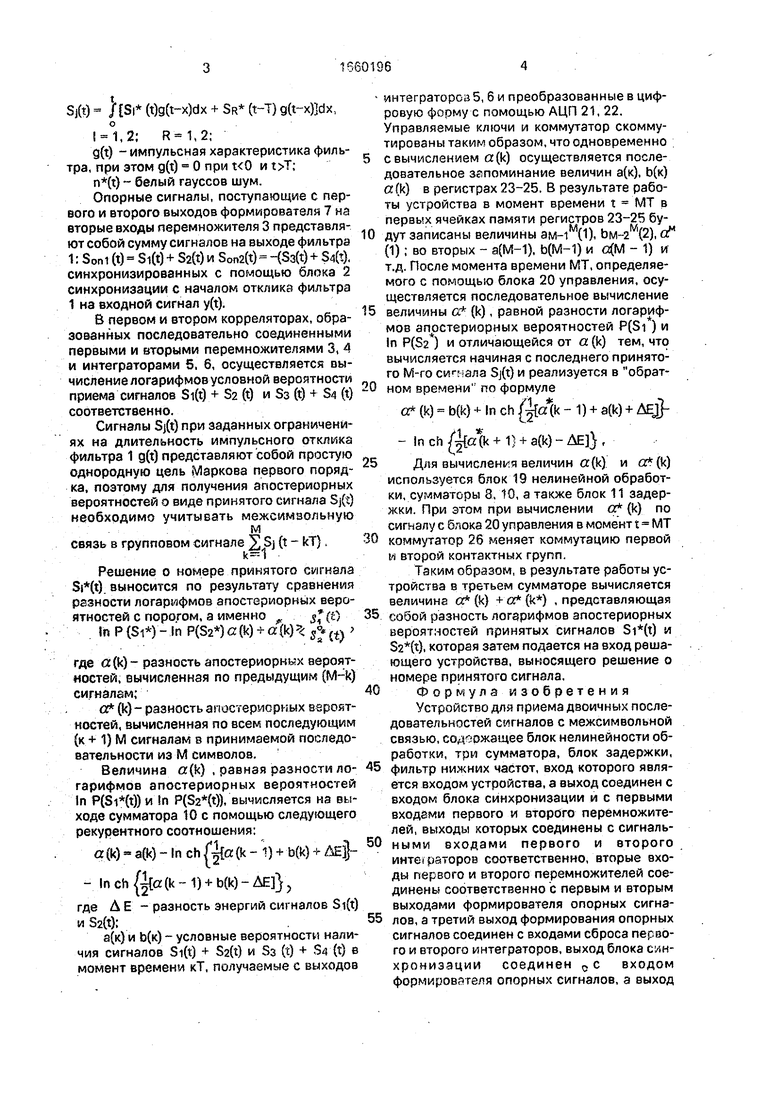

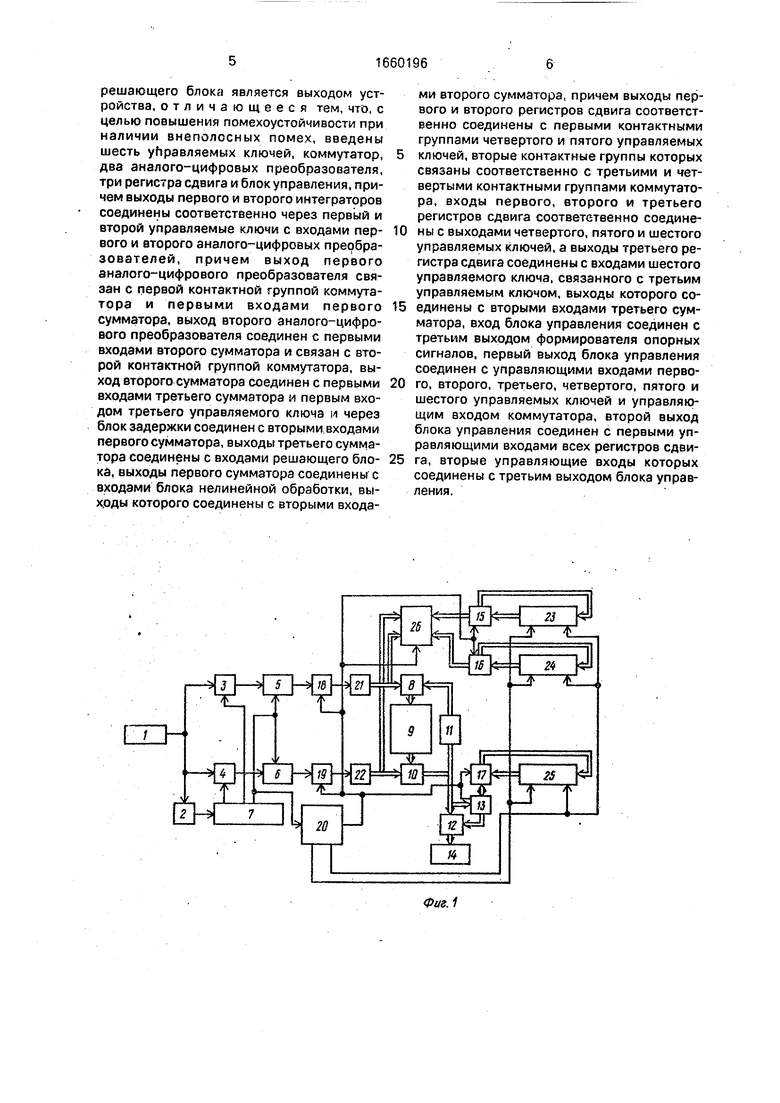

На фиг. 1 изображена структурная схема предложенного устройства: на Лиг. 2 - схема блока управления.

Устройство содержит фильтр 1 нижних частот, блок 2 синхронизации, первый и второй перемножители 3, 4, первый и второй интеграторы 5, 6, формирователь 7 опорных сигналов, первый сумматор 8, блок 9 нелинейной обработки, второй сумматор 10, блок 11 задержки, третий сумматор 12, третий управляемый ключ 13, решающий блок 14, четвертый, пятый, шестой, первый, второй управляемые ключи 15-19, блок 20 управления, первый и второй аналого-цифровые преобразователи (АЦП) 21,22, первый, второй, третий регистры 23- 25 сдвига, коммутатор 26.

Блок 20 управления содержит генератор 27 тактовых импульсов, ключи 28, 29, блок 30 задержки, элемент И 31, счетчик 32.

Устройство работает следующим образом.

Входной сигнал устройства y(t) представляет собой аддитивную смесь последо- вательности из М информационных сигналов Si(t), (i 1,2) длительностью Т, белого гауссового шума n(t) и внеполосной помехи Ј(t)

м .

y(t) 2sr(t-kT) + n(t)Ј(t)

k 1

Проходя через фильтр 1 нижних частот, форма передаточной характеристики которого такова, что спектральная плотность мощности шума и помехи равномерна входной сигнал y(t) преобразуется в сигнал М

y(t) 2Sj (t-кт).

k I

где j 1, 4, а форма Sj(t) определяется как

(Л

С

DS

о о

5 о

Sj(t) (t)g(t-x)dx + SR (t-T) g(t-x)dx,

1-1,2: R-1,2;

g(t) - импульсная характеристика фильтра, при этом g(t) 0 при и

n(t) - белый гауссов шум.

Опорные сигналы, поступающие с первого и второго выходов формирователи 7 на вторые входы перемножителя 3 представляют собой сумму сигналов на выходе фильтра 1: Son 1 (t) Si(t) + S2(t) и Son2(t)-(S3(t) + S4(t), синхронизированных с помощью блока 2 синхронизации с началом отклика фильтра 1 на входной сигнал y(t).

В первом и втором корреляторах, образованных последовательно соединенными первыми и вторыми перемножителями 3, л и интеграторами 5. 6, осуществляется вычисление логарифмов условной вероятности приема сигналов Si(t) + 82 (t) и Ss (t) + 84 (t) соответственно.

Сигналы Sj(t) при заданных ограничениях на длительность импульсного отклика фильтра 1 g(t) представляют собой простую однородную цель sVlapKoea первого порядка, поэтому для получения апостериорных вероятностей о виде принятого сигнала Sj(t)

необходимо учитывать межсимзольную

м связь в групповом сигнале % Sj {t - kT),

Решение о номере принятого сигнала Si(t) выносится по результату сравнения разности логарифмов апостериорных вероятностей с порогом, а именнозГ(0

In Р (81) - In P( a (k) + a(k) s° (

где cc(k)- разность апостериорных вероятностей, вычисленная по предыдущим (M-k) сигналам;

of (k)- разность апостериорных вероятностей, вычисленная по всем последующим (к + 1) М сигналам в принимаемой последовательности из М символов.

Величина сг(к) , равная разности логарифмов апостериорных вероятностей In P(Si(t)) и n P(S2(t)), вычисляется на выходе сумматора 10 с помощью следующего рекурентного соотношения:

a (k) - a(k) - In ch {-{a (k - 1) + b{k) + inchdtadc-IJ + bflO-AE },

где Д E - разность энергий сигналов Si(t) и SaW;

а(к) и Ь(к) - условные вероятности наличия сигналов Si(t) + S2(t) и Ss (t) + 84 (t) в момент времени кТ, получаемые с выходов

интеграторсаб, 6 и преобразованные в цифровую форму с помощью АЦП 21, 22. Управляемые ключи и коммутатор скомму- тированы таким образом, что одновременно

с вычислением ct (k) осуществляется последовательное запоминание величин а(к), Ь(к) a{k) в регистрах 23-25. В результате работы устройства в момент времени t МТ в первых ячейках памяти регистров 23-25 будут записаны величины ам-1М(1), Ьм-2М{2), 0м (1); во вторых - а(М-1), Ь(М-1) и о(М - 1) и т.д. После момента времени МТ, определяемого с помощью блока 20 управления, осуществляется последовательное вычисление

величины a (k), равной разности логарифмов апостериорных вероятностей P(Si ) и In Р($2 ) и отличающейся от a (k) тем, что вычисляется начиная с последнего принятого М-го ,ала Sj(t) и реализуется в обратном времени по формуле

a (k) b(k) In ch /gf«(k - 1) + a(k) + AEJJ- In ch + 1) + a(k) - ДЕ}} ,

Для вычисления величин tt(k) и о (k) используется блок 19 нелинейной обработки, сумматоры 8, 10, а также блок 11 задержки. При этом при вычислении a (k) по сигналу с блока 20 управления в момент

коммутатор 26 меняет коммутацию первой и второй контактных групп.

Таким образом, в результате работы устройства в третьем сумматоре вычисляется величине о (k) + a (k) , представляющая

собой разность логарифмов апостериорных вероятностей принятых сигналов Si(t) и S2(t), которая затем подается на вход решающего устройства, выносящего решение о номере принятого сигнала.

Формула изобретения

Устройство для приема двоичных последовательностей сигналов с межсимвольной связью, содоожащее блок нелинейности обработки, три сумматора, блок задержки,

фильтр нижних частот, вход которого является входом устройства, а выход соединен с входом блока синхронизации и с первыми входами первого и второго перемножителей, выходы которых соединены с сигнальнымм входами первого и второго интв(уаторов соответственно, вторые входы первого и второго перемножителей соединены соответственно с первым и вторым выходами формирователя опорных сигналов, а третий выход формирования опорных сигналов соединен с входами сброса первого и второго интеграторов, выход блока сян- хрониэации соединен с с входом формирователя опорных сигналов, а выход

решающего блок является выходом устройства, отличающееся тем, что, с целью повышения помехоустойчивости при наличии внеполссных помех, введены шесть управляемых ключей, коммутатор, два аналого-цифровых преобразователя, три регистра сдвига и блок управления, причем выходы первого и второго интеграторов соединены соответственно через первый и второй управляемые ключи с входами пер- вого и второго аналого-цифровых преобразователей, причем выход первого аналого-цифрового преобразователя связан с первой контактной группой коммутатора и первыми входами первого сумматора, выход второго аналого-цифрового преобразователя соединен с первыми входами второго сумматора и связан с второй контактной группой коммутатора, выход второго сумматора соединен с первыми входами третьего сумматора и первым входом третьего управляемого ключа и через блок задержки соединен с вторыми входами первого сумматора, выходы третьего сумматора соединены с входами решающего бло- ка, выходы первого сумматора соединены с входами блока нелинейной обработки, выходы которого соединены с вторыми входами второго сумматора, причем выходы первого и второго регистров сдвига соответственно соединены с первыми контактными группами четвертого и пятого управляемых ключей, вторые контактные группы которых связаны соответственно с третьими и четвертыми контактными группами коммутатора, входы первого, второго и третьего регистров сдвига соответственно соединены с выходами четвертого, пятого и шестого управляемых ключей, а выходы третьего регистра сдвига соединены с входами шестого управляемого ключа, связанного с третьим управляемым ключом, выходы которого соединены с вторыми входами третьего сумматора, вход блока управления соединен с третьим выходом формирователя опорных сигналов, первый выход блока управления соединен с управляющими входами первого, второго, третьего, четвертого, пятого и шестого управляемых ключей и управляющим входом коммутатора, второй выход блока управления соединен с первыми управляющими входами всех регистров сдвига, вторые управляющие входы которых соединены с третьим выходом блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема двоичных сигналов | 1988 |

|

SU1573551A1 |

| Устройство для приема двоичных сигналов с непрерывной фазовой модуляцией | 1989 |

|

SU1753617A1 |

| Устройство для приема цифровых сигналов с непрерывной фазовой модуляцией | 1989 |

|

SU1690211A1 |

| Устройство для приема двоичных сигналов | 1989 |

|

SU1709550A1 |

| Устройство для приема двоичных сигналов | 1986 |

|

SU1406812A1 |

| Адаптивный ранговый обнаружитель | 1979 |

|

SU800927A2 |

| Устройство для оценки параметров многолучевого канала связи | 1991 |

|

SU1781828A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ДИСКРЕТНЫХ СИГНАЛОВ | 2012 |

|

RU2480839C1 |

| Анализатор сигнала тактовой синхронизации | 1988 |

|

SU1587656A1 |

| Анализатор сигнала тактовой синхронизации | 1990 |

|

SU1781834A2 |

Изобретение относится к приемопередающей технике. Цель изобретения - повышение помехоустойчивости при наличии внеполосных помех. Устройство содержит фильтр 1 нижних частот, блок 2 синхронизации, перемножители 3 и 4, интеграторы 5 и 6, формирователь 7 опорных сигналов, сумматоры 8, 10 и 12, блок 9 нелинейной обработки, блок 11 задержки, управляемые ключи 13, 15 - 19, решающий блок 14, блок 20 управления, АЦП 21 и 22, регистры 23, 24 и 25 сдвига и коммутатор 26. Цель достигается за счет вычисления величины, представляющей собой разность логарифмов апостериорных вероятностей принятых сигналов, по которой затем решающий блок 14 выносит решение о номере принятого сигнала. 2 ил.

ОНФиг.2

| Устройство для приема двоичных сигналов | 1987 |

|

SU1506577A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-06-30—Публикация

1988-12-01—Подача