Изобретение относится к технике связи и может быть использовано для когерентной обработки двоичных дискретных сигналов.

Цель изобретения - повышение достоверности приема сигналов в частот- но-эграниченных каналах с межсимвольной интерференцией и высоким уровнем аддитивных помех.

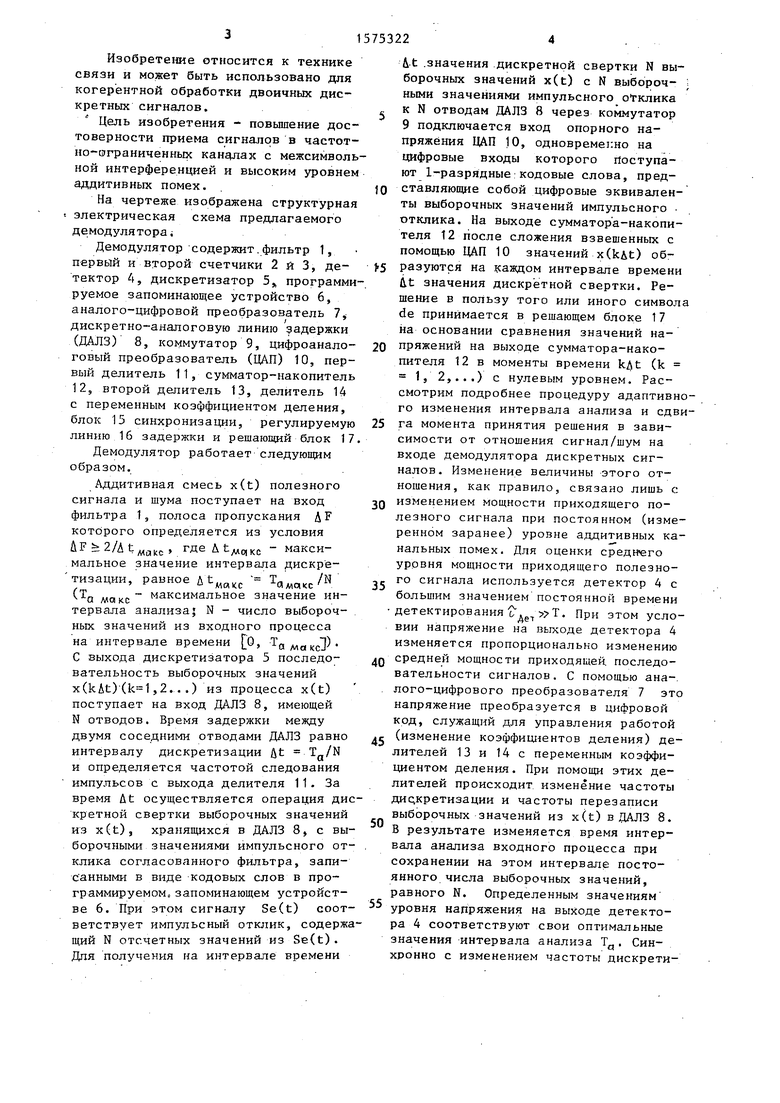

На чертеже изображена структурная электрическая схема предлагаемого демодулятора.

Демодулятор содержит фильтр 1, первый и второй счетчики 2 и 3, детектор 4, дискретизатор 5„ программируемое запоминающее устройство 6, аналого-цифровой преобразователь 7, дискретно-аналоговую линию задержки (ДАЛЗ) 8, коммутатор 9, цифроанало- говый преобразователь (ЦАП) 10, первый делитель 11, сумматор-накопитель 12, второй делитель 13, делитель 14 с переменным коэффициентом деления, блок 15 синхронизации, регулируемую линию 16 задержки и решающий блок 17

Демодулятор работает следующим образом.

Аддитивная смесь x(t) полезного сигнала и шума поступает на вход фильтра 1, полоса пропускания ДР которого определяется из условия UFb2/AtMakc, rfleAt dKc - максимальное значение интервала дискре- тизации, равное AtMBV,c TaMqlcc/N (TQ макс максимальное значение интервала анализа; N - число выборочных значений из входного процесса

на интервале времени

О, Т

а АИ а кс

д

С выхода дискретизатора 5 последовательность выборочных значений x(kAt)(,2...) из процесса x(t) поступает на вход ДАЛЗ 8, имеющей N отводов. Время задержки между двумя соседними отводами ДАЛЗ равно интервалу дискретизации ftt Ta/N и определяется частотой следования импульсов с выхода делителя 11. За время At осуществляется операция дикретной свертки выборочных значений из x(t), хранящихся в ДАЛЗ 8, с выборочными значениями импульсного отклика согласованного фильтра, записанными в виде кодовых слов в программируемом запоминающем устройстве 6. При этом сигналу Se(t) соответствует импульсный отклик, содержщий N отсчетных значений из Se(t). Для получения на интервале времени

5

0

5

0

5

0

5

0

5

At значения дискретной свертки N выборочных значений x(t) с N выборочными значениями импульсного отклика к N отводам ДАЛЗ 8 через коммутатор 9 подключается вход опорного напряжения ЦАП 10, одновременно на цифровые входы которого йоступа- ют 1-разрядные кодовые слова, представляющие собой цифровые эквиваленты выборочных значений импульсного отклика. На выходе сумматора-накопителя 12 после сложения взвешенных с помощью ЦАП 10 значений x(kit) образуются на каждом интервале времени it значения дискретной свертки. Решение в пользу того или иного символа de принимается в решающем блоке 17 на основании сравнения значений напряжений на выходе сумматора-накопителя 12 в моменты времени (k 1, 2,...) с нулевым уровнем. Рассмотрим подробнее процедуру адаптивного изменения интервала анализа и сдвига момента принятия решения в зависимости от отношения сигнал/шум на входе демодулятора дискретных сигналов. Изменение величины этого отношения, как правило, связано лишь с изменением мощности приходящего полезного сигнала при постоянном (измеренном заранее) уровне аддитивных канальных помех. Для оценки среднего уровня мощности приходящего полезного сигнала используется детектор 4 с большим значением постоянной времени детектирования . При этом условии напряжение на выходе детектора 4 изменяется пропорционально изменению средней мощности приходящей последовательности сигналов. С помощью аналого-цифрового преобразователя 7 это напряжение преобразуется в цифровой код, служащий для управления работой (изменение коэффициентов деления) делителей 13 и 14 с переменным коэффициентом деления. При помощи этих делителей происходит изменение частоты дискретизации и частоты перезаписи выборочных значений из x(t) в ДАЛЗ 8. В результате изменяется время интервала анализа входного процесса при сохранении на этом интервале постоянного числа выборочных значений, равного N. Определенным значениям уровня напряжения на выходе детектора 4 соответствуют свои оптимальные значения интервала анализа Тд. Синхронно с изменением частоты дискрети51

эации происходит и изменение частоты подключения отводов ДАЛЗ 8 с помощью коммутатора 9 к входу опорного напряжения ЦАП 10. Все возможные формы импульсных откликов дискретно-аналогового согласованного фильтра, соответствующие определенным значениям интервалов анализа Та, записаны в виде 1-разрядных кодовых слов в программируемом запоминающем устройстве 6, причем каждая форма отклика представлена N значениями чисел. Выбор той или иной формы импульсного отклика из памяти программируемого запоминающего устройства 6 осуществляется с помощью,n-разрядного кода, поступающего на третьи входы программируемого запоминающего устройства 6. Каждому n-разрядному числу соответствует своя область памяти программируемого запоминающего устройства 6, где записаны значения импульсного отклика для данного интервала анализа Та. С выходов программируемого запоминающего устройства 6 1-разрядные числа поступают на цифровые входы ЦАП 10, на выходе которого получаются значения результатов синхронного перемножения выборочных значений x(t) с выходов ДАЛЗ и выборочных значений импульсного отклика, хранящихся в программируемом запоминающем устройстве 6. С помощью сумматора-накопителя 12 суммируются N значений результатов перемножения указанных напряжений, и на выходе сумматора-накопителя 12 формируется значение дискретной свертки входного процесса x(t) с соответствующим импульсным откликом на интервале анализа TQ. Такое фор- мировалие значений дискретной свертки осуществляется на каждом интервале времени &t. В соответствии с алгоритмом работы решающий блок 17 производит анализ полярности этого напряжения в момент времени t0+Ta. Смещение интервала анализа осуществляется с помощью регулируемой линии 16 задержки. Изменение времени задержки последовательности импульсов с третьего выхода блока 15 синхронизации осуществляется с помощью п-раз- рядного кода, поступающего с выходов аналого-цифрового преобразователя 7.. Регулируемая линия 16 задержки может быть выполнена, например, на основе аналоговой линии, к отводам которой

5755226

подключены ключи, управляемые дешифраторами.

0

5

0

5

Формула изобретения

Демодулятор дискретных сигналов, содержащий последовательно соединенные фильтр, вход которого является входом демодулятора, дискретизатор и дискретно-аналоговую линию задержки, управляющие входы которых подключены к выходу первого делителя, первый и второй счетчики, причем вход второго счетчика соединен с входом первого делителя, коммутатор, второй делитель, программируемое запоминающее устройство, решающий блок, блок синхронизации, последовательно соединенные цифроаналоговый преобразователь и сумматор-накопитель, причем N первых входов коммутатора соединены с выходами дискретно-аналоговой линии задержки, р вторых входов подключены к р выходам второго счетчика, а выход соединен с входом опорного напряжения цифроаналогового преобразователя, 1 входов которого подключены к 1 выходам программируемого запоминающего устройства, первые р входов которого подключены к р выходам второго счетчика, а вторые m входов соединены с m выходами первого счетчика, первый выход блока синхронизации соединен с соответствующим входом второго делителя, отличающийся тем, что, с целью повышения достоверности приема сигналов в частотно- ограниченных каналах с межсимвольной интерференцией и высоким уровнем аддитивных помех, второй делитель выполнен с переменным коэффициентом деления и введены последовательно соединенные детектор и аналого-цифровой преобразователь, делитель с переменным коэффициентом деления, регулируемая линия задержки, выход которой подключен к управляющему входу решающего блока, первый вход - к второму выходу блока синхронизации, а п вторых входов - к п выходам аналого-цифрового преобразователя, которые также подсоединены к третьим п входам программируемого запоминающего устройства и к п входам второго делителя и делителя с переменным коэффициентом деления, причем соответствующий вход делителя с переменным коэффициентом деления подключен к третьему выходу блока синхронизации,

0

5

0

5

0

5

715753228

а выход второго делителя подключен к чика и управляющему входу сумматора- входу первого делителя, выход делите накопителя, выход которого соединен с ля с переменным коэффициентом де- входом решающего блока, выход; фнльтления подключен к входу первого счет-- ра соединен с входом детектора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Перестраиваемый демодулятор дискретных сигналов | 1986 |

|

SU1401637A1 |

| Цифровой согласованный фильтр | 1980 |

|

SU944077A1 |

| ЦИФРОВОЕ УСТРОЙСТВО ФОРМИРОВАНИЯ СПЕКТРАЛЬНО-ЭФФЕКТИВНЫХ СИГНАЛОВ | 2012 |

|

RU2498515C1 |

| Демодулятор дискретных сигналов | 1979 |

|

SU788429A1 |

| Устройство для поиска шумоподобного сигнала | 1984 |

|

SU1277415A1 |

| Устройство для измерения диаграммы направленности антенны | 1990 |

|

SU1707573A1 |

| ЦИФРОВОЙ СОГЛАСОВАННЫЙ ФИЛЬТР СИГНАЛОВ С ДИСКРЕТНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1992 |

|

RU2114514C1 |

| Цифровой фазовый детектор | 1982 |

|

SU1064421A1 |

| СИНТЕЗАТОР ЧАСТОТ | 2015 |

|

RU2595629C1 |

| Многоканальный имитатор канала магнитной записи | 1990 |

|

SU1767529A1 |

Изобретение относится к технике связи. Цель изобретения - повышение достоверности приема сигналов в частотно-ограниченных каналах с межсимвольной интерференцией и высоким уровнем аддитивных помех. Демодулятор дискретных сигналов содержит фильтр 1, счетчики 2 и 3, дискретизатор 5, программируемое запоминающее устройство 6, дискретно-аналоговую линию задержки 8, коммутатор 9, ЦАП 10, делитель 11, сумматор-накопитель 12, делитель 13 с переменным коэф. деления, блок синхронизации 15, решающий блок 17. Цель достигается введением детектора 4, АЦП 7, делителя 14 с переменным коэф. деления и регулируемой линии задержки 16, с помощью которых решается задача адаптивного изменения интервала анализа и сдвига момента принятия решения в решающем блоке 17 в зависимости от отношения сигнал/шум на входе демодулятора. 1 ил.

| Перестраиваемый демодулятор дискретных сигналов | 1986 |

|

SU1401637A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-06-30—Публикация

1988-01-12—Подача