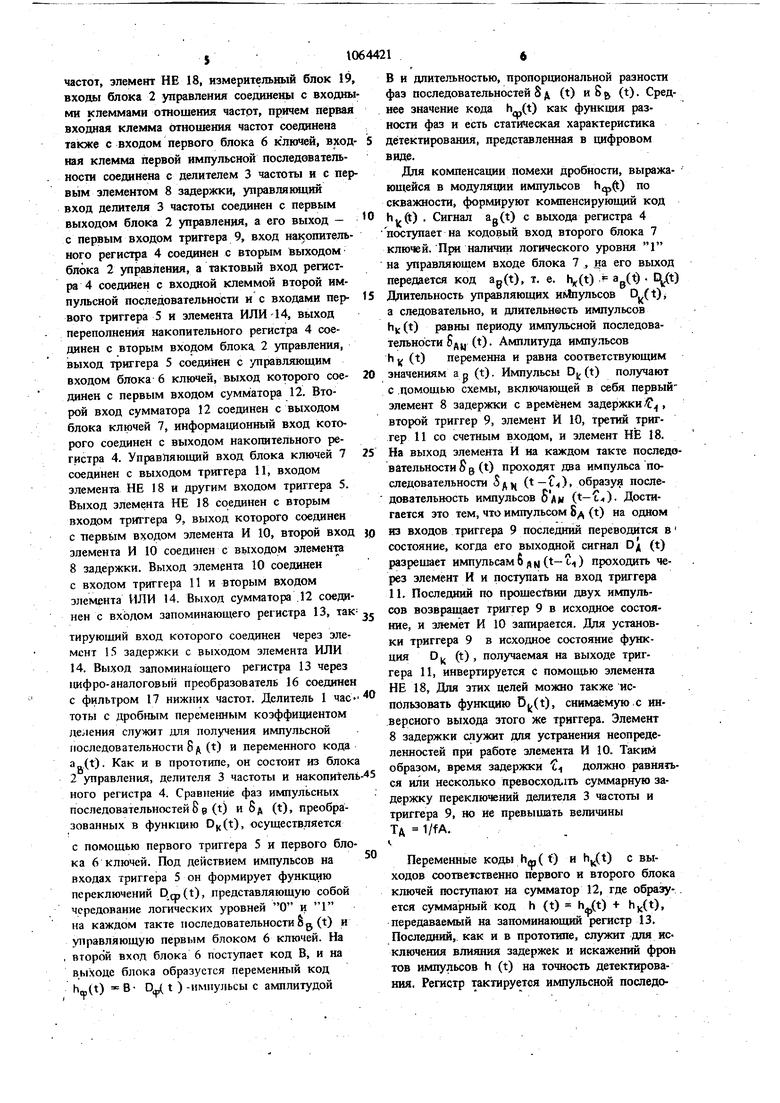

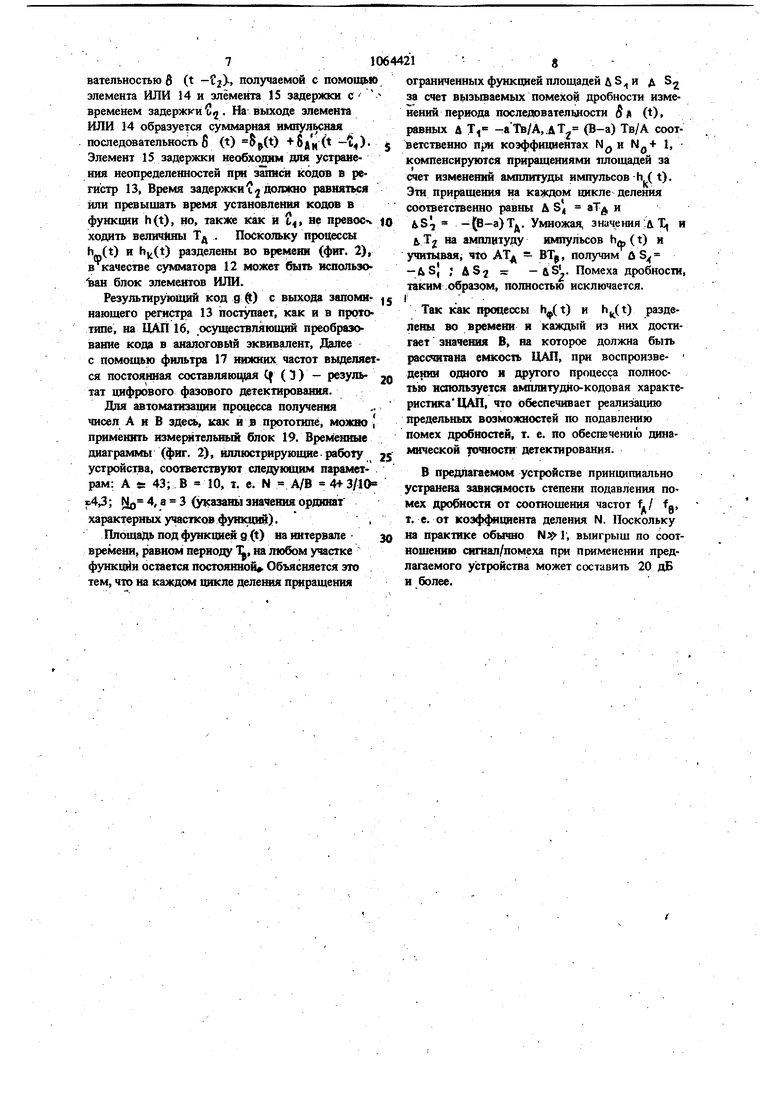

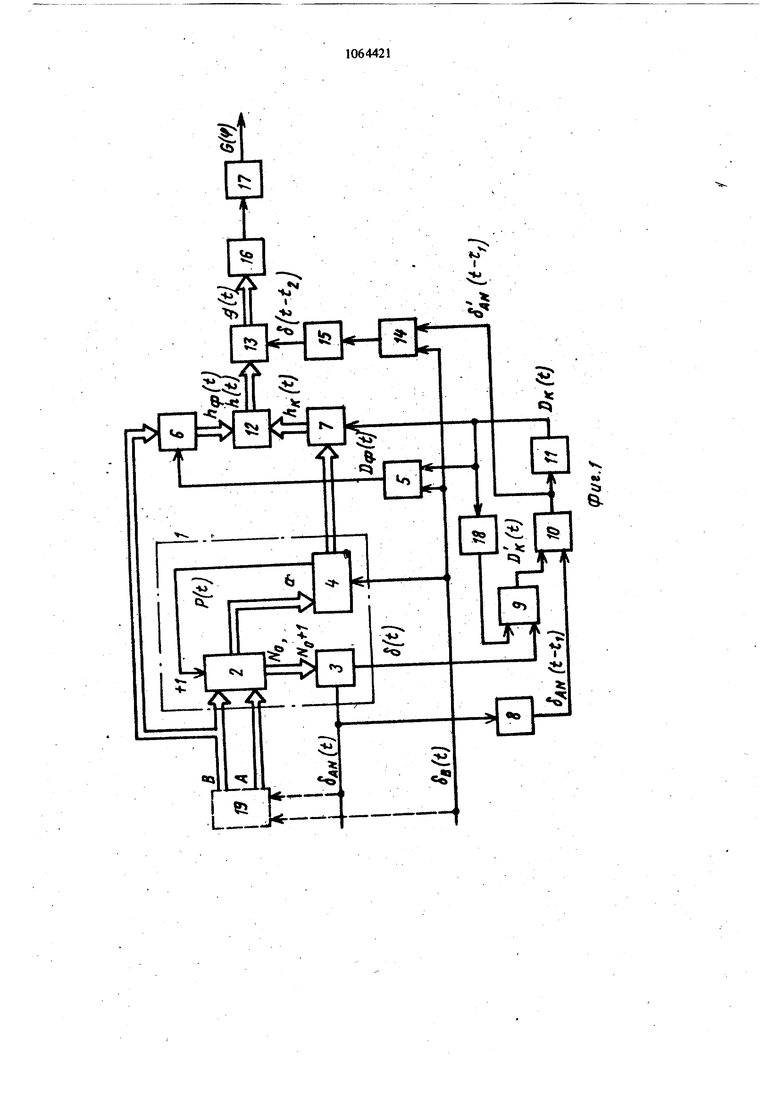

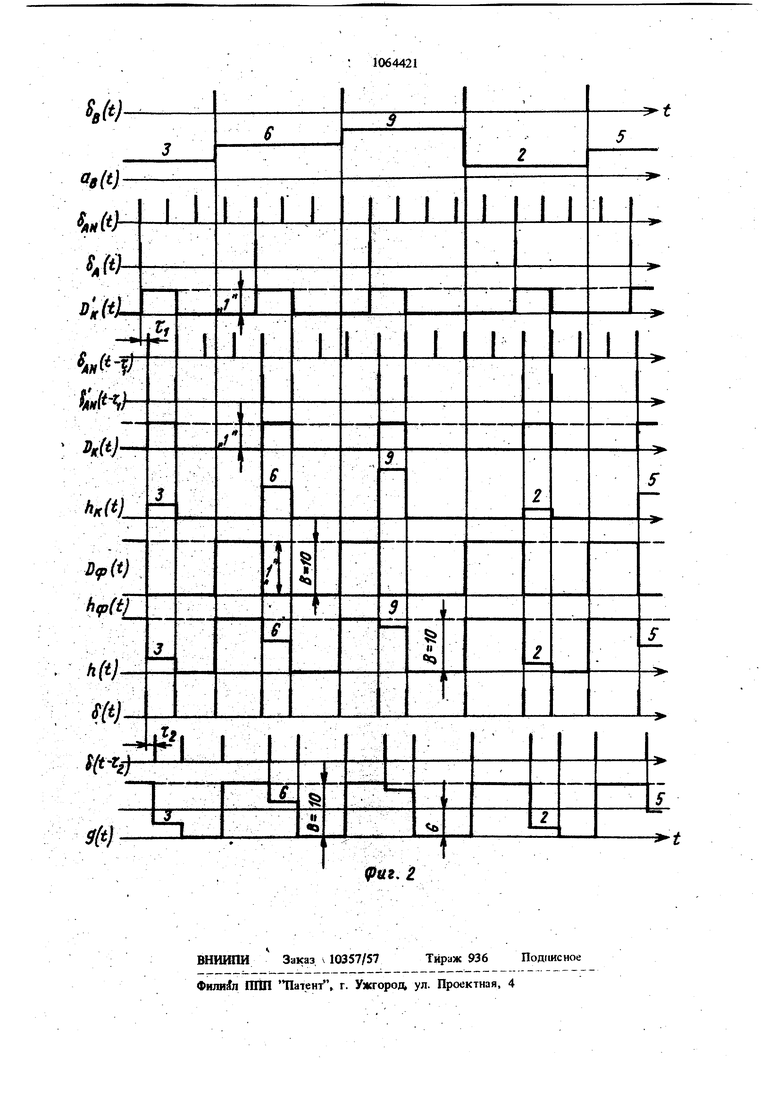

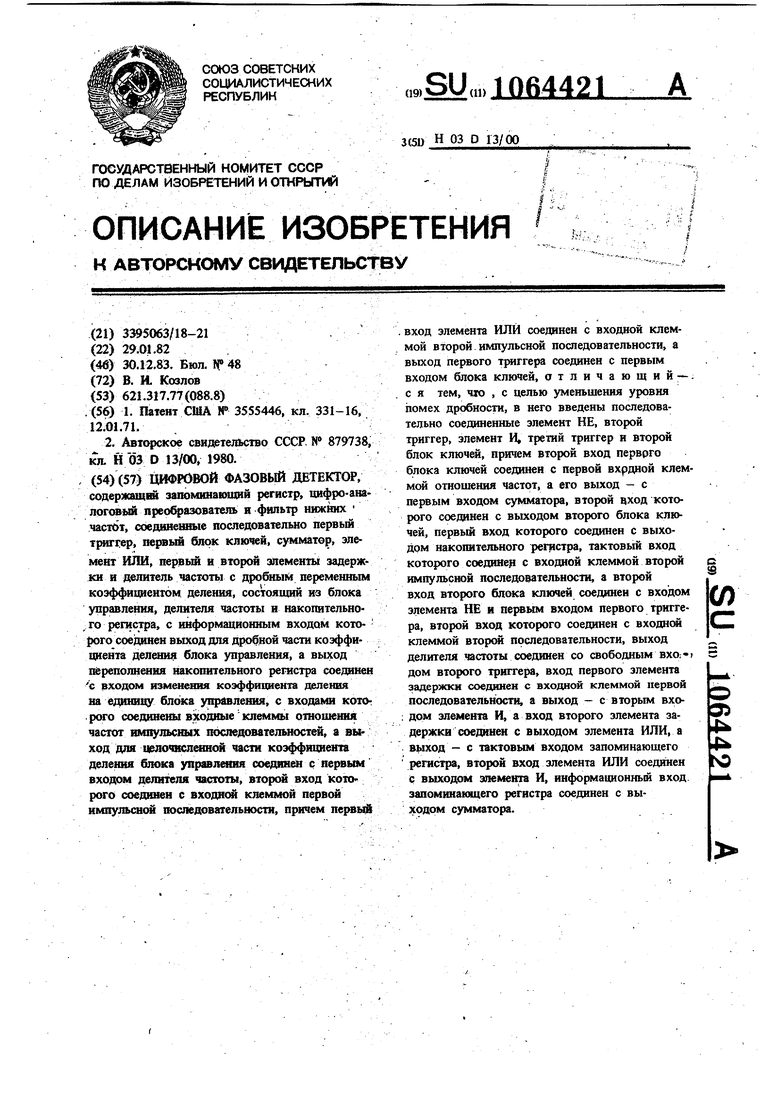

Изобретение относится к радиотехнике, а именно к технике цифрового фазового детекти рования на неравных частотах, и может быть использовано для детектирования радиосягаалов с угловой модуляцией, для получения сигнале рассогласования в системах АПЧ, для формирования сетки стабильных частот в пртемоперелающей и измерительной аппаратуре н в ряде других случаев..-.. Известно устройство сщфрового фазсюого детектирования, содержащее фазовый детектор, сумматор и Делитель, в котором частоты приводят к равенству путем деления большей из них в дробное число N раз, получаемое за счет чередования целочисленных коэф пшен1ов, например, N и NQ+ 1 Появляющаяся в результате фазового детектирования помеха дробности компенсируется за счет противофазного суммирования сигнала фазового рассогласования с преобразованным в аналоговую форму процессом накопления дробной части козффи циентЗ деления N 1. . Однако из-за ограниченных возможностей аналоговой компенсации по точности схема практически не прнментля для получения требуемых соотношений сигнал/помеха более 40 дБ. Наиболее близким к предлагаемому является устройство с цифровой компенсацией помех дробности, содержащее делитель частоты с дроб ным перемениьпл козффициентом деления (ДПКД), сумматор, блок ключей, зшюминаАщи регистр, цифро-аналоговый преобразователь (ЦАП), фильтр нижних частот (ФНЧ), триггер, ИЛИ и три элемента задержки {2}. Входь блока управления соединены с входаы ми клеммами отношения частот, а выхода бло .ка управления соединены с входом делителя част.оты и накопительного регистра, выход переноса которого соединен с управляющим входом блока управления, а кодовый выход - с входом сумматора и блока ключей. Первъ1й вход сумматора соединен с пё{юой входной клеммой отношения астот, а выход сумматора соединен с вторым входом блока ключей. Выход блокам ключей соединен с информацишным входом запоминающего регистра, а выход последнего соединен с входом цифро-анаголового преобразо вагеля. При этом выход ЦАП соединен с входом ФНЧ. Вход делителя частоты соединен с входной клеммой первой импульсной последовательности, а выход делителя соединен с такта руюшим входом накопительного регистра через первый злемент задержки. Вход первого . элемента задержки соединен с входом второго элемента задержки и первым,входом злемеша И Л И.Второй вход элемента ИЛИ соединен с входной клеммой второй импульсной последовательности и с входом третьего элемента задержки. Выходы второго и третьего элементов задержки соединены с входами триггера, выход которого (оедииеи с управляющим входом блока ключей, а выход элемента ИЛИ соединен с тактирующим входом запоминающего регистра. Работа известного устройства основана на деления брльщей из сравниваемых частот в дробное число раз N А/В, где А и В - целые числа, пропорциональные соответствующим частотам f и f g соответственно импульсных послед жательностей6цц(1) и SB (t), путем изменения целочисленного коэффициента деления. Для этого импульсную последовательиость бд(1), лолученную в результате уменьщения частоты f в N раз, преобразовьюают в цифровой код а (t)/, возрастающий с каждым им пульсом на величину а, равную числителю дроби а/В, составляющей дробную часть коэффициента N, пока ад(1) не достигнет значения А.., равного или большего В, после чего коэффициент деления изменяют на единицу на время одг кого цикла деления, а код уменьщают на величину В и дальнейщее его изменение происходит начиная с разности . Одновременно с этим формирую т КОД a.(t) суммированием ад (t) и А, получают жгнш1 фазового рассогласования g (t) в цифровом виде, поочередно запоминая .мгновенные значения a(t) и ) в моменты появления импульсов последовательностей 8 д (t) и 8 в () таким образом, что очередное значение a(t) существует с момента появления очередного импульса последовательности Sa(t) до момента появления очередного импульса последовательностиS 1 (t), а ag(t) на остальных интервалах времени. Затем код g (t) преобразовывают в аналоговую форму и усредняют результат преобразования. Блок управления вырабатывает коды N (с возможностьюИзменения на единицу) и а, поступающие соответственно иа управляющий ход делителя и на информационный вход накоительного регистра. ДШКД служит для получе01Я импульсной последовательности 8 д (t) и еременного кода я (t). Суммирование кодов .{t) и А осуществляется ёумматором. Получен ый таким образом код a(t) совместно с коом a.(t) поступает на блок ключей, управляюий вход которого подключен к выходу RSjMirrepa. Триггер управляет ключами таким образом, что код а Q (t) передается на запоминающий регистр после прихода очередного импульса 89(1), а код a(t) - после прихода очередного мпульса 8 ц (t). Так формируется код А (t) на информационном входе запоминающего регистра. Дйя получения кода (t ) мгновенные значения кода A(t ) записываются в запоминающем регистре с помощью суммы последовательностей BiiCt) H6a(t), выделяемой на выходе элемента ИЛИ и подаваемой на тактовый вход регистра. Элементы задержек введены для устранения неопределенностей при записи мгновенных значеннй кода A(t ) в регистр. Времена задержек выбираются такими, чтобы момент записи в регистр не попадал в интервал переходных процессов на его информационном входе, С приходом на тактовый вход регистра импульса последовательности S g (t ) записьшается значение кода a(t ), которое сохраняется до прихода импульса бд(1), после чего записьтается значение кода ад (t ), и т. д. Полученный таким образом переменный код (t ) поступает на ЦАП, где преобразо вывается в аналоговую форму. Фильтр нижних частот вьщеляет постоянную составляющую Cj (5), являющуюся результатомдетектиров ния. Ее величина линейно зависит от зквиваленшой разности фаз исхрдных импульсных последовательностей В (t ) и 8 ц (t ), Возможности ЦАП при этом используются не полностью, что объясняется следующими причинами.Результирующий код на выходе запоминающего регистра может быть представлен в виде суммы фазового и компенсирующего кодов, т. е. g (t ) g(t ) +g,(t ). Без учета сдвига по времени фазовый код q(t ) представляет собой результат перемно жения числа А с функвдей переключений D(t) RS-триггера, а компенсирующий- (t) s - 2|v (t). Максимальные значения этих кодов соответственно равны А и В, т, е отличаются в N раз. Очевидно, что точность компенсащш помех на выходе ЦАП будет тем выше, чем большую долю составляет jj(t) в общем Процессе (t), поскольку при этом уменьщается доля погрешности, вносимая преобразователем. В общем случае коэффициент Nимеет широкий диапазон значений и обычно на практике N 1 , так что недоиспользование ампли-, тудно-кодовой характеристики ЦАП для ком-/ пенсацки помех дробности оказывается весьма существенным. Таким образом, недостапсом известного устройства является достаточно высокий уровень помех дробности. Цель изобретения - уменьшение уровня помех дробности, Поставленная - цель достигается тем, что в цифровой ;фазовый детектор, содержащий запоминающий регистр, цифро-аналоговый преобразователь и фильтр нижних частот, соединенные последовательно первый триггер, первый блок ключей, сумматор, элемент ИЛИ, первый и второй элементы задержки и делитель частоты с дробным переменным коэффициентом деления, состоящий из блока управления, делителя частоты и накопительного регистра, с информационным входом которого соединен выход для щюбной .части коэффициента деления блока управления, а выход переполнения накопительного регистра соединен с входом изменения коэффициента деления на единицу блока управления, с входами которого соединены : входные клеммы отношения частот импульсных последовательностей, а выход для целочисленной части коэффициента деления блока управления соединён с первым входом делителя частоты, второй вход которого соединен с входной клеммой первой импульсной последовательности, причем первый вход элемента ИЛИ соединен с входной клеммой второй импульсной последовательности, а выход первого триггера соединен с первым входом первого блока ключей, введены последовательно соединенные элемент НЕ , второй триггер, элемент И, третий триггер и второй блок ключей, причем второй вход первого блока ключей соединен с первой входной клеммой отношения частот, а его, выход - с первым входом сумматора, второй вход которого соединен с- выходом второго блока ключей, первый вход которого соединен с выходом накопительного регистра, тактовый вход которого соединен с, входной клеммой йторой импульсной последовательности, а второй вход второго блока ключей соединен с входом элемента НЕ и первым входом первого триггера, второй вход которого соединен с входной клеммой вторюй последовательности, выход делителя частоты соединен со свободным входом второго триггера, вход первого элемента задержки соединен с входной клеммой первой последовательности, а выход - с вторым вхо-. дом элемента И, а вход второго элемента задержки соединен с выходом элемента ИЛИ, а выход - с тактовым входом запоминающего регистра, второй вход элемента ИЛИ соединен с выходом элемента И, информаци-. онный вход запоминающего регистра соединен с выходом сумматора. На фиг. 1 приведена структурная схема фазового детектора; на фиг. 2 - временные диаграммы работы.v Устройство содержит делитель 1 частоты с дробным переменным коэффициентом деления, блок 2 управления, делитель 3 частоты, накопительный регистр 4, первый триггер 5, первый блок 6 ключей, второй блок 7 ключей, первый элемент 8 задержки, второй триггер 9, элемент И 10, третий триггер 11, сумматор 12, ; запоминающий регистр 13, элемент ИЛИ 14, второй элемент 15 задержки, цифро-аналоговый преобразователь (ЦАП) 16, фильтр 17 нижних частот, элемент НЕ 18, измерительный блок 19 входы блока 2 управления соединены с входны ми клеммами отношения частот, причем первая входная клемма отношения частот соединена также с входом первого блока 6 ключей, вход ная клемма первой импульсной последовательности соединена с делителем 3 частоты и с пер вым элементом 8 задержки, управляниций вход делителя 3 частоты соединен с первым выходом блока 2 управления, а его выход - с первым входом триггера 9, вход нак опитель ного регистра 4 соединен с вторым выходом блока 2 управления, а тактовый вход регистра 4 соединен с входной клеммой второй импульсной последовательности и с входами первого триггера 5 и элемента ИЛИ 4 4, выход переполнения накопительного регистра 4 соединен с вторым входом блока. 2 управления, выход триггера 5 соедийен с управляющим входом блока 6 ключей, выход которого соединен с первым входом сумматора 12. Второй вход сумматора 12 соединен с выходом блока ключей 7, информационный вход которого соединен с выходом накопительиого регистра 4. Управляющий вход блока ключей 7 соединен с выходом триггера 11, входом элемента НЕ 18 и другим входом триггера 5. Выход элемента НЕ 18 соединен с вторым входом триггера 9, выход которого соединен с ттервьгм входом элемента И 10, второй вход элемента И 10 соединен с выходом элемента 8 задержки. Выход элемента 10 соединен с входом триггера 11 и вторым входом элемента ИЛИ 14. Выход сумматора .12 соединен с входом запоминающего peiHcrpa 13, так тирующии вход которого соединен через элемент 15 задержки с выходом элемента ИЛИ 14. Выход запоминающего регистра 13 через цифро-аналоговый преобразователь 16 соединен с фильтром 17 нижних частот. Делитель 1 час тоты с дробным nepeMeifflbiM коэффициентом деления служит для получения импульсной последовательности 8 д (t) и переменного кода а (t). Как и в прототипе, он состоит из блока 2 управления, делителя 3 частоты и накопиТел ного регистра 4. Сравнение фаз импульсных последовательностей 8 р (t) и 8 д (t), преобразованных в функцию D|{(t), осуществляется с помощью первого триггера 5 и первого блока 6 ключей. Под действием импульсов на входах триггера 5 он формирует функцию переключений Dm{t), представляющую собой чередование логических уровней О и 1 па каждом такте последовательности & g (t) и управляющую первым блоком 6 ключей. На , второй вход блока 6 поступает код В, и на выходе блока образуется переменный код h(t) В- D t ) -импульсы с амплитудой В и длительностью, пропорциональной разности фаз последовательностей S д (t) и S (t). Среднее значение кода h (t) как функция разности фаз и есть статическая характеристика детектирования, представленная в цифровом виде. Для компенсации помехи дробности, выражающейся в модуляции импульсов Нф) по скважности, формируют компенсирующий код (t) , Сигнал ag(t) с выхода регистра 4 поступает на кодовый вход второго блока 7 ключей. TIjfM наличии логического уровня 1 на управляющем входе блока 7 , на его выход передается код ag(t), т. е. lv(t) 3(1) . ) Длительность управляющих иШульсов (.)i а следовательно, и длительность импульсов h(.(t) равны периоду импульсной последовательности 6 д, (t). Амплитуда импульсов h (t) переменна и равна соответствующим значениям зр (t). Импульсы D, (t) получают с помощью схемы, включающей в себя первыйэлемент 8 задержки с временем задержки , второй триггер 9, элемент И 10, третий триггер 11 со счетным входом, и элемент НЕ 18. На выход элемента И на каждом такте последовательности о g (t) проходят два импульсапоследовательности §дц (t-f), образуя последовательность импульсов ОАЦ (t-1)). Достигается это тем, что импульсом 8д (t) на одном из входов триггера 9 последний переводится в состояние, когда его выходной сигнал Од (t) разрешает импульсам S д (t-ц) проходить через элемент И и поступать на вход триггера И- Последиий по прошес1вии двух импульсов возвращает триггер 9 в исходное состояние, и элемет И 10 запирается. Для установки триггера 9 в исходное состояние функция D j (t) , получаемая на выходе триггера 11, инвертируется с помощью элемента НЕ 18, Для этих целей можно также испбльзовать функцию Oj,(t), снимаемую.с инверсиого выхода этого же триггера. Элемент 8 задержки служит для устраиения неопределенностей при работе элемента И 10. Таким образом, время задержки с должно равияться или несколько превосход.1ть суммарную задержку переключений делителя 3 частоты и триггера 9, но не превышать величины ТА 1/fA. Переменные коды Нд, ( f) и h( t) с выходов соответственно первого и второго блока ключей поступают на сумматор 12, где образу- . ется суммарный код h (t) h.j(t) + h,(t), передаваемый на запоминающий регистр 13. Последний, как и в прототипе, служит для ис ключения влияния задержек и искажений фрон тов импульсов h (t) иа точность детектирования. Регистр тактируется импульсной последовательностью 8 (t -С)-, получаемой с помощью элемента ИЛИ 14 и элемента IS задержю С временем задержки { ij . На выходе элемента ИЛИ 14 образуется суммарная нмпульсная последовательность 8 (t) S(t) 8дц(t -t). Элемент 15 задержкн необходим для устранения неопределенностей прк зшшси кодов в регнстр 13, Время задержки должно равняться йлн превышать время установления кодов в функции h(t), но, также как и t, не превос ч ходить величины Тд . Поскольку процессы h (t) и h(t) разделены во временя (фиг. 2), в качестве сумматора 12 может быть использо ван блок элементов ИЛИ.

Результирующий код g $) с выхода эапомиг нающето регистра 13 поступает, как и в прототипе, на ЦАП 16, осуществляющий преобразование кода в аналоговый эквивалент. Далее с помощью фильтра 17 нижних частот вьщеляется постоянная составляюцшя (f (tl) - результат цнфрового фазового детектирования.

Для автомапгзацнн процесса получения .. чисел А н В здео, как и в прототипе, можно , пртмешяь изме жтельный блок 19. Временные диаграммы (фиг. 2), иллюстрирующие. работу устройства, соответствуют следующим парамет- . рам: А fc 43; В 10, т. е. N А/В 4+3/10 4, а 3 (у1сазаны значения ординат харшстерных участков функщ1Й).,

Площадь под функш ей g (t) на интервале времени, равн(яи1 периоду L, на любом участке функции остается постоянной Объясняется это тем, что на каждом цикле делешш пртращения

ограниченных функцией площадей д8 и д S за счет в юьгааемых помехой дробности нзмененнй периода последователыюсти $ д (t), Д Т -а1Ъ/А,.дТ2 (В-а) Тв/А соответственно при коэффициентах N и 1, компенсируются пртфащеииями площадей за счет изменений амплитуды импульсов h ( t). Эти приращення на каждом цикле деления соответственно равны Л S аТ и 487 -(В-а)Тд. Умножая, значения :а. Т, и Т на амплитуду импульсов Нф(1) и учитывая что АТд ВТр, получим fl S - &s| ; uSj - - uS. Помеха дробности, такнм,образом, полностью нсключается.

Так как процессы h(t) и h(t) разделены во времени и каждый из них достигает значения В, на которое должна быть рассчитана емкость ЦАП, при воспронзведеяии одного и другого процесса полностью используется амплитудно-кодовая характеристика ЦАП, что обеспечивает реализацию предельных возможностей по подавлению помех дробностей, т. е. по обеспечению динамической точности детектирования.

В предлагаемом устройстве принципиально устранена завна1мость степени подавления помех дробности от соотношення частот f./

В

т. е. от козф циента деления N. Поскольку на практике обычно N:i 1, выигрыш по соотнощению сигнал/помеха при применении предлагаемого устройства может составить 20 дБ и более.

:s

0ыг, 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазовый детектор | 1980 |

|

SU892654A1 |

| Способ цифрового фазового детектирования импульсных последовательностей на неравных частотах и устройство для его осуществления | 1979 |

|

SU879738A1 |

| Цифровой синтезатор частоты | 1987 |

|

SU1515364A1 |

| Цифровой фазовый детектор | 1980 |

|

SU898588A1 |

| Цифровой фазовый детектор | 1980 |

|

SU875303A1 |

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1981 |

|

SU1109872A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1068838A1 |

| Синтезатор частот | 1986 |

|

SU1394434A1 |

| Синтезатор частот | 1986 |

|

SU1376242A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1149394A1 |

ЦИФРОВОЙ ФАЗОВЫЙ ДЕТЕКТОР, содержащга запоминающий регистр, цифро-аналрг юмй прео азователь и фильтр нижних частот, соединенные последовательно первый тртггер, первый блок ключей, сумматор, элемент ИЛИ, первьй и второй элементы задержг ки и делитель частоты с дробным переменньпл коэффициентом деления, состоящий из блока управления, делителя частоты и накопительно, го регистра, с информационным входом которого соединен выход для дробной части коэффнцкеита деления блока управления, а выход переполнения накопительного регистра соединен с входом изменения коэффи1щента деления на единицу блока управления, с входами котОг рого соединены входные клеммы отношешга частот импульсных последовательностей, а вы ход для целочисленной части коэффициента делення блока управлеяяя соединен с первьм входом делителя частоты, второй вход кото рого соединен с входнЫ} клеммой первой импульсной последовательности, причем nepBtiift . вход элемента ИЛИ соединен с входной клеммой второй импульсной последовательности, а выход пе{жого триггера соединен с первым входом блока ключей, отличающий - , с я тем, что , с целью уменьшения уровня помех дробности, в него введены последовательно соединенные элемент НЕ, второй триггер, элемент И, третий триггер и второй блок ключей, причем второй вход первого блока ключей соединен с первой вхрдной клеммой отношения частот, а его выход - с первым входом сумматора, второй вход которого соединен с выходом второго блока ключей, первый вход которого соединен с выходом накопительного регистра, тактовый вход которого соединен с входной клеммой второй импульсной последовательности, а второй (Л вход второго блока ключей соединен с входом элемента НЕ и пе{шым входом первого триггера, второй вход которого соединен с входнсж клеммой второй последовательности, выход делителя частоты соедииен со свободным вхо, дом второго триггера, вход первого элемента задержки соединен с входной клеммой первой о последовательностн, а выход - с вторым вхоЭд 4 : дом элемента И, а вход второго элемента эадержкв соединен с выходом элемента ИЛИ, а выход - с тактовым входом запоминающего N0 регистра, второй вход элемента ИЛИ соединен с выходом элемента И, информационный вход, запоминающего регистра соедииен с выходом сумматора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3555446, кл | |||

| Накладной висячий замок | 1922 |

|

SU331A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авюрское свидетельство СССР | |||

| Способ цифрового фазового детектирования импульсных последовательностей на неравных частотах и устройство для его осуществления | 1979 |

|

SU879738A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-12-30—Публикация

1982-01-29—Подача