ЦИФРОВОЙ СОГЛАСОВАННЫЙ ФИЛЬТР

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЕ УСТРОЙСТВО ФОРМИРОВАНИЯ СПЕКТРАЛЬНО-ЭФФЕКТИВНЫХ СИГНАЛОВ | 2012 |

|

RU2498515C1 |

| Демодулятор дискретных сигналов | 1988 |

|

SU1575322A1 |

| УСТРОЙСТВО УСКОРЕННОЙ СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2011 |

|

RU2446560C1 |

| Перестраиваемый демодулятор дискретных сигналов | 1986 |

|

SU1401637A1 |

| Цифровой согласованный фильтр | 1990 |

|

SU1815796A1 |

| Устройство для приема сигналов относительной фазовой телеграфии | 1983 |

|

SU1138954A1 |

| УСТРОЙСТВО ПЕРЕДАЧИ И ПРИЕМА ДЛЯ ШИРОКОПОЛОСНОЙ РАДИОСВЯЗИ | 1980 |

|

SU1840131A1 |

| Способ передачи дискретных сообщений с синхронизируемой системой двойного шифрования и устройство для его осуществления | 2024 |

|

RU2831996C1 |

| ЦИФРОВОЙ ДЕМОДУЛЯТОР ДВОИЧНЫХ СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИЕЙ ВТОРОГО ПОРЯДКА | 2018 |

|

RU2690959C1 |

| Цифровой согласованный фильтр сигналов с дискретной частотной манипуляцией | 1986 |

|

SU1438017A1 |

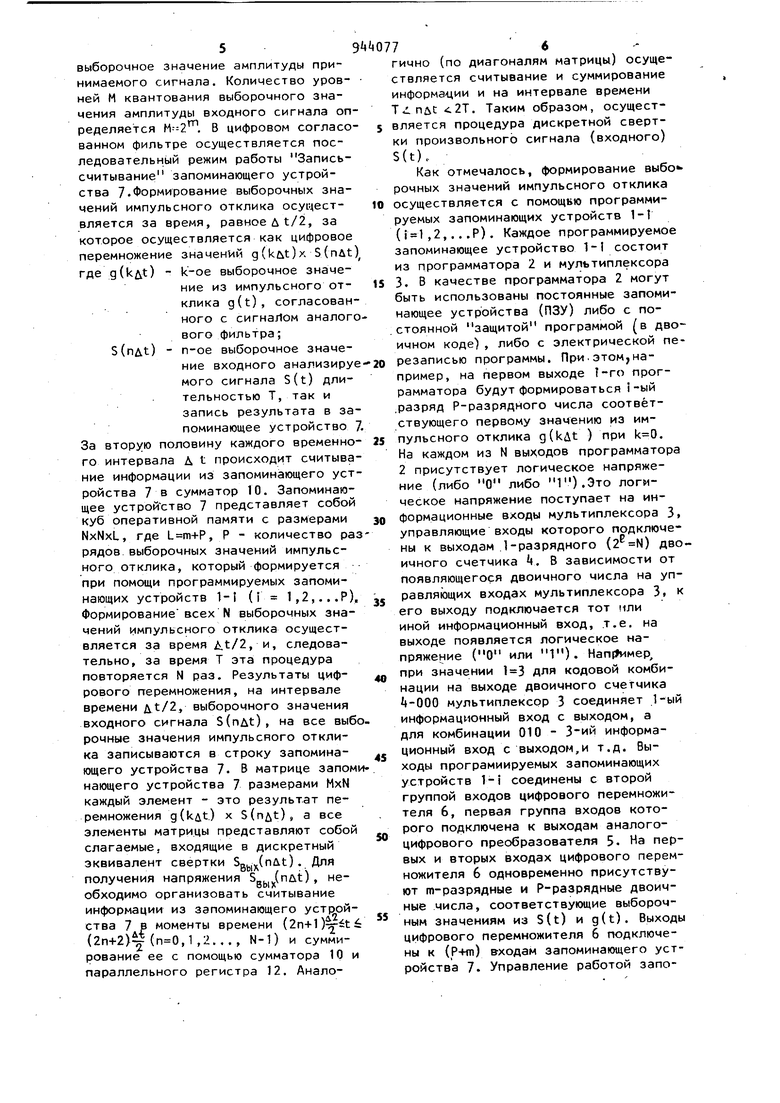

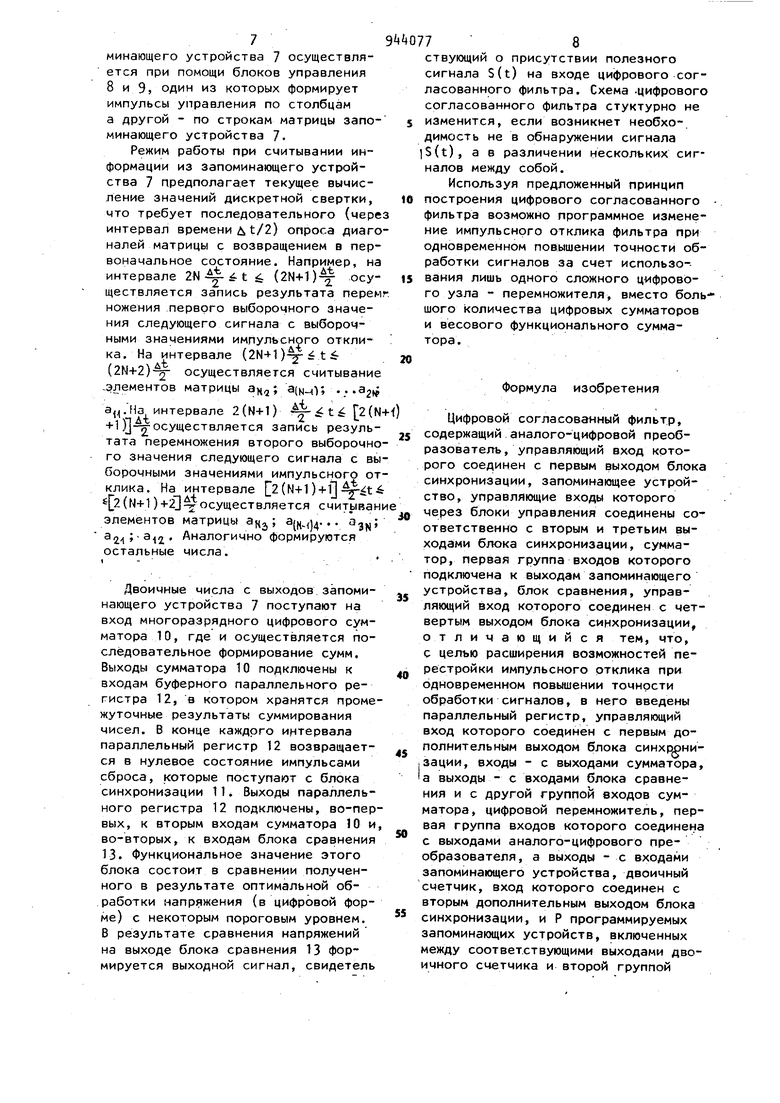

Изобретени.е относится к технике связи и предназначено для когерентной оптимальной обработки дискретны сигналов в системах связи и радиоло кации. Известно устройство оптимальной обработки сложных сигналов, предназ наченное для обработки сигналов с большой базой, в котором входной сигнал поступает на вход многоотводной линии задержки, к отводам которой подключены вертикальные шины взвешивающих устройств, горизонтальн е шины которых подключены к входам суммирующей линии задержки. Импульсный отклик устройства оптицв1П ной обработки сложных сигналов .{дискретного согласованного фильтfpa) формируется при помощи выбора с ответствующих значений коэффициенто передачи взвешивающих устройств lj Недостатком этого устройства является увеличение искажений обрабатываемого сигнала с увеличением ДЛИНЫ многоотводной и суммирующей линий задержки, и как следствие, снижение точности оптимальной обработки сигналов. Известно устройство цифровой обработки сигнала, в котором входное колебание с помощью амплитудно-фазового квантователя (аналого-цифрового преобразователя) преобразуется в совокупность дискретных величин j, характеризующих в виде кода выборочно значение амплитуды и фазы (некогерентный прием) входного колебания. Совокупность дискретных величин, характеризующих в двоичном коде дискретное представление входного колебания, запоминается последовательно во времени в блоках памяти. Выходы элементов памяти, запоминающих код амплитуды, суммируются для каждого эквидистантного уровня фазы, и полученные значения поступают ввесовой сумматор, где производится суммирование и функцио 3 . нальное преобразование совокупности дискретнь1х значений амплитуды и фазы сигнала Г23 . Недостатками этого устройства является наличие большого количества цифровых сумматоров, каждый из которых подключен к ячейке цифровой памяти устройства когерентной фильтрации, что приводит, при большой разрядности выборочных значений импульсного отклика, к существенному усложнению устройства. В то же время при малой разрядности цифровых сумматоров увеличивается погрешность (уменьшается точность} оптимальной когерентной обработки за смет менее точного представления 0 цифровой форме выборочных зна чений импульсного отклика, а также невозможность гибкой перестройки импульсного отклика фильтра, без изменения блок-схемы устройства когерентной фильтрации. Это связано с тем обстоятельством, чт,о любое изменение выборочных значений импульс ного отклика требует исключения (или добавления) как собственно бло ков памяти, так и перестройки или замены цифровых сумматоров и изменения режима работы весового функционального сумматора. Недостатком является также невозможность применения устройства когерентной фильтрации для обработки сигналов в высокоскоростных системах при наличии межсимвольной интерференции. В устройстве каждому образцу принимаемого сигнала должен соответствовать определенный набор цифровых сумматоров .и определенный весовой функциональный сумматор. При большом количестве образцов принимаемого сигнала требуется применение сло ных коммутационных устройств, переключающих выходы блоков памяти к входам различных цифровых сумматоров, что приводит в конечном итоге из-за появляющихся коммутационных помех, к снижению точности оптималь ной когерентной обработки. Цель изобретения - расширение возможностей перестройки импульсног отклика при одновременном повышении точности обработки сигналов. Для этого вцифровой согласованный фильтр, содержащий аналого-цифр вой преобразователь, управляющий вход которого соединен с первым выходом блока синхронизации, запоми 4 нающее устройство, управляющие входы которого через блоки управления соединены соответственно с вторым и третьим выходами блока синхронизации сумматор, первая группа входов которого подключена к выходам запоминающего устройства, блок сравнения, управляющий вход которого соединен с четвертым выходом блока синхронизации, введены параллельный регистр, управляющий вход которого соединен с первым дополнительным выходом блока синхронизации, входы - с выходами сумматора, а выходы - с входами блока сравнения и с другой группой входов сумматора, цифровой перемножитель, первая группа входов которого соединена с выходами аналого-цифрового преобразователя, а выходы - с входами запоминающего устройства, двоичный счетчик, вход которого соединен с вторым дополнительным выходом блока синхронизации, и Р программируемых запоминающих устройств, включенных между соответствующими выходами двоичного счетчика и второй группой входов цифрового перемножителя,, причем каждое программируемое запоминающее устройство состоит из программатора и мультиплексора, информационные входы которого подключены к выходам программатора, а управляющие входы и выход являются соответственно входами и выходом программируемого запоминающего устройства. На чертеже представлена структурная электрическая схема цифрового согласованного фильтра. Устройство содержит Р программируемых запоминающих устройств 1-i1-Р, каждое из которых состоит из программатора 2 и мультиплексора 3, двоичный счетчик k, аналого-цифровой .преобразователь (АЦП) 5. цифровой перемножитель 6, запоминающее устройство 7 блоки управления 8 и 9, сумматор 10, блок синх(эониза1 ии 11, параллельный регистр 12 и блок сравнения 13 Устройство работает следующим образом. Непрерывный сигнал поступает на информационный вход аналого-цифрового преобразователя 5 (АЦП), управляющий вход которого соединен с первым выходом блока синхронизации 11. На m выходах АЦП 5 формируется в виде т-разрядного двоичного числа выборочное значение амплитуды принимаемого сигнала. Количество уровней М квантования выборочного значения амплитуды входного сигнала оп ределяется , В цифровом согласо ванном фильтре осуществляется последовательный режим работы Записьсчитывание запоминающего устройства 7.Формирование выборочных значений импульсного отклика осуществляется за время, равное At/2, за которое осуществляется как цифровое перемножение значен1 й g(kut)x S(nAt где g(kut) - k-oe выборочное значение из импульсного отклика g(t), согласован ного с сигналом аналог вого фильтра; S(nAt) - п-ое выборочное значение входного анализиру мого сигнала S(t) длительностью Т, так и запись результата в за поминающее устройство За вторую половину каждого временно го интервала Д t происходит считыва ние информации из запоминающего уст ройства 7 в сумматор 10. Запоминающее устройство 7 представляет собой куб оперативной памяти с размерами NxNxL, где , Р - количество ра рядов выборочных значений импульсного отклика, который формируется при помощи программируемых запоминающих устройств 1-i (Г 1,2,...Р). Формированиевсех N выборочных значений импульсного отклика осуществляется за время t/2, и, следовательно, за время Т эта процедура повторяется N раз. Результаты цифрового перемножения, на интервале времени At/2, выборочного значения входного сигнала 5(пД1), на все выб рочные значения импульсного отклика записываются в строку запоминающего устройства 7. В матрице запом нающего устройства 7 размерами MxN каждый элемент - это результат перемножения g(kдt.) X S(nut), а все элементы матрицы представляют собой слагаемые, входящие в дискретный эквивалент свертки Sgy(nut). Для получения напряжения 5, (nut) не-выхобходимо организовать считывание информации из запоминающего устройства 7 р моменты времени (2n+1)it (2п+2)(,1,2..., N-1) и суммирование ее с помощью сумматора 10 и параллельного регистра 12. Аналогично (по диагоналям матрицы) осуществляется считывание и суммирование информации и на интервале времени Tinut 2Т. Таким образом, осуществляется процедура дискретной свертки произвольного сигнала (входного) S(t). Как отмечалось, формирование выбо рочных значений импульсного отклика осуществляется с помощью программируемых запоминающих устройств 1(,2,...Р). Каждое программируемое запоминающее устройство 1-1 состоит из программатора 2 и мультиплексора 3. В качестве программатора 2 могут быть использованы постоянные запоминающее устройства (ПЗУ) либо с постоянной защитой программой (в двоичном коде), либо с электрической перезаписью программы. При.этом,например, на первом выходе 1-го программатора будут формироваться i-ый .разряд Р-разрядного числа соответствующего первому значению из импульсного отклика g(kAt ) при . На каждом из N выходов программатора 2 присутствует логическое напряжение (либо О либо 1).Это логическое напряжение поступает на информационные входы мультиплексора 3, управляющие входы которого подключены к выходам 1-разрядного (2 N) двоичного счетчика 4. В зависимости от появляющегося двоичного числа на управляющих входах мультиплексора 3i к его выходу подключается тот или иной информационный вход, т.е. на выходе появляется логическое напряжение (О или 1) . , при значении для кодовой комбинации на выходе двоичного счетчика t-OOO мультиплексор 3 соединяет 1-ый информационный вход с выходом, а для комбинации 010 - 3-ий информационный вход с выходом,и т.д. Выходы програмиируемых запоминающих устройств 1-i соединены с второй группой входов цифрового перемножителя 6, первая группа входов которого подключена к выходам аналогоцифрового преобразователя 5. На первых и вторых входах цифрового перемножителя 6 одновременно присутствуют т-разрядные и Р-разрядные двоичные числа, соответствующие выборочным значениям из S(t) и g(t). Выходы цифрового перемножителя 6 подключены к (Р-нл) входам запоминающего устройства 7. Управление работой запоминающего устройства 7 осуществляется при помощи блоков управления 8 и 9, один из которых формирует импульсы управления по столбцам а другой - по строкам матрицы запоминающего устройства 7. Режим работы при считывании информации из запоминающего устройства 7 предполагает текущее вычисление значений дискретной свертки, что требует последовательного (чере интервал времени д1/2) опроса диаго налей матрицы с возвращением в первоначальное состояние. Например, на интервале 2N- t (2N+1)- ,осуществляется запись результата перем ножения первого выборочного значения следующего сигнала с выборочными значениями импульсного отклика. На интервале ( )- t i(2N+2)- осуществляется считывание элементов матрицы a 3(м,); .. .aj,; а,.На интервале 2(N+1) (N +1 Tj- осуществляется запись результата перемножения второго выборочно го значения следующего сигнала с вы борочными значениями импульсного от клика. На интервале 2(N+1) (N+1 )+23 осуществляется считьтан элементов матрицы ai... а,; Аналогично формируются 21 остальные числа. Двоичные числа с выходов запоминающего устройства 7 поступают на вход многоразрядного цифрового сумматора 10, где и осуществляется последовательное формирование сумм. Выходы сумматора 10 подключены к входам буферного параллельного регистра 12, а котором хранятся промежуточные результаты суммирования чисел. В конце каждого интервала параллельный регистр 12 возвращается в нулевое состояние импульсами сброса, которые поступают с блока синхронизации 11. Выходы параллельного регистра 12 подключены, во-пер вых, к вторым входам сумматора 10 и во-вторых, к входам блока сравнения 13. Функциональное значение этого блока состоит в сравнении полученного в результате оптимальной обработки напряжения (в цифровой форме) с некоторым пороговым уровнем. В результате сравнения напряжений на выходе блока сравнения 13 формируется выходной сигнал, свидетель ствующии о присутствии полезного сигнала S(t) на входе цифрового coi- ласованиого фильтра. Схема .цифрового согласованного фильтра стуктурно не изменится, если возникнет необходимость не в обнаружении сигнала S(t), а в различении нескольких сигналов между собой. Используя предложенный принцип построения цифрового согласованного фильтра возможно программное изменение импульсного отклика фильтра при одновременном повышении точности обработки сигналов за счет использования лишь одного сложного цифрового узла - перемножителя, вместо боль шого количества цифровых сумматоров и весового функционального сумматора. Формула изобретения Цифровой согласованный фильтр, содержащий аналого-цифровой преобразователь , управляющий вход которого соединен с первым выходом блока синхронизации, запоминающее устройство, управляющие входы которого через блоки управления соединены соответственно с вторым и третьим выходами блока синхронизации, сумматор, первая группа входов которого подключена к выходам запоминающего устройства, блок сравнения, управляющий вход которого соединен с четвертым выходом блока синхронизации, отличающийся тем, что, С целью расширения возможностей перестройки импульсного отклика при одновременном повышении точности обработки сигналов, в него введены параллельный регистр, управляющий вход которого соединен с первым дополнительным выходом блока синхр ни3ации, входы - с выходами сумматора, а выходы - с входами блока сравнения и с другой группой входов сумматора, цифровой перемножитель, первая группа входов которого соединена с выходами аналого-цифрового преобразователя, а выходы - с входами запоминающего устройства, двоичный счетчик, вход которого соединен с вторым дополнительным выходом блока синхронизации, и Р программируемых запоминающих устройств, включенных между соответствующими выходами двоичного счетчика и второй группой

входов цифрового перемножителя, причем каждое программируемое запоминающее устройство состоит из прО1- рамматора и мультиплексора, информационные входы которого подключены к выходам программатора, а управляющие входы и выход являются соответственно входами и выходом программируемого запоминающего устройства.

Источники информации, принятые .во внимание при экспертизе

рис. 8.1 (прототип).

Авторы

Даты

1982-07-15—Публикация

1980-11-13—Подача