31577078 4

Изобретение относится к технике кой логике, когда вводятся пороги

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ И УСТРАНЕНИЯ ФАЗОВОЙ НЕОДНОЗНАЧНОСТИ СИГНАЛОВ СИСТЕМ СВЯЗИ С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ | 2010 |

|

RU2444849C2 |

| Многоканальный цифровой коррелятор | 1984 |

|

SU1290352A1 |

| СПОСОБ И СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 2007 |

|

RU2446561C2 |

| СПОСОБ КОРРЕЛЯЦИОННОГО ПРИЁМА СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2002 |

|

RU2237978C2 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 1995 |

|

RU2099893C1 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| Многоканальный цифровой коррелятор | 1983 |

|

SU1211753A1 |

| Коррелятор | 1986 |

|

SU1339584A1 |

| Устройство приема дискретных сигналов с относительно-фазовой модуляцией низкой кратности | 1987 |

|

SU1467786A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ВЗАИМНОЙ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ В РАЗНЕСЕННОЙ РАДИОЛОКАЦИОННОЙ СИСТЕМЕ | 1999 |

|

RU2163383C2 |

Изобретение относится к технике связи и может использоваться в системах обмена дискретной информацией для приема сигналов с фазоразностной модуляцией. Цель изобретения - повышение помехоустойчивости. Устройство содержит блок 1 задержки, фазовые детекторы 2 и 3, фазовращатель 4, блоки 5 и 6 оценки знака, блоки 7 и 8 выделения абсолютной величины, блок 9 сравнения, декодер 10, коррелятор 11 и блок 12 синхронизации. Принимаемый радиосигнал представляет собой смесь помех и полезного сигнала, у которого информация заложена в междискретную фазовую разность. Чтобы устранить влияние фазовой неоднозначности, вносимой блоком 1 задержки, в устройстве детектирования используется декодер 10, функционирующий совместно с коррелятором 11 и блоком 12 синхронизации. Цель достигается путем уменьшения влияния нестабильности блока 1 задержки. Устройство по п.2 ф-лы отличается выполнением декодера 10, дана его ил. 1 з.п. ф-лы, 2 ил.

связи и может использоваться в систе- мах обмена дискретной информацией для приема сигналов с фазоразностной модуляцией (ФРМ).

Цель изобретения - повышение помехоустойчивости путем уменьшения влияния нестабильности блока задержки.

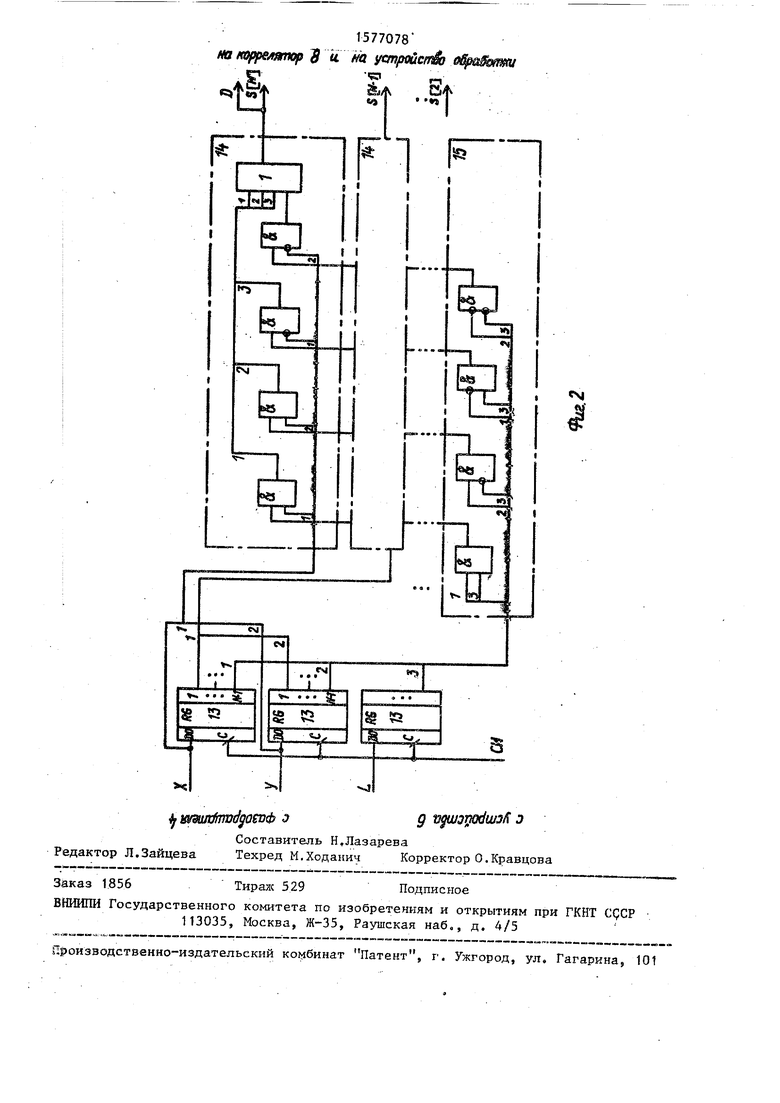

На фиг. 1 изображена структурная электрическая схема предлагаемого устройства; на фиг. 2 - схема декодера.

Устройство содержит блок 1 задержки, первый, второй фазовые детекторы 2 и 3, фазовращатель 4, первый, второй блоки 5 и 6 оценки знака, первый, вто рой блоки 7 и 8 выделения абсолютной величины, блок 9 сравнения, декодер 10, коррелятор 11, блок 12 синхронизации. Декодер 10 состоит из регистров 13 сдвига, коммутаторов 14 и дешифратора 15.

Устройство работает следующим образом.

Пусть принимается радиосигнал, представляющий собой смесь помех и полезного сигнала, у которого информация заложена в междискретную фазовую разность. При этом передаваемый сиг30

С учетом соотношений (2) и (3) по ложение принятого сигнала на фазовой плоскости с точностью до угла 1Г/4 определяется тремя координатами X, Y,L. Но так как во все три координ ты входит неопределенный фазовый на бег (Ое (0, 2,/Г) , определяемый парам ром блока 1, то для однозначного со ответствия между переданной разност фаз и ее оценкой по координатам X, Y,L) такой обработки недостаточно. Чтобы устранить влияние фазовой неод нозначности, вносимой блоком 1, в у ройство детектирования введен декодер 10, функционирующий совместно с коррелятором 11 и блоком 12. С учето того, что в декодере 10 берутся выбо

нал состоит из синхросигнала {S }и не- ки логических символов X,Y,L, алго- посредственно информационной части D . На выходе фазовых детекторов 2 и 3 формируются значения двух проекций видеосигнала на координатные оси X и Y:

X VM-cos();

Y VM-sin(),

где VM - амплитуда сигнала;

УЈ.(/п переданная разность фаз

двух соседних посылок; фазовый сдвиг, вносимый

(1)

40

линией задержки ствие условия.

вследритм его функционирования можно пред ставить в виде

при ,

35 mi при ,

при , (

при ,,,

где Д - текущий номер выборки;

- выходные значения декодера - 1-й бит синхросигнала со значением координат

, , LCD.

Алгоритм (4) оптимально с точки зрения помехоустойчивости и независи мо от начальной фазовой разности d вносимой блоком 1, обеспечивает клас сификацию принимаемого множества зна чений фазовых разностей на два подмножества: подмножество сигналов у которых фазовая разность равна 0; подмножество сигналов фазовой разностью. Это достигается тем, что все принимаемые сигналы, у которых знаки выбранной квадратуры совпадают со знаком принятой большей по абсолютному значению квадратуры 1-го бит синхрослова, образуют подмножество

45

На выходах блоков 5 и 6 формируются логические значения знаков соответствующих проекций, например: 1 при Sign ,

Х

О при Sign /2) 1 при Sign YX),

- YtM

О при Sign

При такой жесткой логике данную операцию можно выполнить на компараторе с нулевым порогом. Возможна и реализация данного устройства по мяг

по обоим знакам.

Логическое значение выходного сигнала блока 9 L определяется неравенством, которое зависит от значений амплитуд квадратур на выходах блоков 7 и 8, например:

(1 при | VMcos(V0)()l О при 1 VH,)sin(+aV0),

(3)

С учетом соотношений (2) и (3) положение принятого сигнала на фазовой плоскости с точностью до угла 1Г/4 определяется тремя координатами X, Y,L. Но так как во все три координаты входит неопределенный фазовый набег (Ое (0, 2,/Г) , определяемый параметром блока 1, то для однозначного соответствия между переданной разностью фаз и ее оценкой по координатам X, Y,L) такой обработки недостаточно. Чтобы устранить влияние фазовой неоднозначности, вносимой блоком 1, в устройство детектирования введен декодер 10, функционирующий совместно с коррелятором 11 и блоком 12. С учетом того, что в декодере 10 берутся выборки логических символов X,Y,L, алго-

ки логических символов X,Y,L, алго-

0

ритм его функционирования можно представить в виде

при ,

5 mi при ,

при , (4)

при ,,,

где Д - текущий номер выборки;

- выходные значения декодера; - 1-й бит синхросигнала со i значением координат

, , LCD.

Алгоритм (4) оптимально с точки зрения помехоустойчивости и независимо от начальной фазовой разности dy, вносимой блоком 1, обеспечивает классификацию принимаемого множества значений фазовых разностей на два подмножества: подмножество сигналов у которых фазовая разность равна 0; подмножество сигналов фазовой разностью. Это достигается тем, что все принимаемые сигналы, у которых знаки выбранной квадратуры совпадают со знаком принятой большей по абсолютному значению квадратуры 1-го бита синхрослова, образуют подмножество

5

0

55

a сигналы, у которых знак квадратуры инверсен знаку принятой большей по абсолютному значению квадратуры 1-го бита синхрослова, образуют подмножество. Рассмотрим подробнее работу декодера 10 по алгоритму (4). Входная информация X,Y,L записывается в соответствующие регистры 13 сдвига, управляемые сдвиговыми импуль сами СИ устройства 12 синхронизации. Глубина записи каждого из регистров равна N-1, где N равно числу бит, образующих передаваемый синхросигнал.

Записанные в регистрах 13 (М-1)-е выборки оценок сигналов поступают на входы дешифратора 15. Значения выходных сигналов декодера 10, снимаемых с выходов коммутаторов 14, определяются из следующих выражений, реализую- щих алгоритм (4) в логике:

...LC1J

.(lJ.

Эти сигналы подаются на вход корре лятора 11, осуществляющего сравнение принятого и продетектированного кода синхросигнала , , .,., с его копией (эталоном). Эта операция может выполняться простой схемой сравнения (совпадения). Выходными сигналами устройства детектирования являются выходные данные с декодера 10, тактовые импульсы (ТИ) выборки и признак начала обработки данных с блока 12.

Формула изобретения

1577078

детектора, первый блок оценки знака, коррелятор, и блок синхронизации, о т- л и чающееся тем, что, с целью повышения помехоустойчивости путем уменьшения влияния нестабильности блока задержки, введены второй блок оценки знака, первый, второй блоки выделения абсолютной величины, блок сравнения и декодер, причем выход первого фазового детектора соединен с входами первого блока определения знака и первого блока выделения абсолютной величины, выход которого соединен с первым входом блока сравнения{- второй вход которого соединен с вьгхс- дом второго блока выделения абсолютной величины, вход которого и вход второго блока определения знака соединены с выходом второго фазового детектора, выходы первого и второго басков определения знака и выход блока сравнения соединены соответственно с первым, вторым, третьим входами ДР- кодера, выход которого является первым выходом устройства и через коррелятор соединен с входами блока синхронизации, первый выход которого соединен с входом синхронизации декодера, а второй и третий соответственно вторым ходаьш устройства.

выходы являются I третьим вы

1, о т л и - что декодер сос2. Устройство по п чающееся тем, тоит из трех регистров сдвига, N-1 коммутаторов, управляемых дешифратором (N количество бит) в синхросигнале, дешифратора, причем первые входы регистров сдвига являются соответственно первым, вторым, третьим входами декодера, вторые входы регистров сдвига являются входом синхронизации, входами дешифратора являются (N-l)-e разряды регистров сдвига, входами первого коммутатора являются входы первого и второго регистров сдвига, входами (N-1)-ro коммутатора являются (N-2)-e выходы первого и второго регистров сдвига, а выходами декодера являются выходы (N-1) коммутаторов, выходы дешифратора соединены с соответствующими входами коммутаторов.

I

ни

&

со

I/

В

t

П--А.™ .. ,п гп

В

t

N

| Оптоэлектронное устройство вычитания десятичных чисел | 1987 |

|

SU1539754A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-07-07—Публикация

1988-02-15—Подача