Изобретение относится к вычислительной технике, предназначено для оперативного определения корреляционных функций случайных процессов в реальном времени и может быть использовано в автоматике, биологии, медицине идругих областях науки и техники.

Целью изобретения является расширение частотного диапазона коррелятора.

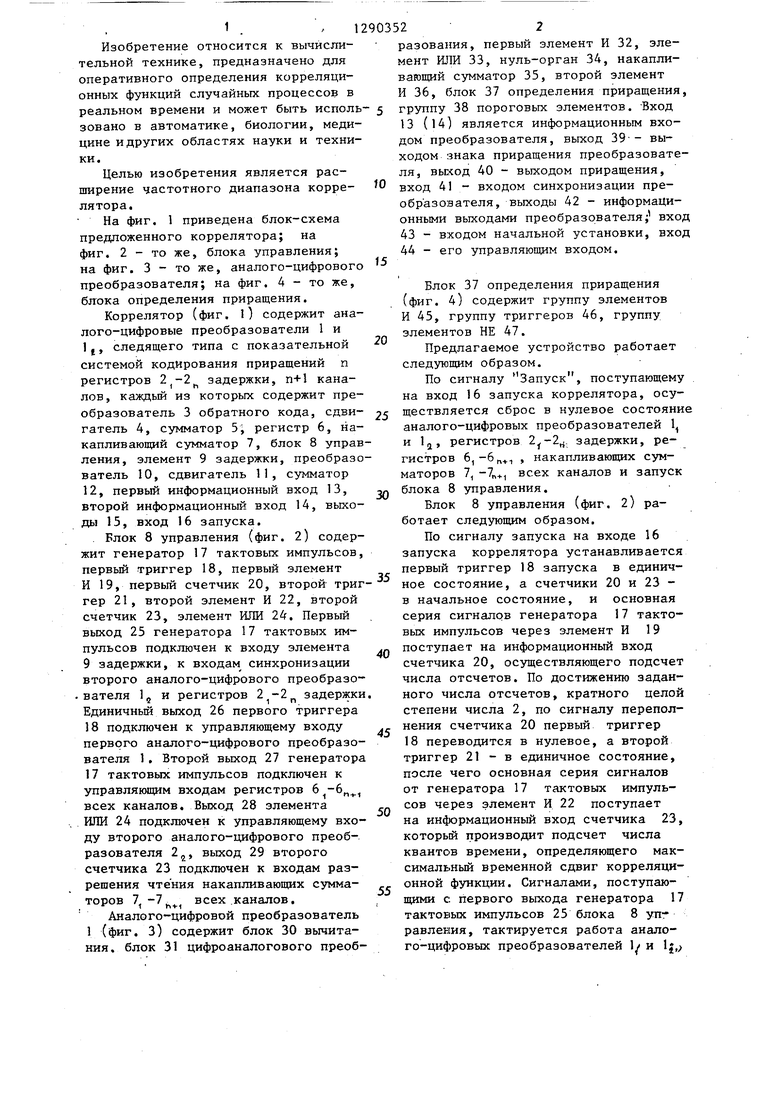

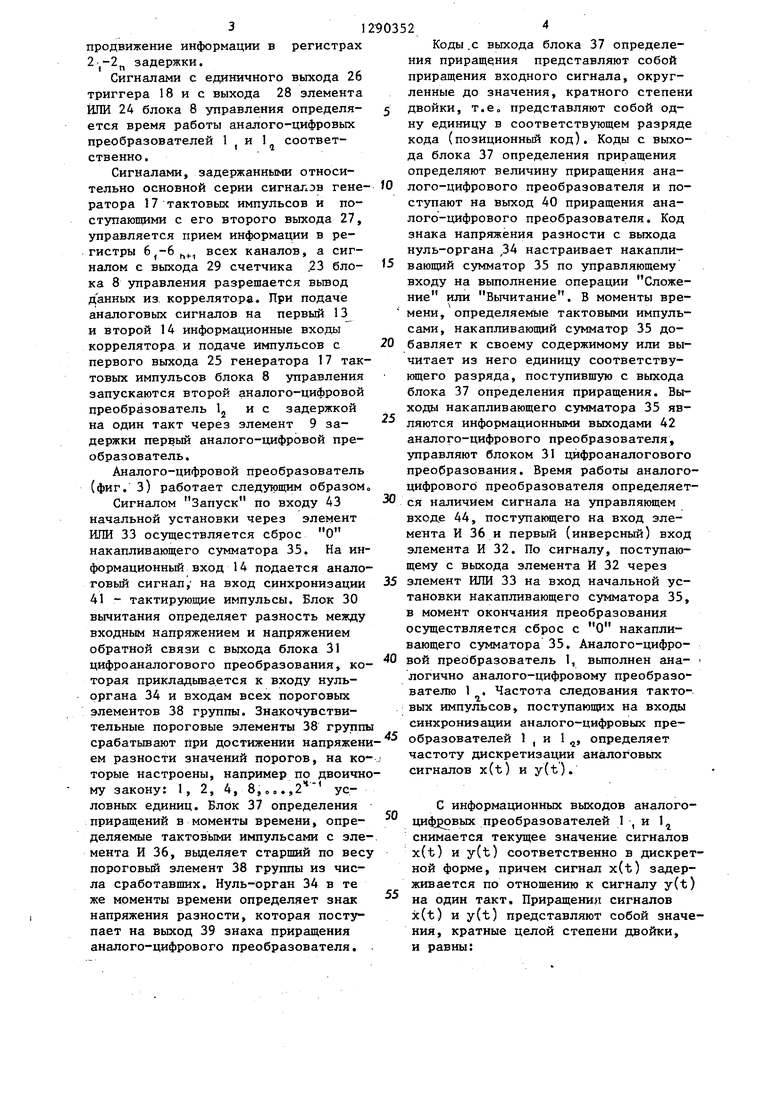

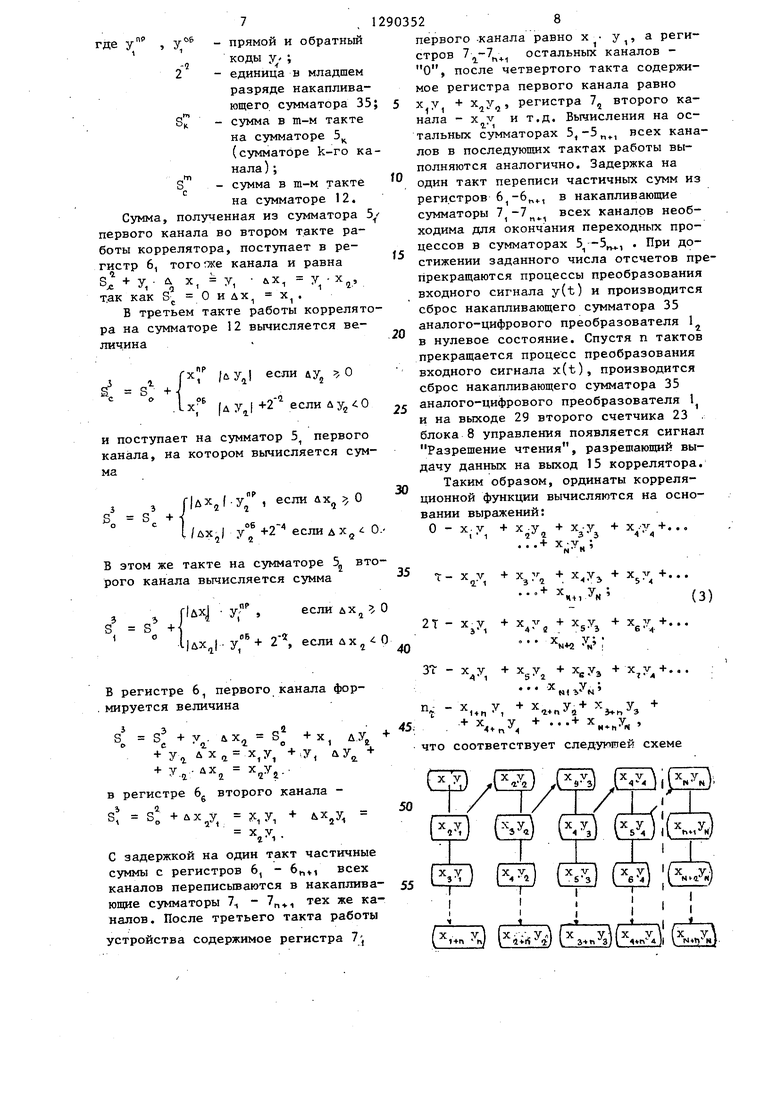

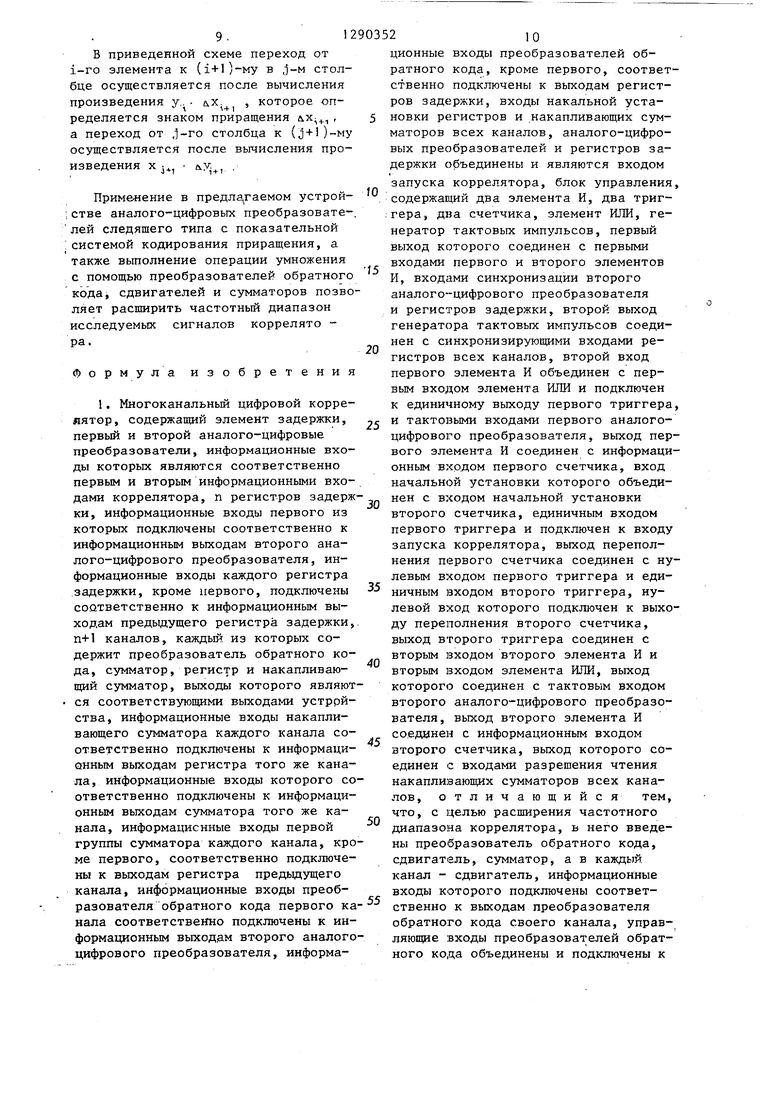

На фиг. 1 приведена блок-схема предложенного коррелятора; на фиг. 2 - то же, блока управления; на фиг. 3 - то же, аналого-цифрового преобразователя; на фиг. 4 - то же, блока определения приращения.

Коррелятор (фиг. 1) содержит аналого-цифровые преобразователи 1 и 1, следящего типа с показательной системой кодирования приращений п регистров задержки, п+1 каналов, каждый из которых содержит преобразователь 3 обратного кода, сдви- гатель 4, сумматор 5; регистр 6, накапливающий сумматор 7, блок 8 управления, элемент 9 задержки, преобразователь 10, сдвигатель 11, сумматор 12, первый информационный вход 13, второй информационный вход 14, выходы 15, вход 16 запуска.

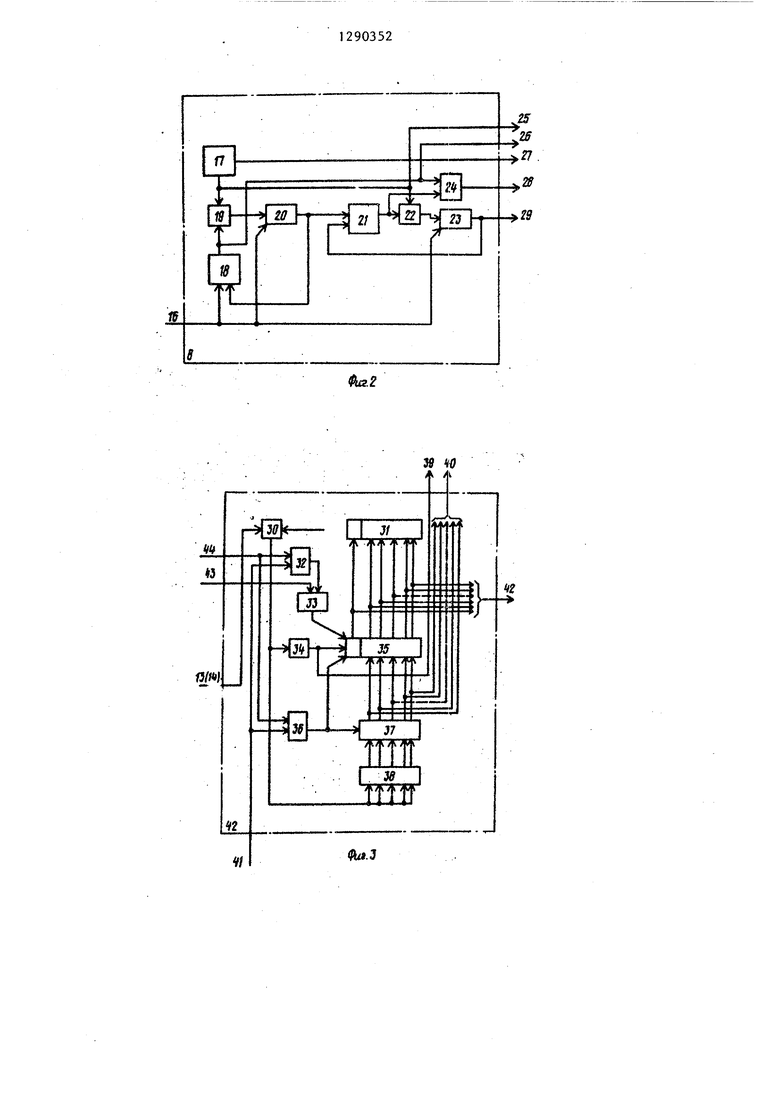

. Блок 8 управления (фиг. 2) содержит генератор 17 тактовых импульсов, первый триггер 18, первый элемент И 19, первый счетчик 20, второй триггер 21, второй элемент И 22, второй счетчик 23, элемент ИЛИ 24. Первый выход 25 генератора 17 тактовых импульсов подключен к входу элемента 9 задержки, к входам синхронизации второго аналого-цифрового преобразователя 1, и регистров задержки Единичный выход 26 первого триггера 18 подключен к управляющему входу первого аналого-цифрового преобразователя 1. Второй выход 27 генератора 17 тактовых импульсов подключен к управляющим входам регистров 6 -6„, всех каналов. Вькод 28 элемента ИЛИ 24 подключен к управляющему входу второго аналого-цифрового преобразователя 2, выход 29 второго счетчика 23 подключен к входам разрешения чтения накапливающих сумматоров 7, 7 всех .каналов.

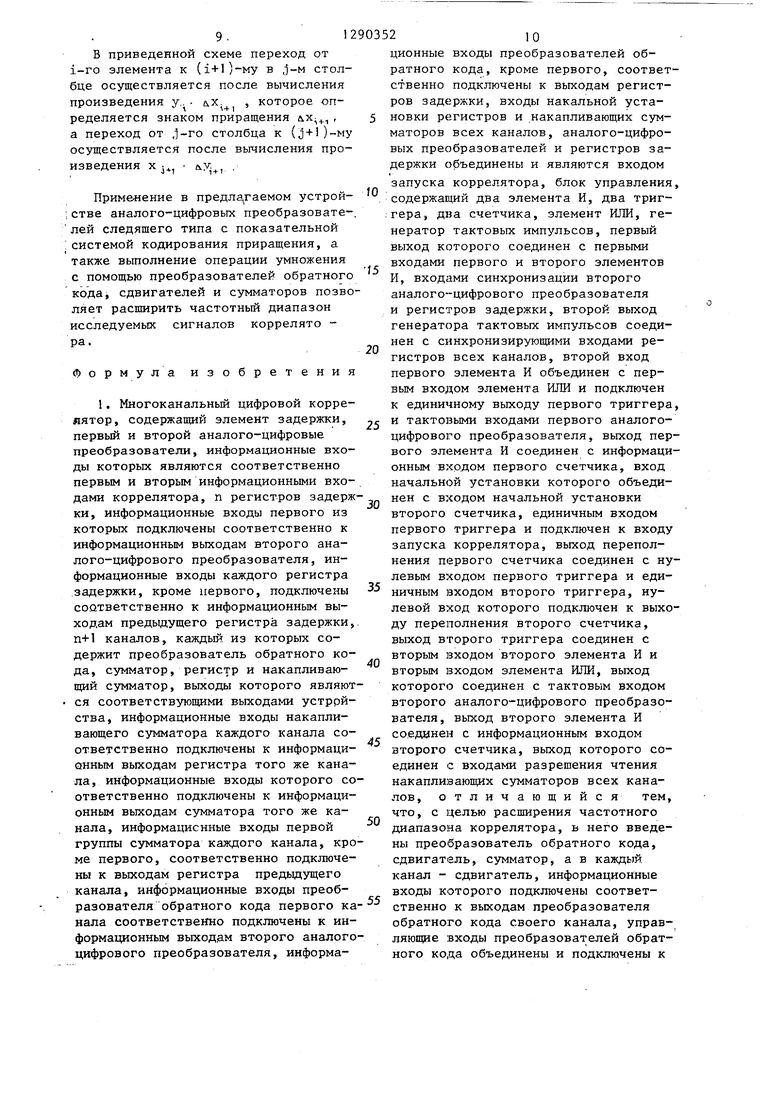

Аналого-цифровой преобразователь 1 (фиг. 3) содержит блок 30 вычитания, блок 31 цифроаналогового преобO

5

0

5

0

5

0

5

0

5

разования, первый элемент И 32, элемент ИЛИ 33, нуль-орган 34, накапливающий сумматор 35, второй элемент И 36, блок 37 определения приращения, группу 38 пороговых элементов. Вход 13 (14) является информационным входом преобразователя, выход 39-- выходом знака приращения преобразователя, выход 40 - выходом приращения, вход 41 - входом синхронизации преобразователя, выходы 42 - информационными выходами преобразователя; вход

43- входом начальной установки, вход

44- его управляющим входом.

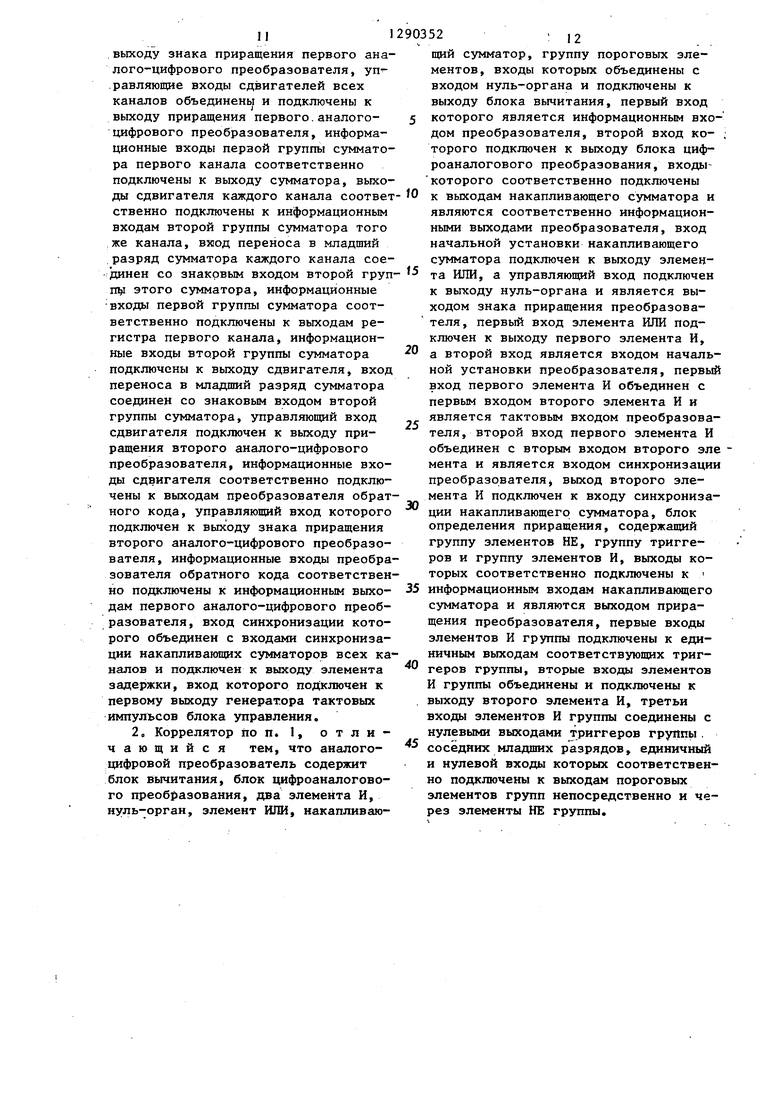

Блок 37 определения приращения (фиг. 4) содержит группу элементов И 45, группу триггеров 46, группу элементов НЕ 47.

Предлагаемое устройство работает следующим образом.

По сигналу Запуск, поступающему на вход 16 запуска коррелятора, осуществляется сброс в нулевое состояние аналого-цифровых преобразователей 1 и 1 j, регистров . задержки, регистров 6,-бп. , накапливающих сумматоров 7, -7„+, всех каналов и запуск блока 8 управления.

Блок 8 управления (фиг. 2) работает следующим образом.

По сигналу запуска на входе 16 запуска коррелятора устанавливается первый триггер 18 запуска в единичное состояние, а счетчики 20 и 23 - в начальное состояние, и основная серия сигналов генератора 17 тактовых импульсов через элемент И 19 поступает на информационный вход счетчика 20, осуществляющего подсчет числа отсчетов. По достижению заданного числа отсчетов, кратного целой степени числа 2, по сигналу переполнения счетчика 20 первый триггер 18 переводится в нулевое, а второй триггер 21 - в единичное состояние, после чего основная серия сигналов от генератора 17 тактовых импульсов через элемент И 22 поступает на ин4юрмационный вход счетчика 23, который производит подсчет числа квантов времени, определякицего мак- сималЕ.ный временной сдвиг корреляционной функции. Сигналами, поступающими с. первого выхода генератора 17 тактовых импульсов 25 блока 8 уп- равлек1ия, тактируется работа аналого-цифровых преобразователей Ь и 1{,

продвижение информации в регистрах

задержки.

Сигналами с единичного выхода

26

триггера 18 и с выхода 28 элемента ИЛИ 24 блока 8 управления определяется время работы аналого-цифровых преобразователей 1 и 1 соответственно .

Сигналами, задержанными относительно основной серии сигналов генератора 17 тактовых импульсов и поступающими с его второго выхода 27, управляется прием информации в регистры всех каналов, а сигналом с выхода 29 счетчика ,23 блока 8 управления разрешается вьгоод данных из. коррелятора. При подаче аналоговых сигналов на первый 13 и второй 14 информационные входы коррелятора и подаче импульсов с первого выхода 25 генератора 17 тактовых импульсов блока 8 управления запускаются второй аналого-цифровой преобразователь 1 и с задержкой на один такт через элемент 9 задержки первый аналого-цифровой преобразователь.

Аналого-цифровой преобразователь (фиг. 3) работает следующим образом

Сигналом Запуск по входу 43 начальной установки через элемент ИЛИ 33 осуществляется сброс О накапливающего сумматора 35. На информационный вход 1 4 подается аналоговый сигнал,- на вход синхронизации 41 - тактирующие импульсы. Блок 30 вычитания определяет разность между входным напряжением и напряжением обратной связи с выхода блока 31 цифроаналогового преобразования, которая прикладьша.ется к входу нуль- органа 34 и входам всех пороговых элементов 38 группы. Знакочувстви- тельные пороговые элементы 38 группы срабатывают при достижении напряжением разности значений порогов, на ко- торые настроены, например по двоичному закону: 1, 2, 4, 8,00., условных единиц. Блок 37 определения приращений в моменты времени, определяемые тактовыми импульсами с элемента И 36, вьщеляет старший по весу пороговый элемент 38 группы из числа сработавших. Нуль-орган 34 в те же моменты времени определяет знак напряжения разности, которая поступает на выход 39 знака приращения аналого-цифрового преобразователя.

5

0

5

0

0

Коды .с выхода блока 37 определения приращения представляют собой приращения входного сигнала, округленные до значения, кратного степени двойки, т.е„ представляют собой одну единицу в соответствующем разряде кода (позиционный код). Коды с выхода блока 37 определения приращения определяют величину приращения аналого-цифрового преобразователя и поступают на выход 40 приращения аналого-цифрового преобразователя. Код знака напряжения разности с выхода нуль-органа ,34 настраивает накапливающий сумматор 35 по управляющему входу на выполнение операции Сложение или Вычитание. В моменты времени, определяемые тактовыми импульсами, накапливающий сумматор 35 добавляет к своему содержимому или вычитает из него единицу соответству- кщего разряда, поступившую с выхода блока 37 определения приращения. В(л- ходы накапливающего сумматора 35 являются информационными выходами 42 аналого-цифрового преобразователя, управляют блоком 31 цифроаналогового преобразования. Время работы аналого- цифрового преобразователя определяется наличием сигнала на управляющем вход,е 44, поступающего на вход элемента И 36 и первый (инверсный) вход элемента И 32. По сигналу, поступающему с выхода элемента И 32 через

5 элемент ИЛИ 33 на вход начальной установки накапливающего сумматора 35, в момент окончания преобразования осуществляется сброс с О накапливающего сумматора 35. Аналого-цифровой преобразователь 1, выполнен ана- логично аналого-цифровому преобразователю 1 . Частота следования тактовых импульсов, поступающих на входы синхронизации аналого-цифровых пре-

5 образователей 1 . и 1 ., определяет

частоту дискретизации аналоговых сигналов x(t) и y(t ).

С информационных выходов аналого- цифровых преобразователей 1 , и 1 снимается текущее значение сигналов x(t) и y(t) соответственно в дискретной форме, причем сигнал x(t) задерживается по отношению к сигналу y(t) на один такт. Приращения сигналов x(t) и y(t) представляют собой значения, кратные целой степени двойки, и равны:

5.

л X )

(sign (sign дУ| )

- 2

--Р

.-р

(1)

где р 1,2,..., г - целая степень

двойки; г - разрядность аналого-цифровых

преобразователей.

Здесь sign лхj или sign ду; формируется на выходе знака приращения, а 2 - на выходе приращения аналого-цифровых преобразователей 1. Произведение лХ; (или ду ) на у. (или Xj ) равно

(sign АХ..) 2 (sign у, )(у, ) (sign ДХ.) 2 . у.

ь

или

то

ДУ.

знак произведения дх:

У;

,равен знаку у. или х-,

или

(sign ду-) 2 (sign x,)j(x,-) (sign ду,- )- 2 Xi .

Знак произведений дх. у. и лу - х равный (sign дх- ) @ (sign у. ) и (sign ду. ) © (sign X. ), определяется преобразователями обратного кода 3-3 и 10 следующи образвм.

Если знак приращения дХ| или ду. положительный (что соответствуе О на выходе знака приращения аналого-цифровых преобразователей 1 и

так как

(sign дх. )®(sign у. )0©(sign у- ) sign у. и

(sign ду. )@(sign x,(sign х- ) sign Х-,

ДУ

Если же знак приращения дх,- или отрицательный (что соответствует

лого -цифровых преобразователей 1, и

1). или

то знак произведения лУ; х равен знаку, ложному у. или X ., так как

.-у. . противопоГ на выходе знака прирашения ана- 45 первом такте содержимое накаплиёающи : сумматоров 35 первого 1 и второго 1 2 аналого-цифровых преобразователей изменяется на О и соответственно. Во втором также со- i

50 держимое накапливающих сумматоров 35 -аналого-цифровых преобразователей 1 и Ц изменяется надх,- и ду- соответственно. На преобразователе 3. об- обратного кода, сдвигателе 4, и сум55 маторе 5, первого канала осуществля(sign ДХ; )@(sign у) l@(sign у )

sign у,

и

(sign ду. )@(sign Xj)l®(sign х ) sign X...

В этом случае лараллельный код с информационных выходов аналого-цифро- 90ГО преобразователя или регистра задержки необходимо инвертировать. Это

1 ется операция

-у.

1 г

So Sc 1

об

I &XJ, если дх, , О,,-1

I Д.Х I +2 , если д

1290352

х

,

JO

15

,, м

ет

20

преобразование выполняется по значениям сигналов с выходов знака приращений аналого-цифровых преобразователей.

р Операции умножения 2 у; или

2 X ,. в предлагаемом .устройстве заменены операциями сдвига на р разрядов в сторону младших разрядов. Операция сдвига выполняется на сдвигате- лях 4 - Д :, , 1 1. С выходов сдвига- телей 4 4 результаты произведений (2) поступают на сумматоры ,, всех каналов, с выхода сдвигателя 11 произведение х , - ду поступает на сумматор 12.

Формирование произведений (2) и корреляционной фракции на примере первого канала.

Код сигнала y(t) в дискретной форме с информационных выходов.второго аналого-цифрового преобразователя 1 поступает в регистр 21 задержки и преобразователь 3, обратного кода, который определяет знак произведения приращения ьх сигнала x(t) и кода текущего значения сигнала y(t) и передает код произведения sign лх-,-у. в сдвигатель 4, в прямом коде, если знак произведения плюс, или в обратном коде, если знак произведения минус. Код сигнала x(t) в дискретной форме с информационных выходов первого аналого-цифрового преобразо- . ватёля 1 в зависимости от знака при35 ращения сигнала лу- и знака кода текущего значения аналогового сигнала x(t) поступает на сдвигатель И через преобразователь 50 обратного кода в обратном коде, если произведение

у.. sign д у. величина отрицательная, и в прямом коде, если это произведение величина положительная.

25

30

е 5, первого канала осуществля1операция

-у.

г

Sc 1

об

I &XJ, если дх, , О,,-1

I Д.Х I +2 , если д

где у

ПР

у° - прямой и обратный

коды уL - единица в младшем разряде накапливающего сумматора 35; S7 - сумма в т-м такте на сумматоре 5 (сумматоре k-ro канала ); S - сумма в т-м такте

на сумматоре 12.

Сумма, полученная из сумматора 5 первого канала во втором такте работы коррелятора, поступает в ре- того 1же канала и равна

гистр 6, sNy...

°с

-х: -у,- т.ак как

X,

лх, у

7.

О и дх 1 в третьем такте работы коррелято- 12 вычисляется вера на сумматоре личина

I

/йУ,1 если йУ, х О

.,-1

( если U УЗ-с О 25

и поступает на сумматор 5 первого канала, на котором вычисляется сумма

В этом же такте на сумматоре 5 рого канала вычисляется

rluxj

,П(

|лх.

2-5

если дх,

если дх ,j О

В регистре 6, первого канала формируется величина

5;

5

-

to

f5

20

25

30

первого -канала равно х у , а регистров 7, остальных каналов - О, после четвертого такта содержимое регистра первого канала равно X У + регистра 7 второго канала - X у и т.д. Вычисления на остальных сумматорах 5,-5„, всех каналов в последующих тактах работы выполняются аналогично. Задержка на один такт переписи частичных сумм из регистров 6,-6„, в накапливающие сумматоры всех каналов необходима для окончания переходных процессов в сумматорах , . При достижении заданного числа отсчетов пре- прекращаются процессы преобразования входного сигнала y(t) и производится сброс накапливающего сумматора 35 аналого-цифрового преобразователя 1 в нулевое состояние. Спустя п тактов прекращается процесс преобразования входного сигнала x(t), производится сброс накапливающего сумматора 35 аналого-цифрового преобразователя 1 и на выходе 29 второго счетчика 23 . блока 8 управления появляется сигнал Разрешение чтения, разрешающий выдачу данных на выход 15 коррелятора. Таким образом, ординаты корреляционной функции вычисляются на основании выражений: О вто35

«ч.

0

2Т X у

J 1

4

у,.:

X, у 6 4

+ ..

X у

А 1

.

ХеУэ «.гУы

,+..

п - 5.

X, У -г + п 1

+ Х У п л

Х.пУа- + .. .+

X

3

X V гч

ЧТО соответствует следующей схеме

С задержкой на один такт частичные суммы с регистров 6, - 6, всех каналов переписьшаются в накапливающие сумматоры 7 7, тех же каналов. После третьего такта работы

устройства содержимое регистра 7,

50

ё) sM

55

l 3E±3SS

В приведенной схеме переход от i-ro элемента к (1+)-му в ,J-M столбце осуществляется после вычисления произведения у,. й.х. , которое определяется знаком приращения лх. , а переход от ,1-го столбца к (j + l)-My осуществляется после вычисления произведения X

J-4

й-У..

Применение в предла;Гаемом устрой- ;стве аналого-цифровых преобразовате-. лей следящего типа с показательной системой кодирования приращения, а также выполнение операции умножения с помощью преобразователей обратного кода, сдвигателей и сумматоров позволяет расщирить частотный диапазон исследуемых сигналов коррелято - ра.

Форму л а изобретения

1. Многоканальный цифровой коррелятор, содержащий элемент задержки, первый и второй аналого-цифровые преобразователи, информационные входы которых являются соответственно первым и вторым информационными вхо-. дами коррелятора, п регистров задержки, информационные входы первого из которьпс подключены соответственно к информационным выходам второго аналого-цифрового преобразователя, информационные входы каждого регистра задержки, кроме первого, подключены соответственно к информационным выходам предыдущего регистра задержки,. n-1-l каналов, каждый из которых содержит преобразователь обратного кода, сумматор, регистр и накапливающий сумматор, выходы которого являются соответствуюпщми выходами устройства, информационные входы накапливающего сумматора каждого канала соответственно подключены к информационным выходам регистра того же канала, информационные входы которого соответственно подключены к информационным выходам сумматора того же канала, информационные входы первой группы сумматора каждого канала, кроме первого, соответственно подключены к выходам регистра предьщущего канала, информационные входы преобW

15

20

25

30

35

40

45

50

ционные входы преобразователей об ратного кода, кроме первого, соот ственно подключены к выходам реги ров задержки, входы накальной уст новки регистров и .накапливающих су маторов всех каналов, аналого-цифр вых преобразователей и регистров держки объединены и являются вход запуска коррелятора, блок управле содержащий два элемента И, два тр :гера, два счетчика, элемент ИЛИ, нератор тактовых импульсов, первы выход которого соединен с первыми входами первого и второго элемент И, входами синхронизации второго аналого-цифрового преобразователя и регистров задержки, второй выход генератора тактовых импульсов соед нен с синхронизирующими входами р гистров всех каналов, второй вход первого элемента И объединен с пе вым входом элемента ИЛИ и подключе к единичному выходу первого тригг и тактовыми входами первого анало цифрового преобразователя, вьпсод вого элемента И соединен с информ онным входом первого счетчика, вх начальной установки которого объед нен с входом начальной установки второго счетчика, единичным входом первого триггера и подключен к вх запуска коррелятора, выход перепол нения первого счетчика соединен с левым входом первого триггера и ед ничным входом второго триггера, н левой вход которого подключен к вы ду переполнения второго счетчика, выход второго триггера соединен с вторым входом второго элемента И и вторым входом элемента ИЛИ, выход которого соединен с тактовым вход второго аналого-цифрового преобра вателя, выход второго элемента И соединен с информационным входом второго счетчика, выход которого единен с входами разрещения чтения накапливающих сумматоров всех кан лов, отличающийся т что, с целью расширения частотног диапазона коррелятора, в него введ ны преобразователь обратного кода сдвигатель, сумматор, а в каждый канал - сдвигатель, информационны входы которого подключены соответразователя обратного кода первого ка-- ственно к выходам преобразователя

нала соответственно подключены к информационным выходдм второго аналого- цифрового преобразователя, информа

5

0

5

0

5

0

5

0

ционные входы преобразователей обратного кода, кроме первого, соответственно подключены к выходам регистров задержки, входы накальной установки регистров и .накапливающих сумматоров всех каналов, аналого-цифровых преобразователей и регистров задержки объединены и являются входом запуска коррелятора, блок управления, содержащий два элемента И, два триг- :гера, два счетчика, элемент ИЛИ, генератор тактовых импульсов, первый выход которого соединен с первыми входами первого и второго элементов И, входами синхронизации второго аналого-цифрового преобразователя и регистров задержки, второй выход генератора тактовых импульсов соединен с синхронизирующими входами регистров всех каналов, второй вход первого элемента И объединен с первым входом элемента ИЛИ и подключен к единичному выходу первого триггера, и тактовыми входами первого аналого- цифрового преобразователя, вьпсод первого элемента И соединен с информационным входом первого счетчика, вход начальной установки которого объединен с входом начальной установки второго счетчика, единичным входом первого триггера и подключен к входу запуска коррелятора, выход переполнения первого счетчика соединен с нулевым входом первого триггера и единичным входом второго триггера, нулевой вход которого подключен к выходу переполнения второго счетчика, выход второго триггера соединен с вторым входом второго элемента И и вторым входом элемента ИЛИ, выход которого соединен с тактовым входом второго аналого-цифрового преобразователя, выход второго элемента И соединен с информационным входом второго счетчика, выход которого соединен с входами разрещения чтения накапливающих сумматоров всех каналов, отличающийся тем, что, с целью расширения частотного диапазона коррелятора, в него введены преобразователь обратного кода, сдвигатель, сумматор, а в каждый канал - сдвигатель, информационные входы которого подключены соответобратного кода своего канала, управляющие входы преобразователей обратного кода объединены и подключены к

ч

выходу знака приращения первого аналого-цифрового преобразователя, равляющие входы сдвигателей всех каналов объединены и подключены к выходу приращения первого.аналого- цифрового преобразователя, информационные входы первой группы сумматора первого канала соответственно подключены к выходу сумматора, выходы сдвигателя каждого канала соответ ственно подключены к информационным входам второй группы сумматора того же канала, вкод переноса в младший разряд сумматора каждого канала соединен со знаковым входом второй груп TOf. этого сумматора, информационные входы первой группы сумматора соответственно подключены к выходам регистра первого канала, информационные входы второй группы сумматора подключены к выходу сдвигателя, вход переноса в младший разряд сумматора соединен со знаковым входом второй группы сумматора, управляющий вход сдвигателя подключен к выходу приращения второго аналого-цифрового преобразователя, информационные входы сдвигателя соответственно подключены к выходам преобразователя обратного кода, управляющий вход которого подключен к выходу знака приращения второго аналого-цифрового преобразователя, информационные входы преобра зователя обратного кода соответствен но подключены к информационным выходам первого аналого-цифрового преобразователя, вход синхронизации которого объединен с входами синхронизации накапливающих сумматоров всех каналов и подключен к выходу элемента задержки, вход которого подключен к первому выходу генератора тактовых импульсов блока управления.

2 о Коррелятор по п. 1, отличающийся тем, что аналого- цифровой преобразователь содержит блок вычитания, блок цифроаналогово- го преобразования, два элемента И, нуль-орган, элемент ИЛИ, накапливаю90352: 12

щий сумматор, группу пороговых элементов, входы которых объединены с входом нуль-органа и подключены к выходу блока вычитания, первый вход 5 которого является информационным входом преобразователя, второй вход ко- ; торого подключен к выходу блока циф- роаналогового преобразования, входы- которого соответственно подключены

О к выходам накапливающего сумматора и

являются соответственно информационными выходами преобразователя, вход начальной установки накапливающего сумматора подключен к выходу элемен та ИЛИ, а управляющий вход подключен

к выходу нуль-органа и является выходом знака приращения преобразователя, первый вход элемента ИЛИ подключен к выходу первого элемента И,

0 а второй вход является входом начальной установки преобразователя, первый вход первого элемента И объединен с первым входом второго элемента И и является тактовым входом преобразователя, второй вход первого элемента И объединен с вторым входом второго эле мента и является входом синхронизации преобразователяj выход второго элемента И подключен к входу синхронизации накапливающего сумматора, блок определения приращения, содержащий группу элементов НЕ, группу триггеров и группу элементов И, выходы которых соответственно подключены к

35 информационным входам накапливающего сумматора и являются выходом приращения преобразователя, первые входы элементов И группы подключены к единичным выходам соответствующих триг геров группы, вторые входы элементов И группы объединены и подключены к выходу второго элемента И, третьи входы элементов И группы соединены с нулевыми выходами триггеров группы .

25

30

45

соседних младших разрядов, единичный и нулевой входы которых соответственно подключены к выходам пороговых элементов групп непосредственно и через элементы НЕ группы.

S

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный цифровой коррелятор | 1983 |

|

SU1211753A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1273944A1 |

| Устройство для поворота вектора (его варианты) | 1982 |

|

SU1078431A1 |

| Устройство для регистрации однократных сигналов | 1980 |

|

SU983741A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1290351A1 |

| Многоканальный цифровой коррелятор | 1984 |

|

SU1292006A1 |

| Параболический интерполятор | 1984 |

|

SU1231512A1 |

| Цифровой коррелятор | 1980 |

|

SU894719A1 |

Изобретение относится к вычислительной технике, предназначено для оперативного определения корреляционных функций случайных процессов в реальном времени и может быть использовано в автоматике, биологии, медицине и других областях науки и техники. Целью изобретения является расширение частотного диапазона коррелятора. Коррелятор содержит аналого-цифровые преобразователи 1, Ц следящего типа, с показательной системой кодирования приращений, п регистров задержки , п+1 каналов, каждый КЗ которых содержит преобразователь 3 обратного кода, сдвигате- ли 4 и П, сумматоры 5 и 12, регистр 6, накапливающий сумматор 7, блок 8 управления, элемент 9 задержки, преобразователь 10. Применение в устройстве аналого-цифровых преобразователей следящего типа с показательной системой кодирования приращений, а также выполнение операции умножения с помощью преобразователей обратного кода, сдвигателей и сумматоров поз воляет расширить частотный диапазон исследуемых сигналов коррелятора. 1 з.п. ф-лы, 4. ил. с (О fuf.1

«W

.J

Составитель А, И&анова Редактор М, Келемеш Техред Л. Сердюков а Корректор Г. Решетник

7904/48

Тираж .673 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг.4

| Цифровой коррелятор | 1976 |

|

SU610117A1 |

| Многоканальный цифровой коррелятор | 1983 |

|

SU1211753A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-15—Публикация

1984-01-26—Подача