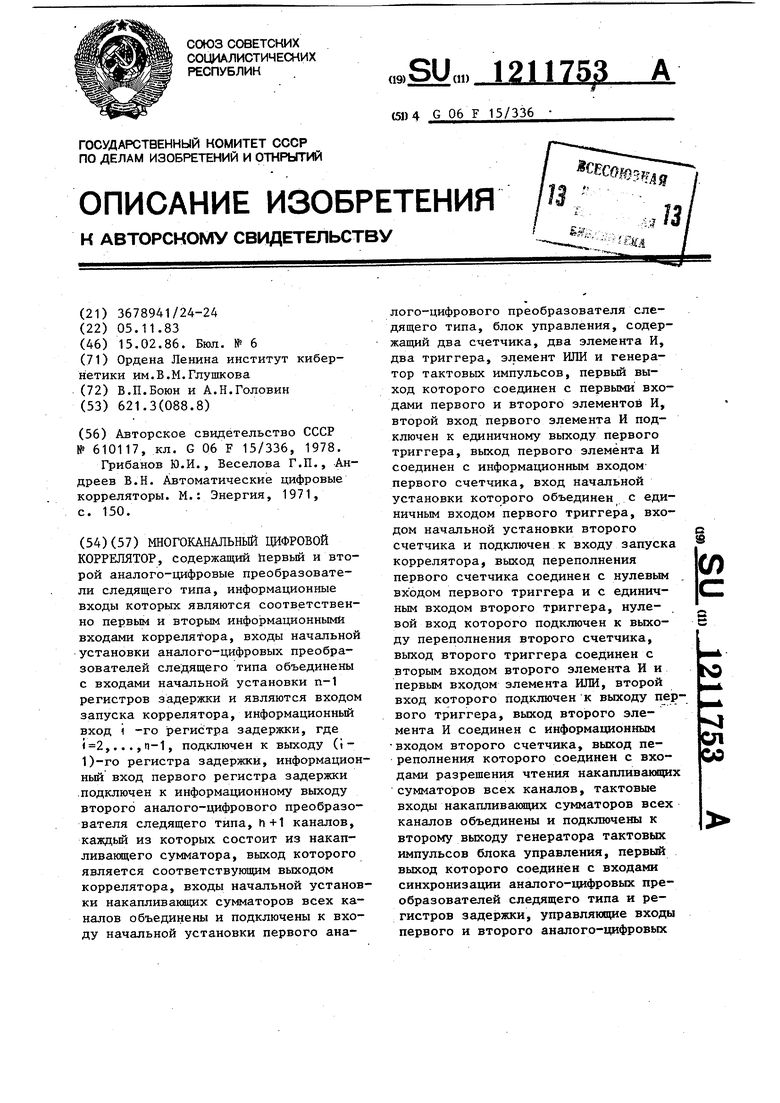

преобразователей следящего типа соответственно подключены к выходу элемента ИЛИ и выходу первого триггера блока управления, отличающийся тем, что, с целью повышения быстродействия коррелятора, введен элемент задержки, а в каждый канал - преобразователь обратного кода, сумматор и регистр, причем вход переноса сумматора первого канала через .элемент задержки подключен к выходу приращения второго аналого- цифрового преобразователя следящего типа, первый информационный вход сумматора каждого канала подключен к выходу преобразователя обратного кода того же канала, второй информа- ционньш вход сумматора i-го канбша, где 2, ... J ц , объединен с информационным входом накапливанядего сумматора (1-1)-го канала и подключен к выходу регистра (i-l)-ro канала, второй вход сумматора первого канала подключен к выходу сумматора второго канала, выход сумматора каждого канала соединен с информационном входом регистра того же канала, входы

Изобретение относится к вычислительной технике, предназначено для оперативноро определения корреляционных функций случайных процессов в реальном времени и может быть исполь зовано в Гидрометеорологии, автоматике, биологии, медицине и других областях науки и техники.

Целью изобретения является повышение быстродействия коррелятора.

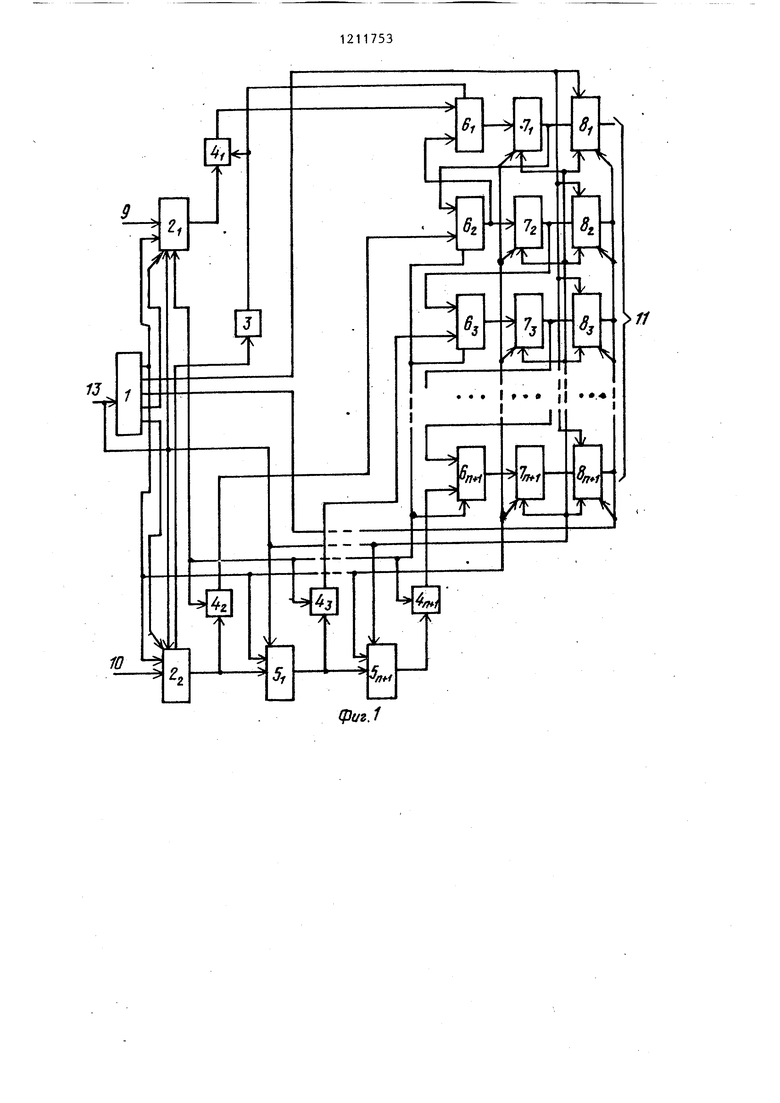

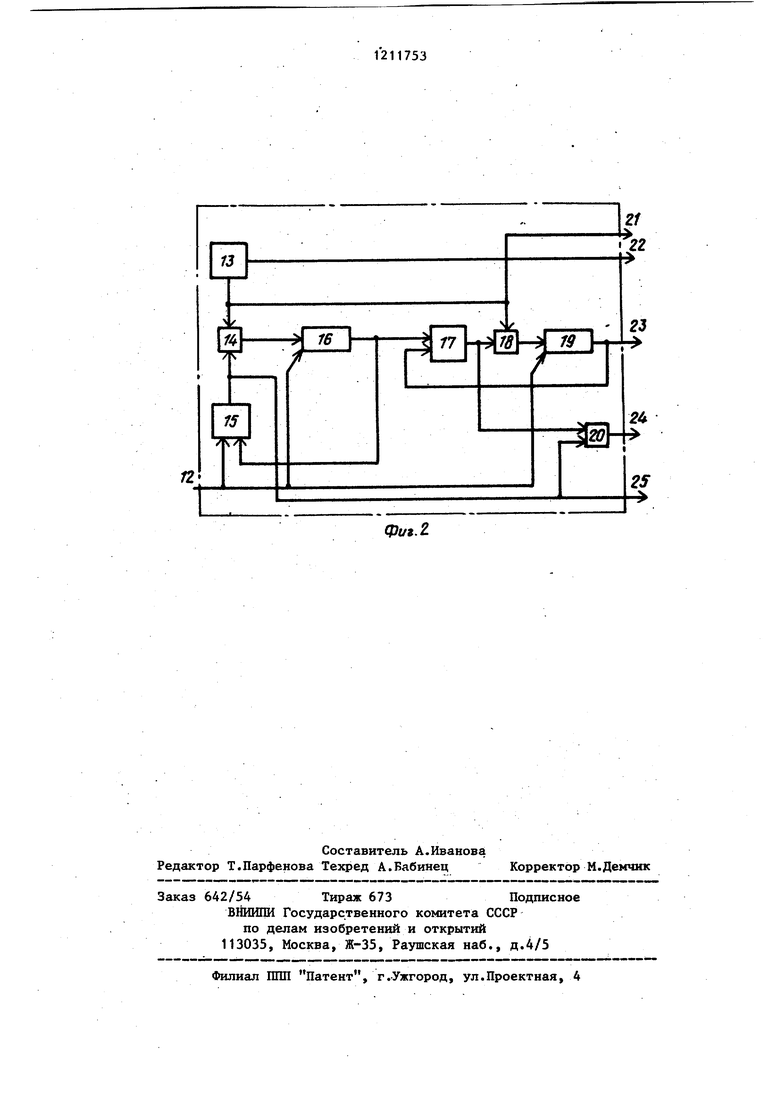

На фиг.1 приведена блок-схема коррелятораJ на фиг.2 - блок-схема блока управления.

Устройство содержит п каналов, блок 1 управления, аналого-цифровые преобразователи 21 и 2 следящеГ-о типа, элемент 3 задержки, (п+1) преобразователей 4,-Anti обратного кода (п-1) регистров 5,-5п-1 задерлоси, (п+1) сумматоров 6, (п+1) ре- гистров ( , (п+1) накапливающих сумматоров 8 -8nti. Причем, каждый i-ьй канал устройства содержит преобразователь 4; обратного кода, сумначальной установки и входы синхронизации регистров всех каналов соответственно объединены и подключены соответственно к входу начальной установки и входу синхронизации второго аналого-цифрового преобразователя следящего типа, информационный вход преобразователя обратного кода первого канала подключен к информационному выходу первого аналого-цифрового пре- о.бразователя следящего типа, а управляющий вход - к выходу элемента за- дерйжи, информационный вход преобразователя обратного кода i -го канала, где i 3, ...,п, подключен к выходу i -го регистра задержки, информационный вход преобразователя обратного кода второго канала подключен к информационному выходу второго аналого-цифрового преобразователя следящего типа, управляющие входы преобразователей обратного кода и входы переноса сумматоров всех каналов, кроме первого, объединены и подключены к выходу приращений первого аналого-цифрового преобразователя следящего типа.

матор 6; регистр Iff и накапливаюврй сумматор 8;. Входы первого и второго аналого-цифровых преобразователей являются соответственно первым 9 и вторым 10 информационными входами коррелятора, выходы накашшвакицих сумматоров В являются соответствующими выходами 11 коррелятора. Вход 12 является входом начальной установки коррелятора.

Блок 1 управления содержит генератор 13 тактовых импульсов, первый элемент И 14, первый триггер 15, первый счетчик 16, второй триггер 17, второй элемент И 18, йторой счетчик 19, элемент ИЛИ 20, причем единичный вход первого триггера является входом 12 начальной установки коррелятора, первьй и второй выходы 21 и 22 генератора 13 тактовых шетульсов соединены соответственно со входг1ми синхронизации аналого-цифровых преобразователей 2 и 2 и тактовыми входами накапливаняцих сумматоров 8 всех

каналов, выход 23 второго счётчика 19 соединен с входами разрешения записи накапливающих сумматоров 8 всех каналов, выход 24 элемента ИЛИ 20 соединен с управляющим входом первого аналого-цифрового преобразователя 2, а выход 25 первого триггера 15 . соединен с управляющим входом второго аналого-цифрового преобразователя 2г.

Устройство работает следующим образом.

Работа устройства начинается с момента поступления сигнала запуска на вход, по которому осуществляется на чальная установка аналого-цифровых преобразователей 2, и 2, регистров „5,-5п, задержки, регистров t накапливающих сумматоров SQ-S и запуск блока 1 управления.

Частота следования тактовых импульсов, поступающих с первого выхода генератора 13 тактовых импульсов блока 1 управления на входы синхронизации аналого-цифровых преобразователей 2, и 22, определяет частоты дискретизации аналоговых сигналов x(t) и y(t), поступающих на первый и второй информационные входы 9 и 10 устройства соответственно.

С информационных выходов аналого- цифровых преобразователей 2 и 22 соответственно снимается текущее значение Х-, у сигналов x(t) и y(t) соответственно в дискретной форме, а с выходов приращений этих же аналого-цифровых преобразователей - приращений сигнала лх; и ду,- соответственно. Причем приращение представлено значащим значением младшего разряда т-разрядного числа. При этом единица соответствует отрицательному приращению сигнала на информационном выходе соответствующего аналого- цифрового преобразователя, а нуль - положительному приращению, поэтому приращения их- и ьу соответственно равны

4x; (signAXj)2 ; 4y; (signAy,- ).

Разрядность сумматоров 6 и регистров 7 составляет 2т разрядов, разрядность регистров 5 задержки и преобразователей 4 обратного кода - m разрядов. В устройстве вычисление корреляционнЬй функции выполняется по алгоритму

R(k),.

где .., +ЛХ| , У;-,- + У ;-к Тогда

1 «

(2)

(k)R,,-;y.K 5,S )(у,--,.,+йУ;-) j- -

+ &Х;у..,.+Х;,,ду.+Ах;лу;. -E

-J 14 1 xj., y..,.+UX;y.. +X;&y- J ,

где k - номер отсчета корреляционной

функции.

Вычисление i-oro произведения jij отсчетов Xj и yj при вычислении.корреляционной функции RCkC) при осуществляется согласно выражению

., У;., +ЛХ;У;., -l-X-Vy- Z.., + ., +Х.уе,(3) ,

причем при реализации этого выражения на двухвходовых сумматорах оно принимает вид

., +4Х-У;., ;

z; z.z .+x;4y;

30 Вычисление вьфажения (3) производится на сумматорах 6J и преобразователях 4J обратного кода (, п+1) следующим образом

35

Vs- Г I t j.,

Гг.Л

li-i если sign

V

«. l - Qb к M

.l4-,-,J 2 если sign i),

a на сумматоре 6, и преобразователе 40 , обратного кода следующим образом

5о-5л

tVi P -ni X; J 2если Sign i 0

1,

где

V -|пр

Ш

прямой код содержимого

50

., регистра 7;., ,

ha -пр f t -io6pi

i-lj )Ui llпрямой И обратный КОДЫ

значения у- на информационном выходе аналого- цифрового преобразователя 2

2

11 г г «поьр

4 1 iJ прямой и обратный коды

значения х на информационном выходе аналого-цифрового преобразователя 2, .

Промежуточные произведения типа

У,Г 2. У,-.,Г 2- и другие получаются путем подачи сигналов с выходов преобразователей 4,-4, обратного кода на m младших разрядов соответствующих информационных сумма

торов 6,-6п41 .

Таким образом на сумматорах 6, и 6j производится суммирование промежуточных произведений и значений произведений отсчетов сигналов x(t) и y(t), полученных в (1-1)-ом такте работы устройства, дающих в сумме значения произведений отсчетов сигна лов x(t) и y(t) в i-oM такте.

Алгоритм рабо ты устройства реализуется следующим образом.

В блок 1 управления по сигналу запуска на входе устанавливаются пер вый триггер 15 в единичное состояние а счетчики 16 и 19 - в начальное состояние, и основная серия сигналов генератора 13 тактовых импульсов через элемент И 14 поступает на информационный вход счетчика 16, осуществляющего подсчет числа отсчетов. По достижению заданного числа отсчетов, кратног целой степени числа 2, по сигналу переполнения счетчика 16 первый триггер 15 переводится в нулевое, а второй триггер 17 - в единичное состояние, после чего основная серия сигналов от генератора 13 тактовых импульсов через элемент И 18 поступает на информационный вход счетчика 19, которьш производит подсчет числи квантов времени, определяющего максимальный временной сдвиг корреляционной функции. Сигналами, поступающими с выхода 21 блока управления 1, тактируется работа аналого-цифровых преобразователей 2 и 22, продвижение информации в регистрах 5 задержки и запись информации в регистры , .

Сигналами, задержанными относительно основной серии сигналов генератора 13 тактовых импульсов и поступающими с выхода 23 блока 1 управления, осуществляется прием информации в накапливающие сумматоры 8,-8„,. Сигналом с выхода 24 блока 1 управления разрешается вьшод данных из устройства, а сигналами с выходов 24 и 25 блока 1 управления разрешается работа аналого-цифрового преобразователей 2 и 2г соответственно .

10

15

20

25

30

35

40

5

0

5

В первом канале устройства осуществляется вычисление отсчетов корреляционной функции при временном сдвиге, равном нулю. Текущее значение х; сигнала x(t) поступает на преобразователь 4, с задержкой, которая определяется временем работы аналого-цифрового преобразователя 2 и длительностью операции суммирования на сумматоре 6.

В первом такте работы устройства текущее значение у с информационного выхода аналого-цифрового преобразователя 22 поступает на вход ре- .гистра задержки 5 и преобразователь 42, а текущее значение х, с информационного выхода аналого-цифрового преобразователя 2, спустя время, определяемое элементом 3 задержки, поступает на вход преобразователя обратного кода 4,.

В зависимости от знака приращения лх, и ьу, сигналов x(t) и y(t) соответственно на первые информационные входы сумматоров 6( и 63 поступают прямью коды X,, Уд и нулевое значение переноса в младший разряд или обратные коды х,, у и единичное значение переноса в младший разряд.

Таким образом, в первом такте работы коррелятора производится вычисление на сумматоре 6г

2,,бу, на сумматоре 6,

,+х,ду, дх,у„+х,йу, ,

где йУ, У, , .

Результаты вычисления соответственно записываются в регистры 7, и 7 . В первом такте содержимое накапливающего сумматора 8, равно х,у,,. а накапливающих сумматоров 8,,-8„4, равно 0.

Во втором такте работы устройства содержимое регистра 5 задержки равно Уд , на информационные входы в преобразователей обратных кодов 4,- 4j поступают коды х-, у, и у соответственно, на второй информационный вход сумматора 6 поступает содержимое регистра , равное х,йу, . Результат суммирования с сумматора 6 поступает на сумматор Ь, и регистр 7. На сумматоре 6( вычисляется сумма ,+х. .

В третьем такте работы устройства содержимое регистра 5 задержки равно

-«- .

у,, преобразователи обрат- .ных кодов 4,-44 поступают коды х,, Vg У, и Уд соответственно.

На сумг аторе 6 вычисляются сумма х У2+Дх, , на сумматоре 6, - сумма х,,, а на сумматоре 6, - сумма Xj,y,+дх,у,Х2У, .

В накапливакяцих сумматорах 8 после вьшолнения третьего такта работы содержимое в суг маторе соответственно равно

8,-x,y,+x,,y,, 82-х.у,+х УЗ, 8,-х,У, , 84-8„,,-0.

При достижении заданного числа отсчетов прекращается процесс преобразования входного сигнала y(t) и производится начальная установка аналого-цифрового преобразователя 2 в

См7

2 У2

зИз

Xityif )

;

т

1 ) ) С Уз )

GiuOQiiZ) С) С5К)

1

1

3 1пУЙ)(j)

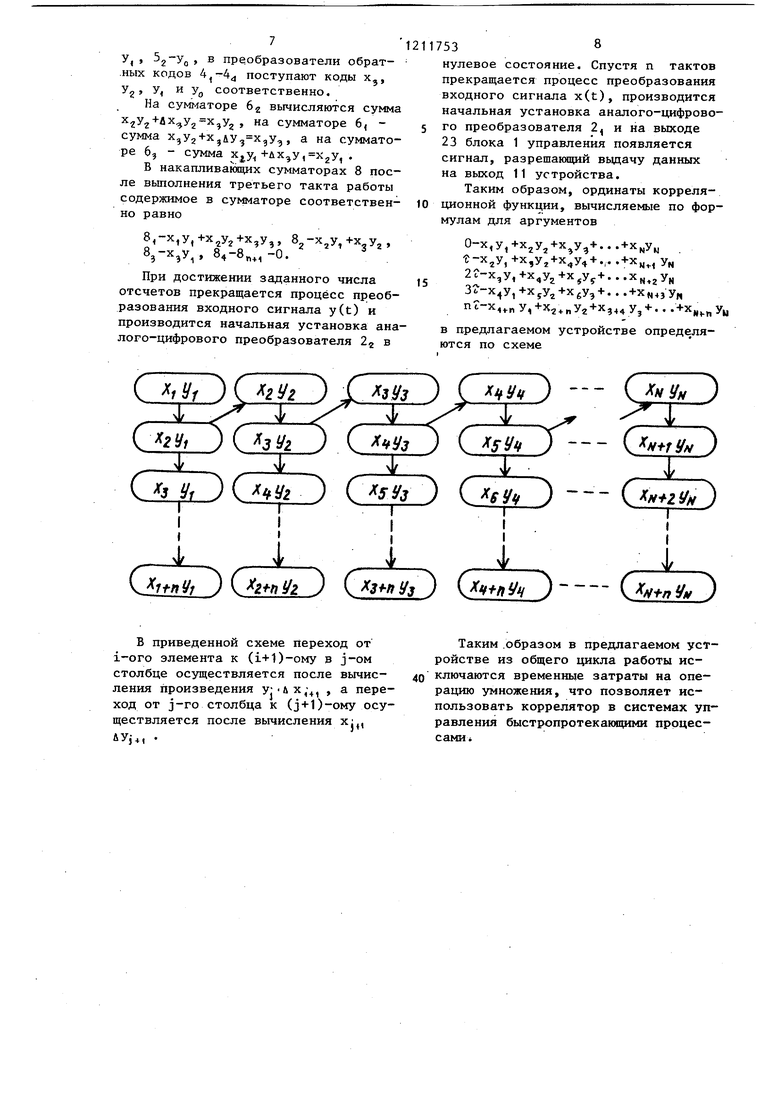

в приведенной схеме переход от i-oro элемента к (1+1)-ому в j-ом столбце осуществляется после вычисления произведения уг ДХ,-, , а переход от j-го столбца к (j+1)-OMy осуществляется после вычисления х;

йУ)4,

211753

нулевое состояние. Спустя п тактов прекращается процесс преобразования входного сигнала x(t), производится начальная установка анапого-цифрово- 5 го преобразователя 2, и на выходе 23 блока 1 управления появляется сигнал, разрешающий выдачу данных на выход 11 устройства.

Таким образом, ординаты корреля- 10 ционной функции, вычисляемые по формулам для аргументов

0-х,у,+Х2У.,+ ...,

15

, , + .,. .+х„, УМ 2 е-х,у,,.+ ... х„,гУ„

,+ХуУг+Х Уэ + ...+ХмчзУ|,

пГ-х,.„у,+х2 + ,

44Уз - - Х,

Хьп УМ

в предлагаемом устройстве опреде ля- ются по схеме

Xityif )

;

т

)

Таким .образом в предлагаемом устройстве из общего цикла работы ис- 40 ключаются временные затраты на операцию умножения, что позволяет использовать коррелятор в системах управления быстропротекающими процессами

фиг.1

Составитель А.Иванова Редактор Т.Парфенова Техред А.Бабинец

Заказ 642/54 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП Патент, г.Ужгород, ул.Проектная, 4

Фе/г.2

Корректор М.Демчнк

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный цифровой коррелятор | 1984 |

|

SU1290352A1 |

| Многоканальный цифровой коррелятор | 1984 |

|

SU1292006A1 |

| Коррелометр | 1982 |

|

SU1026144A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2011 |

|

RU2445690C2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2002 |

|

RU2229157C2 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Цифровой коррелятор | 1980 |

|

SU942038A1 |

| Многоканальный цифровой коррелятор | 1985 |

|

SU1397938A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1273944A1 |

| ПРИЕМНИК СИГНАЛОВ СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 2000 |

|

RU2178894C1 |

| Цифровой коррелятор | 1976 |

|

SU610117A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Грибанов Ю.И., Веселова Г.П., Андреев В.Н | |||

| Автоматические цифровые корреляторы | |||

| М.: Энергия, 1971, с | |||

| Деревянный коленчатый рычаг | 1919 |

|

SU150A1 |

Авторы

Даты

1986-02-15—Публикация

1983-11-05—Подача