сд

00

о сд

4ъ

ас

Изобретение относится к импульсной технике и может быть использовано в качестве входного устройства в интегральных микросхемах для формирования и преобразования уровней напряжения, в частности при формировании сигналов КМДП-схем от входных сигналов ТТЛ уровней.

Цель изобретения - обеспечение защиты входа устройства от статических зарядов при сохранении высокого быстродействия.

Цель достигается путем использования собственных p-n-переходов входных МДП-транзисторов дополнительного типа и изменения соответствующих связей между транзисторами. Указанные р-п переходы, благодаря их подключению между входом устройства и шинами опорных напряжений, выполняют функции защитных пороговых элементов при перенапряжениях на входе устройства обеих полярностей. Вследствие этого устройство не требует специальных средств защиты затворов МДП-транзисторов на входе, что может приводить к снижению быстродействия.

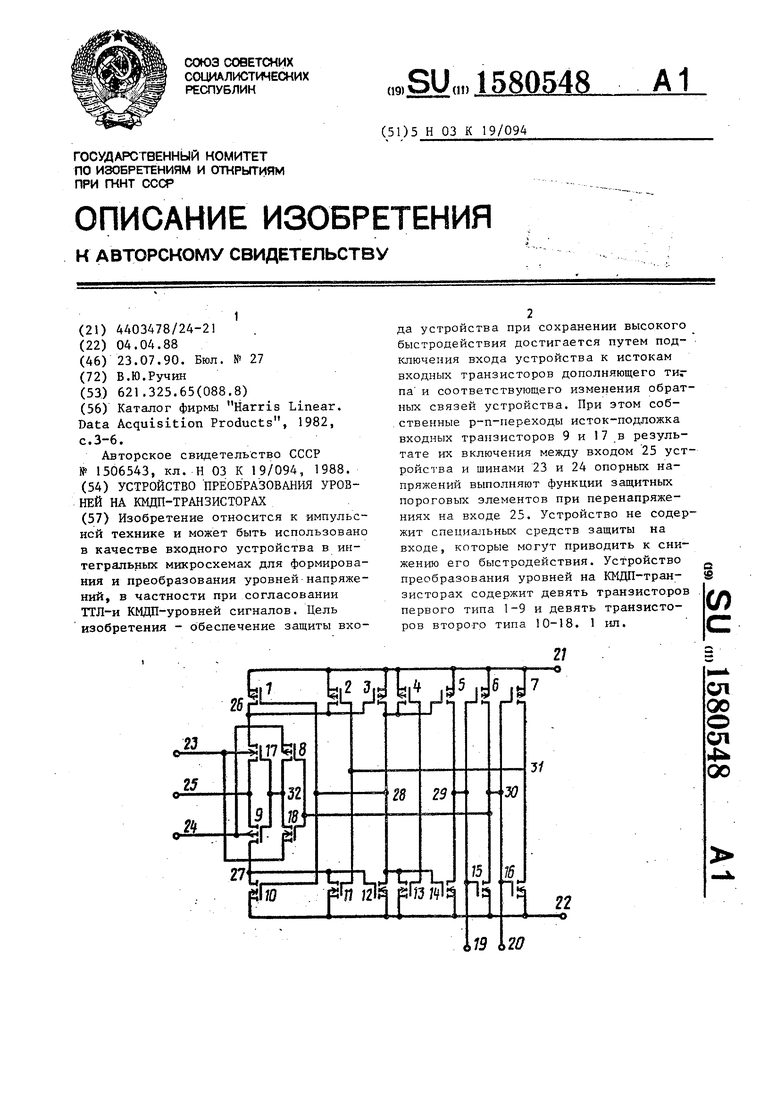

На чертеже приведена принципиальная схема предлагаемого устройства.

Устройство преобразования уровнем на МДП-транзисторах содержит 18 транзисторов 1-18, из которых транзисторы 1-9 первого (например,р) типа, а транзисторы 10-18 второго (дополнительного, п) типа. Затвор первого транзистора 1 соединен с затворами пятого 5, десятого 10 и четырнадцатого 14 транзисторов и стоками третьего 3, четвертого 4, двенадцатого 12 и тринадцатого 13 транзисторов. Затвор второго транзистора 2 соединен с затворами четвертого 4, одиннадцатого 11, тринадцатого 13 транзисторов и со стоками седьмого 7 и шестнадцатого 16 транзисторов. Затвор третьего транзистора 3 соединен со стоком второго транзистора 2, затвор двенадцатого транзистора 12 - со стоком одиннадцатого транзистора 11. Затвор шестого транзистора 6 соединен с затвором пятнадцатого транзистора 15, со стоками пятого 5 и четырнадцатого 14 транзисторов и с выходом 19. Затворы седьмого 7 и шестнадцатого 16 транзисторов соединены и подключены к затворам восьмого 8 и восемнадцатого 18 транзисторов и стокам шестого 6 и пятнадцатого 15 транзисторов и к

JO

20

25

,,

05484

инверсному выходу 20. Затвор семнадцатого 17 транзистора соединен с затвором девятого 9 транзистора. Истоки транзисторов с первого 1 по седьмой 7 подключены к первбй шине 21 питания. Истоки транзисторов с десятого 10 по шестнадцатый 16 подключены ко второй шине 22 питания.

Подложка семнадцатого транзистора 17 подключена к первой шине 23 опорного напряжения, подложка девятого транзистора 9 - ко второй шине 24 опорного напряжения. Вход 25 устройства соединен с истоками семнадцатого 17 и девятого 9 транзисторов. Сток семнадцатого транзистора 17 соединен со стоками первого 1 и второго 2 транзисторов, сток девятого транзистора 9 - со стоками десятого 10 и одиннадцатого 11 транзисторов, сток восьмого транзистора 8 - со стоком восемнадцатого транзистора 18 и с затвором семнадцатого транзистора 17. Исток и подложка восемнадцатого транзистора 18 соединены с первой шиной 23 опорного напряжения, исток и подложка опорного восьмого транзистора - со второй шиной 24 опорного напряжения.

Устройство работает следующим образом.

На первую шину 23 опорного напряжения подается напряжение величиной не менее чем входное напряжение низкого уровня минус пороговое напряжение (по абсолютной величине) МДП-транзис- тора р-типа. На вторую шину 24 опорного напряжения подается напряжение величиной не более чем входное напряжение высокого уровня плюс пороговое напряжение МДП-транзистора п-типа. Например, если источником входного сигнала, подаваемого на вход 25 устройства, служит ТТЛ-схема, указанные напряжения на шинах 23 и 24 опорного напряжения могут быть приняты равными 0 и 5 В, что соответствует напряжениям питания ТТЛ-схемы.

На шины питания 21 и 22 подаются напряжения, необходимые для работы высоковольтных МДП-схем, например плюс 15 и минус 15В. В рассматриваемой схеме уровень напряжения на затворах транзисторов, совпадающий с напряжением на шине 21 питания, открыва- 55 ет транзисторы 10,11,13-16,18 и за-, крывает транзисторы 1-8. Уровень напряжения на затворах транзисторов, совпадающий с напряжением на шине 22

30

35

40

45

50

иктыкия, открывает транзисторы 1-8 и закрывает транзисторы 10-16,18. Транзистор 3 открывается уровнем напряжения, совпадающим с напряжением на шизисторов ,-,12,)3 к затворами транзисторов 5., 14, и 10, уровень напря жения совпадает с напряжением на первой шине питания 21, в узле 29, образованном стоками транзисторов 5 и 14, затворами транзисторов 6 и 15, выходом 19, уровень напряжения совпадает с напряжением на второй шине 22 питане 23 опорного напряжения. Транзистор 12 открывается уровнем напряжения, совпадающим с напряжением на шине 24 опорного напряжения. Транзистор 17 открыт, если на входе 25 сигнал, на- |0 пряжение которого совпадает с напряжением на шине 23 опорного напряжения, а на затворе транзистора 17 напряжение, совпадающее с напряжением на шине 24 опорного напряжения. Транзис- питания, в узле 31, образованном сто- тор 17 закрыт, если на входе 25 и на ками транзисторов 7 и 16, затворами затворе транзистора 17 напряжения одинаковы и совпадают с напряжением на шине 23 или 24 опорного напряжения или если напряжение на входе 25 совпадает on обоазованном стоками транзисторов 8 с напряжением на шине 24 опорного на- и 18 и затворами транзисторов 17 и 9, пряжения, а напряжение на затворе уровень напряжения совпадает с на- транзистора 17 совпадает с напряжени- пряжением на первой шине 23 опорного ем на шине 23 опорного напряжения. Транзистор 9 открыт, если напряжение на входе 25 совпадает с напряжением на шине 24 опорного напряжения, а напряжение на затворе транзистора 9 совпадает с напряжением на шине 23 опорного напряжения. Транзистор 9 закрыт, если напряжения на входе 25 и на затния, в узле 30, образованном стоками транзисторов 6 и 15, затворами транзисторов 7,16,8 и 18 и инверсным выходом 20, уровень напряжения совпадает с напряжением на первой шине 21

транзисторов 4,13, 2 и 11, уровень напряжения совпадает с напряжением на второй шине 22 питания, в узле 32,

напряжения.

25 При подаче на вход 25 уровня напряжения, совпадающего с напряжением на второй шине 24 опорного напряжения, транзистор 9 открывается. В узле 27 устанавливается напряжение, близкое к напряжению на входе 25. Этот уровень напряжения открывает транзистор 12. В узле 28 через открытый транзистор 12 устанавливается уровень напряжения, близкий к напряжению на второй шине 22 питания. Этот уровень

30

воре транзистора 9 одинаковы и совпадают с напряжением HS шинах 23 и 24 опорного напряжения и если напряжение на входе 25 совпадает с напряжением

25 При подаче на вход 25 уровня напряжения, совпадающего с напряжением на второй шине 24 опорного напряжения транзистор 9 открывается. В узле 27 устанавливается напряжение, близкое к напряжению на входе 25. Этот уровень напряжения открывает транзистор 12. В узле 28 через открытый тран зистор 12 устанавливается уровень напряжения, близкий к напряжению на второй шине 22 питания. Этот уровень

на шине 23 опорного напряжения, а на- напряжения открывает транзисторы 1 и 5 пряжение на затворе транзистора 9 и закрывает транзисторы 10 и 14. В

узле 27 напряжение становится равным напряжению сигнала на входе 25.

45

совпадает с напряжением на шине 24 опорного напряжения.

Транзисторы 1, 10, 4 и 13 имеют сокое сопротивление канала в открытом состоянии. Остальные транзисторы имеют низкое сопротивление канала в открытом состоянии.

За исходное состояние примем состояние устройства, установившееся под воздействием уровня напряжения на входе 25, совпадающего с напряжением на шине 23 опорного напряжения. При этом напряжения в узлах следующие: в узле 26, образованном стоками транзисторов 1,2 и 17 и затвором транзистора 3, уровень напряжения совпадает с напряжением в первой шине 21 питания, в узле 27, образованном стоками транзисторов 9,10,11 и затвором транзисто- ра 12, уровень напряжения совпадает с напряжением на второй шине 22 питания, в узле 28, образованном стоками тран50

55

В узле 29 устанавливается напряжение, совпадающее с напряжением на первой шине 21 питания. Это напряжение закрывает транзистор 6 и открывает транзистор 15. В узле 30 устанавливается напряжение, совпадающее с напряжением на второй шине 22 питания Это напряжение открывает транзисторы 7 и 8 и закрывает транзисторы 16 и 18. В узле 31 устанавливается напряжение, совпадающее с напряжением на первой шине 21 питания, что приводит к открыванию транзисторов 11 и 13 и закрыванию транзисторов 2 и 4. В узле 32 устанавливается напряжение, совпадающее с напряжением на второй гакне 24 опорно го напряжения, что приводит к закрыванию транзистора 9.

После закрывания транзистора 9 и I последующего открывания транзистора 1 1

зисторов ,-,12,)3 к затворами транзисторов 5., 14, и 10, уровень напряжения совпадает с напряжением на первой шине питания 21, в узле 29, образованном стоками транзисторов 5 и 14, затворами транзисторов 6 и 15, выходом 19, уровень напряжения совпадает с напряжением на второй шине 22 питапитания, в узле 31, образованном сто- ками транзисторов 7 и 16, затворами обоазованном стоками транзисторов 8 и 18 и затворами транзисторов 17 и 9, уровень напряжения совпадает с на- пряжением на первой шине 23 опорного

питания, в узле 31, образованном сто- ками транзисторов 7 и 16, затворами обоазованном стоками транзисторов 8 и 18 и затворами транзисторов 17 и 9, уровень напряжения совпадает с на- пряжением на первой шине 23 опорного

ния, в узле 30, образованном стоками транзисторов 6 и 15, затворами транзисторов 7,16,8 и 18 и инверсным выходом 20, уровень напряжения совпадает с напряжением на первой шине 21

питания, в узле 31, образованном сто- ками транзисторов 7 и 16, затворами обоазованном стоками транзисторов 8 и 18 и затворами транзисторов 17 и 9, уровень напряжения совпадает с на- пряжением на первой шине 23 опорного

транзисторов 4,13, 2 и 11, уровень напряжения совпадает с напряжением на второй шине 22 питания, в узле 32,

питания, в узле 31, образованном сто- ками транзисторов 7 и 16, затворами обоазованном стоками транзисторов 8 и 18 и затворами транзисторов 17 и 9, уровень напряжения совпадает с на- пряжением на первой шине 23 опорного

напряжения.

При подаче на вход 25 уровня напряжения, совпадающего с напряжением на второй шине 24 опорного напряжения, транзистор 9 открывается. В узле 27 устанавливается напряжение, близкое к напряжению на входе 25. Этот уровень напряжения открывает транзистор 12. В узле 28 через открытый транзистор 12 устанавливается уровень напряжения, близкий к напряжению на второй шине 22 питания. Этот уровень

В узле 29 устанавливается напряжение, совпадающее с напряжением на первой шине 21 питания. Это напряжение закрывает транзистор 6 и открывает транзистор 15. В узле 30 устанавливается напряжение, совпадающее с напряжением на второй шине 22 питания. Это напряжение открывает транзисторы 7 и 8 и закрывает транзисторы 16 и 18. В узле 31 устанавливается напряжение, совпадающее с напряжением на первой шине 21 питания, что приводит к открыванию транзисторов 11 и 13 и закрыванию транзисторов 2 и 4. В узле 32 устанавливается напряжение, совпадающее с напряжением на второй гакне 24 опорного напряжения, что приводит к закрыванию транзистора 9.

После закрывания транзистора 9 и I последующего открывания транзистора 1 1

в узле 27 устанавливается исходное напряжение, совпадающее с напряжением на второй шине 22 питания. Это напряжение закрывает транзистор 12. Уровень напряжения, установившийся в узле 28, сохраняется благодаря открытому транзистору 13 Напряжение в узле 26 от указанного воздействия не изменяется,совпадает с напряжением на первой шине 21 питания и поддерживается на этом уровне после закрывания транзистора 2 открывшимся транзистором 1 . Установившееся на затворе транзистора 17 напряжение, совпадающее с напряжением на второй шине 24 опорного напряжения, подготавливает устройство к следующему переключению по входному сигналу, совпадающему по уровню напряжения с напряжением на первой шине 23 опорного напряжения.

Подача на вход 25 этого сигнала приводит к открыванию транзистора 17. Через открытый транзистор 17 в узле 26 устанавливается напряжение,близкое к напряжению входного сигнала, совпадающего с напряжением на первой шине 23 опорного напряжения. Открывается транзистор 3. В узле 28 устанавливается напряжение, близкое к напряжению на первой шине 21 питания. Закрывается транзистор 1, и в узле 26 устанавливается напряжение, совпадающее с напряжением входного сигнала. Далее переключение узлов происходит в той же последовательности, которая приведена для первого переключающего сигнала. В результате этих переключений на затворах транзисторов 17 и 9 устанавливается напряжение, совпадающее с напряжением на первой шине 23 опорного напряжения. Транзистор 17 закрывается. Транзистор 9 закрыт и подготовлен к следующему переключению. На затворах транзисторов 2, 4, 10 и 13 устанавливается уровень напряжения, совпадающий с напряжением на вто- i рой шине 22 питания. Через открытый транзистор 2 в узле 26 устанавливается напряжение, совпадающее с напр жением, на первой шине 2 питания. Транзистор 3 закрывается. Уровень напряжения в узле 28 сохраняется открытым транзистором 4. Уровень напряже- . ния в узле 27 от указанного второго входного воздействия не изменяется, совпадает с напряжением Hd второй шине 22 питания и поддерживается на этом

5

0

5

0

5

0

5

0

5

уровне после закрывания транзистора 1 1 открывшимся транзистором 1 О,

Полученное состояние устройства соответствует принятому за исходное в начале рассмотрения процессов.

Благодаря тому, что вход 25 устройства соединен с токовыми электродами транзисторов 9 и 1 7 , подложки которых подключены к источнику опорных напряжений, а не с затворами МДП-транзисто- ров, как обычно, в том числе в известном устройстве, в предлагаемом устройстве дополнительно обеспечивается электростатическая защита входа устройства от перенапряжений обеих полярностей. При этом функции защитных пороговых элементов выпол няют р-п-переходы самих входных транзисторов 9 и 17, поэтому предлагаемое устройство не тре- бует дополнительных средств защиты, выполняемых на диодно-резистивных элементах, введение которых может снижать быстродействие устройства.

Схема устройства позволяет использовать его при работе на большую емкостную нагрузку (сотни пикофарад).

Формула изобретения

Устройство преобразования уровней на КМДП-транзисторах, содержащее восемнадцать транзисторов, из которых первые девять - первого типа, а остальные - второго типа проводимости, истоки и подложки транзисторов с первого по седьмой подключены к первой шине питания, а истоки и подложки транзисторов с десятого до шестнадцатый - к второй шине питания, стоки первого и второго, затвор третьего и сток семнадцатого транзисторов объединены, стоки десятого, одиннадцатого, затвор двенадцатого и сток девятого транзисторов также объединены, стоки третьего, четвертого, двенадцатого и тринадцатого, затворы первого и десятого транзисторов подключены к объединенным затворам пятого и четырнадцатого транзисторов, стоки которых соединены с объединенными затворами шестого и пятнадцатого транзисторов и подключены к выходу устройства, стоки шестого и пятнадцатого объединены и подключены к инверсному выходу устройства и к затворам седьмого и шестнадцатого транзисторов, стоки которых объединены, исток и подложка восемнадцатого и подложка семнадцатого тран9158054810

зисторов подключены к первой шинева от статических зарядов при сохранеопорного напряжения, а исток и подлож-нии высокого быстродействия, истоки

ка во сьмого и подложка девятого тран-девятого и семнадцатого-транзисторов

зисторов подключены к второй шинеобъединены и подключены к входу устопорного напряжения, затворы девятого,5ройства, а затворы тех же транзистосемнадцатого, а также восьмого и во-Ров подключены к объединенным стокам

семнадцатого, второго и одиннадцатоговосьмого и восемнадцатого транзисторов,

транзисторов попарно объединены, о т -затворы которых соединены с инверсличающеес,я тем, что, с це- 10ным вькодом, а затвор второго и сток

лью обеспечения защиты входа устройст-седьмого транзисторов объединены.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство преобразования уровней сигналов на КМДП-транзисторах | 1988 |

|

SU1506543A1 |

| Формирователь адресных сигналов | 1982 |

|

SU1049967A1 |

| Аналоговый переключатель | 1986 |

|

SU1385288A1 |

| Формирователь импульсов | 1982 |

|

SU1238230A1 |

| Аналоговый четырехквадрантный перемножитель | 1988 |

|

SU1504655A1 |

| УСИЛИТЕЛЬ ЗАПИСИ-СЧИТЫВАНИЯ ДЛЯ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1987 |

|

SU1612801A1 |

| Аналоговый четырехквадрантный перемножитель | 1987 |

|

SU1478229A1 |

| Буферный усилитель (его варианты) | 1983 |

|

SU1112409A1 |

| Коммутатор напряжений | 1988 |

|

SU1524168A1 |

| Триггер со счетным входом на взаимодополняющих МДП-транзисторах | 1989 |

|

SU1622925A1 |

Изобретение относится к импульсной технике и может быть использовано в качестве входного устройства в интегральных микросхемах для формирования и преобразования уровней напряжений, в частности при согласовании ТТЛ- и КМДП-уровней сигналов. Цель изобретения - обеспечение защиты входа устройства при сохранении высокого быстродействия достигается путем подключения входа устройства к истокам входных транзисторов дополняющего типа и соответствующего изменения обратных связей устройства. При этом собственные P-N-переходы исток-подложка входных транзисторов 9 и 17 в результате их включения между входом 25 устройства и шинами 23 и 24 опорных напряжений выполняют функции защитных пороговых элементов при перенапряжениях на входе. Устройство не содержит специальных средств защиты на входе, которые могут приводить к снижению его быстродействия. Устройство преобразования уровней на КМДП-транзисторах содержит девять транзисторов первого типа 1-9 и девять транзисторов второго типа 10-18. 1 ил.

| Каталог фирмы Harris Linear | |||

| Data Acquisition Products, 1982, с.3-6 | |||

| Устройство преобразования уровней сигналов на КМДП-транзисторах | 1988 |

|

SU1506543A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-07-23—Публикация

1988-04-04—Подача