ы

Ј

Изобретение относится к вычислитель ной технике и можег быть использовано при построении цифровых интегральных схем на МДП-транзисторах.

Целью изобретения является расширение области применения устройства.

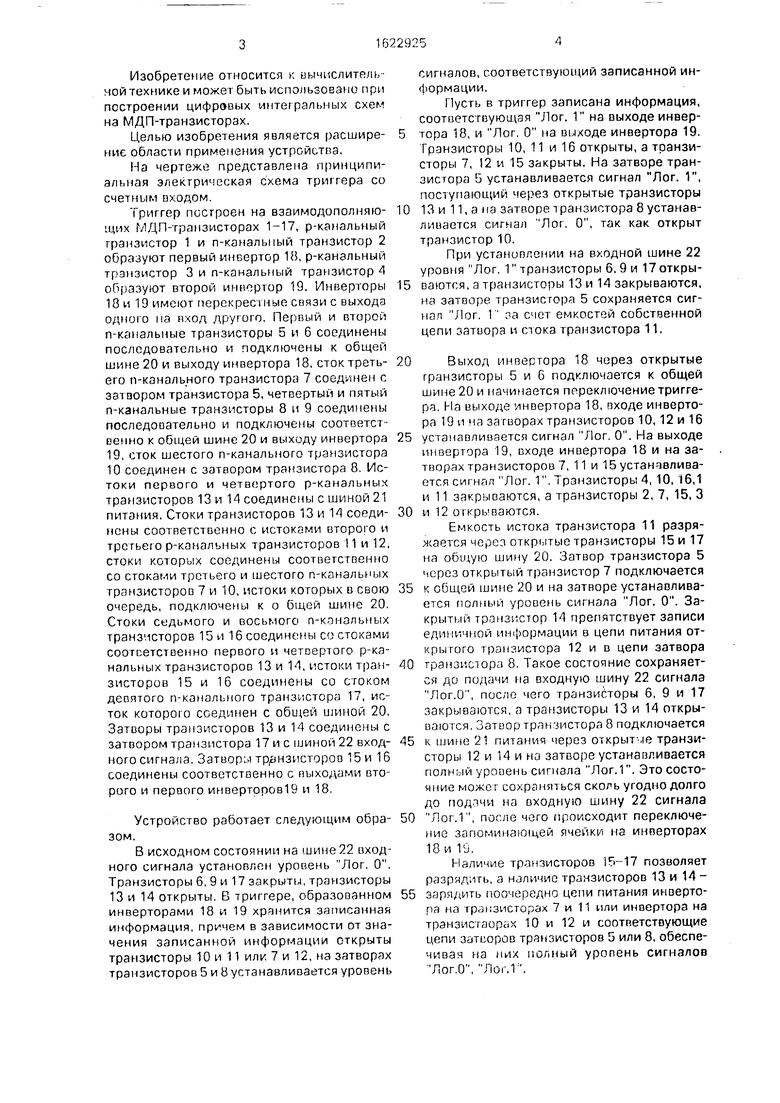

На чертеже представлена принципиальная электрическая схема тршгера со счетным входом.

Триггер построен на взаимодополняющих МДП-грапзисторах 1-17, р-канальный транзистор 1 и п-канальпый транзистор 2 образуют первый инвертор 18, р-канальный транзистор 3 и n-канальный транзистор 4 образуют второй инворюр 19. Инверторы 10 и 19 имеют перекресшые связи с выхода одною на вход друтго. Первый и второй n-канальные транзисторы 5 и 6 соединены последовательно и подключены к общей шине 20 и выходу инвертора 18, сток третьего п-канального транзистора 7 соединен с затвором транзистора 5, четвертый и пятый n-канальные транзисторы 8 и 9 соединены последовательно и подключены соответственно к общей шине 20 и выходу инвертора 19, сток шестого n-канального транзистора 10 соединен с затвором транзистора 8. Истоки первого и четвертого р-канальных транзисторов 13 и 14 соединены с шиной 21 питания. Стоки транзисторов 13 и 14 соединены соответственно с истоками второго и третьего р-канальных транзисторов 11 и 12, стоки которых соединены соответственно со стоками третьего и шестого rs-канальных транзисторов 7 и 10, истоки которых в свою очередь, подключены к о бщей шине 20. Стоки седьмого и восьмого п-кональных транзисторов 15 и 16 соединены со стоками соответственно первого и четвертого р-канальных транзисторов 13 и 14,истоки транзисторов 15 и 16 соединены со стоком девятого п-канального транзистора 17, исток которою соединен с общей шиной 20. Затворы транзисторов 13 и 14 соединены с затвором транзистора 17 и с шиной 22 входного сигнала. Затворы транзисторов 15 и 16 соединены соответственно с выходами второго и первого инверторов19 и 18.

Устройство работает следующим образом.

В исходном состоянии на шине 22 входного сигнала установлен уровень Лог. О. Транзисторы 6, 9 и 17 закрыты, транзисторы 13 и 14 открыты. В триггере, образованном инверторами 18 и 19 хранится записанная информация, причем в зависимости от значения записанной информации открыты транзисторы 10 и 11 или 7 и 12, на затворах транзисторов 5 и 8 устанавливается уровень

сигналов, соответствующий записанной информации.

Пусть в триггер записана информация, соответствующая Лог. 1 на выходе инвер- тора 18, и Лог. О на выходе инвертора 19. Транзисторы 10, 11 и 16 открыты, а транзисторы 7, 12 и 15 закрыты. На затворе транзистора Б устанавливается сигнал Лог. 1, поступающий через открытые транзисторы 13 и 11, а на затворе транзистора 8 устанавливается сигнал Лог. О, так как открыт транзистор 10.

При установлении на входной шине 22 уровня Лог. 1 транзисторы 6.9 и 17 откры- ваются, а транзисторы 13 и 14 закрываются, на затворе транзистора 5 сохраняется сиг- пап Лог. 1 за счет емкостей собственной цепи затвора и стока транзистора 11.

Выход инвертора 18 через открытые транзисторы 5 и 6 подключается к общей шине 20 и начинается переключение триггера. На выходе инвертора 18, входе инвертора 19 и чпза гворах транзисторов 10, 12 и 16

устанавливается сигнал Лог. О. На выходе инвертора 19, входе инвертора 18 и на затворах транзисторов 7, 11 и 15 устанавливается сигнал Лог. 1. Транзисторы 4, 10, 16,1 и 11 закрываются, а транзисторы 2, 7, 15, 3

и 12 открываются.

Емкость истока транзистора 11 разряжается через открытые транзисторы 15 и 17 на общую шину 20. Затвор транзистора 5 через открытый транзистор 7 подключается

к общей шине 20 и на затворе устанавливается полный уровень сигнала Лог. О. Закрытый транзистор 14 препятствует записи единичной информации в цепи питания открытого транзистора 12 и в цепи затвора

транзистора 8. Такое состояние сохраняется до подачи па входную шину 22 сигнала Лог.О, после чего транзисторы 6, 9 и 17 закрываются, а транзисторы 13 и 14 открываются. Затоор транзистора 8 подключается

к шине 21 питания через открытме транзисторы 12 и 14 и на затворе устанавливается полный уровень сигнала Лог.1. Это состояние можег сохраняться сколь угодно долго до подччи на входную шину 22 сигнала

Лог.1 , после чего происходит переключение запоминающей ячейки на инверторах 18 и 1(j.

Наличие транзисторов позволяет разрядить, а наличие транзисторов 13 и 14 зарядить поочередно цепи питания инвертора на транзисторах 7 и 11 или инвертора на транзисгаорах 10 и 12 и соответствующие цепи Зсггсоров транзисторов 5 или 8, обеспечивая на них полный уровень сигналов Tior.O, Ло(.1.

Формула изобретения

Триггер со счетным входом на взаимодополняющих МДП-транзисторах, содержащий два инвертора с перекрестными связями с выхода одного инвертора и на вход другого, три р-канальных и шесть п-ка- нальных транзисторов, сток первого и исток второго последовательно соединенных п- канальных транзисторов соединены соот- ветственно с выходом первого инвертора и общей шиной, сток третьего п-канального транзистора, соединен с затвором порвого n-канального транзистора сток четвертого и исток пятого последовательно соединенных n-канальных транзисторов соединены соответственно с выходом второго инвертора и общей шиной, затворы второго и пятого п- канальных транзисторов и затвор первого р-канального транзистора соединены с ши- ной входного сигнала, исток первого р-ка- нального транзистора соединен с шиной питания, а его сток соединен с истоком второго р-канального транзистора, сток которого соединен со стоком третьего n-канального транзистора, затворы второго р-канального и третьего n-канального транзисторов соединены с выходом второго инвертора, стоки третьего р-канального и шестого n-канального транзисторов соединены с затвором четвертого п-канального транзистора, а их затворы соединены с выходом первого инвертора, истоки третьего и шестого n-канальных транзисторов соединены с общей шиной, отличающи и - с я тем, что, с целью расширения его области применения, введены седьмой, восьмой и девятый n-канальные и четвертый р-канальный транзисторы, причем исток четвертого р-канального транзистора соединен с шиной питания, а его сток соединен с истоком третьего р-канального и стоком восьмого n-канального транзисторов, сток седьмого п-канального транзистора соединен со стоком первого р-канального транзистора, истоки седьмого и восьмого п- канальных транзисторов соединены со стоком девятого n-канального транзистора, а их затворы соединены соответственное выходами второго и первого инверторов, затворы четвертого р-канального и девятого п-канального транзисторов соединены с шиной входного сигнала, исток девятого п-канального транзистора соединен с общей шиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггер со счетным входом на взаимодополняющих МДП-транзисторах | 1987 |

|

SU1492452A1 |

| Аналоговый переключатель | 1986 |

|

SU1385288A1 |

| Тактируемый триггер на комплементарных МДП-транзисторах | 1985 |

|

SU1499435A1 |

| Устройство преобразования уровней сигналов на КМДП-транзисторах | 1988 |

|

SU1506543A1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ | 1995 |

|

RU2107387C1 |

| Устройство преобразования уровней на КМДП-транзисторах | 1988 |

|

SU1580548A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1981 |

|

SU963087A1 |

| Двоичный счетчик | 1984 |

|

SU1282321A1 |

| Формирователь импульсов на МДП-транзисторах | 1985 |

|

SU1569973A1 |

| Коммутатор напряжений | 1988 |

|

SU1524168A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении цифровых интегральных схем на МДП-транзисторах. Цель изобретения - расширение области применения устройства. Триггер содержит инверторы 18 и 19 и шину 22 входного сигнала. Введение МДП- транзисторов 14-17 позволяет исключить зависимость длительности входных сигналов от длительности переходных процессов в триггере. 1 ил.

| Триггер со счетным входом на взаимодополняющих МДП-транзисторах | 1987 |

|

SU1492452A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-01-23—Публикация

1989-01-03—Подача