1

(21) 4494765/24-21

(22) 14.10.88

(46) 30.07.90. Бюл. № 28

(72) В.Ф.Криворучко, Г.М.Попова,

С.Ф.Кибирев и Е.А.Шаламов

(53)681.324(088,8)

(56)Баранов С.И., Скляров В.А. Цифровые устройства на программируемых БИС с матричной структурой. М.: Радио и связь, 1986.

EPLD Handbook, Altera corporation, 1984.

(54)ЛОГИЧЕСКАЯ МАТРИЦА С ПРОГРАММИРУЕМОЙ ПАМЯТЬЮ

(57)Изобретение относится к вычислительной технике и может быть использовано для реализации управляющих и коммутирующих устройств в микропроцессорных системах. Цель изобретения - увеличение информационной емкости логической матрицы, достигаемое путем динамической перестройки триггеров. Устройство содержит с первого по четвертый блоки 1-4 памяти, с первого по N-й коммутационные блоки , блок 6 дешифраторов, вход 7 начальной установки устройства, группу управляющих входов 8, первые 9-12 и вторые адресные входы с первого по четвертый блоков памяти, а также информационные выходы этих блоков, первые группы входов 21 ) и выходов 22, вход-выход 23, синхро- вход 24, вход 25 начальной установки, группу управляющих входов 26 1-го коммутационного блока, первый 27 и аторой 28 синхровходы устройстёа, вторые группы выходов 29 и информационных входов 30 1-го коммутационного блока. 1 з.п. ф-лы, 3 ил.

е SS

(Л

с

31

Изобретение относится к вычислительной технике и может быть использовано для реализации управляющих и коммутирующих устройств в микропроцессорных системах.

Цель изобретения - увеличение информационной емкости матрицы путем динамической перестройки триггеров.

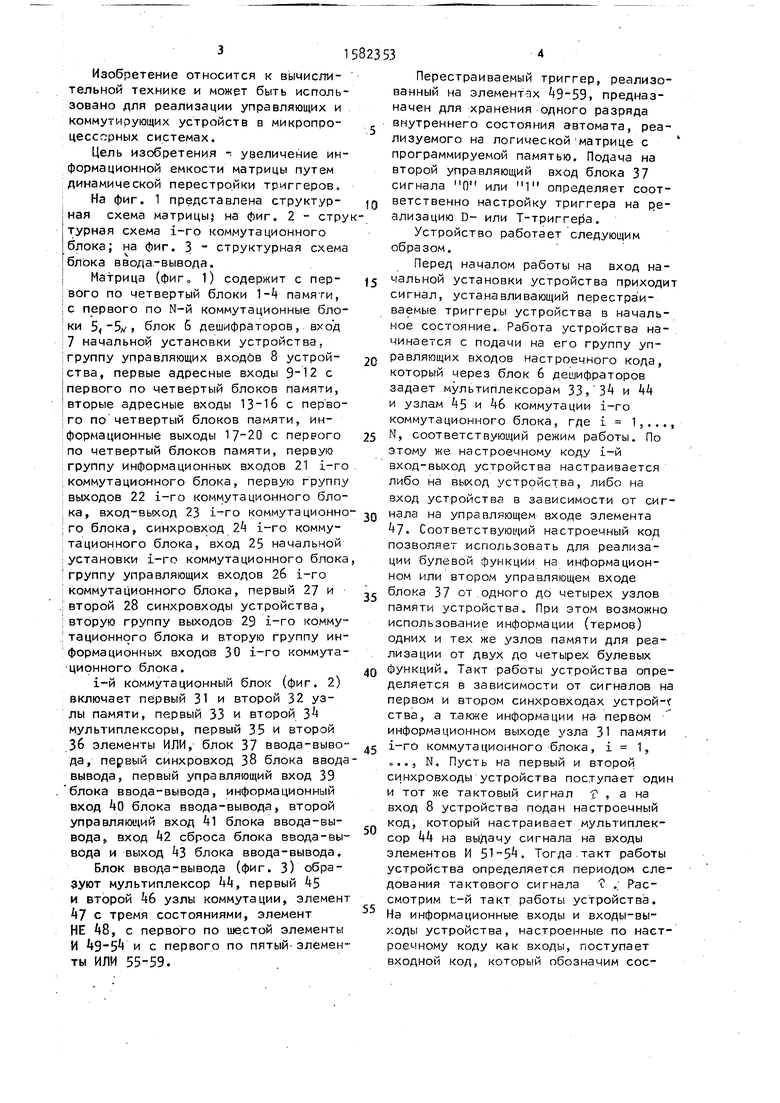

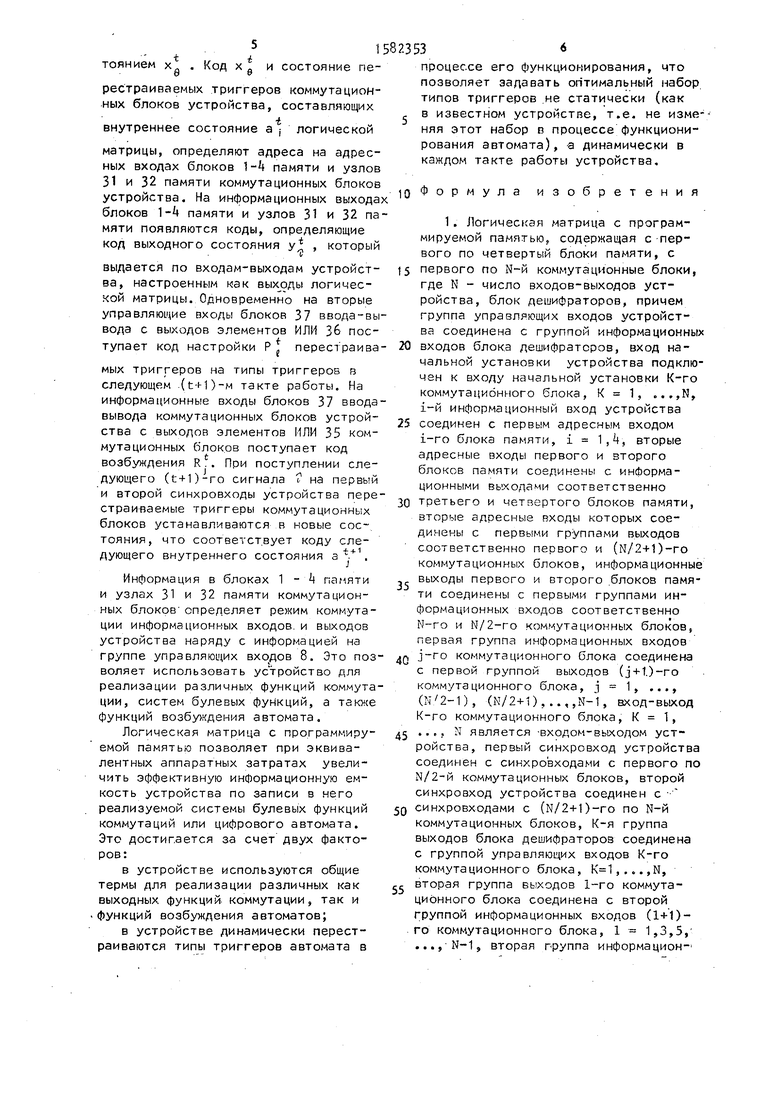

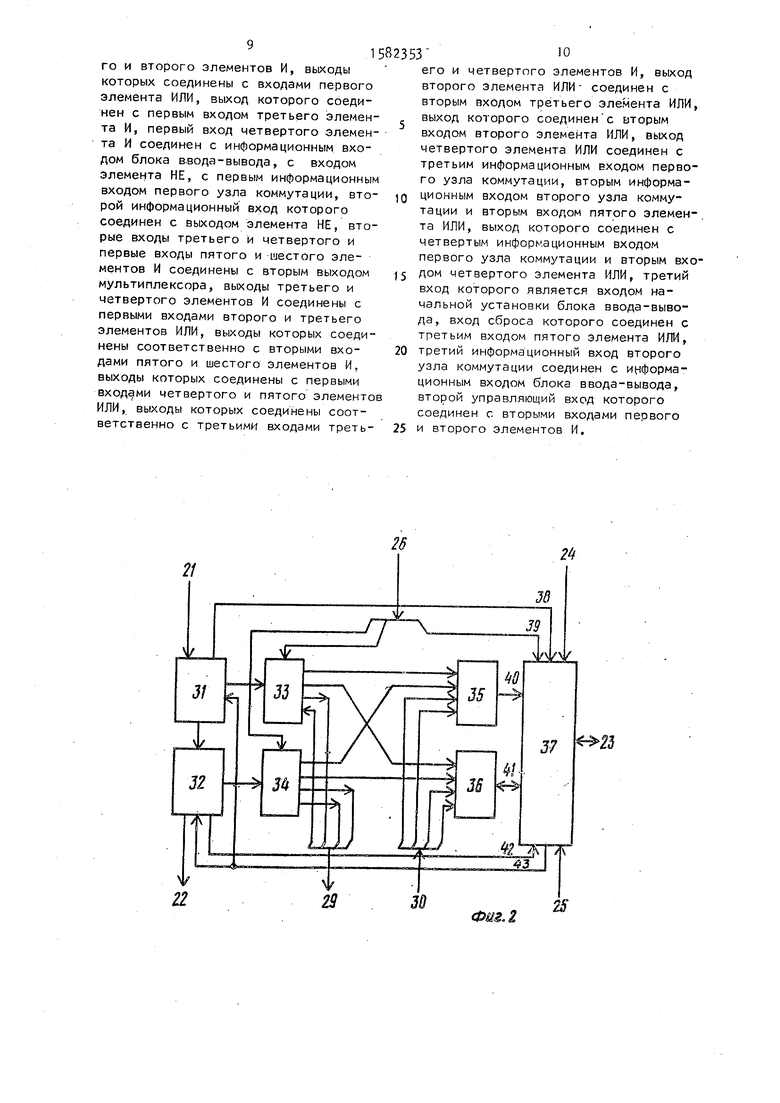

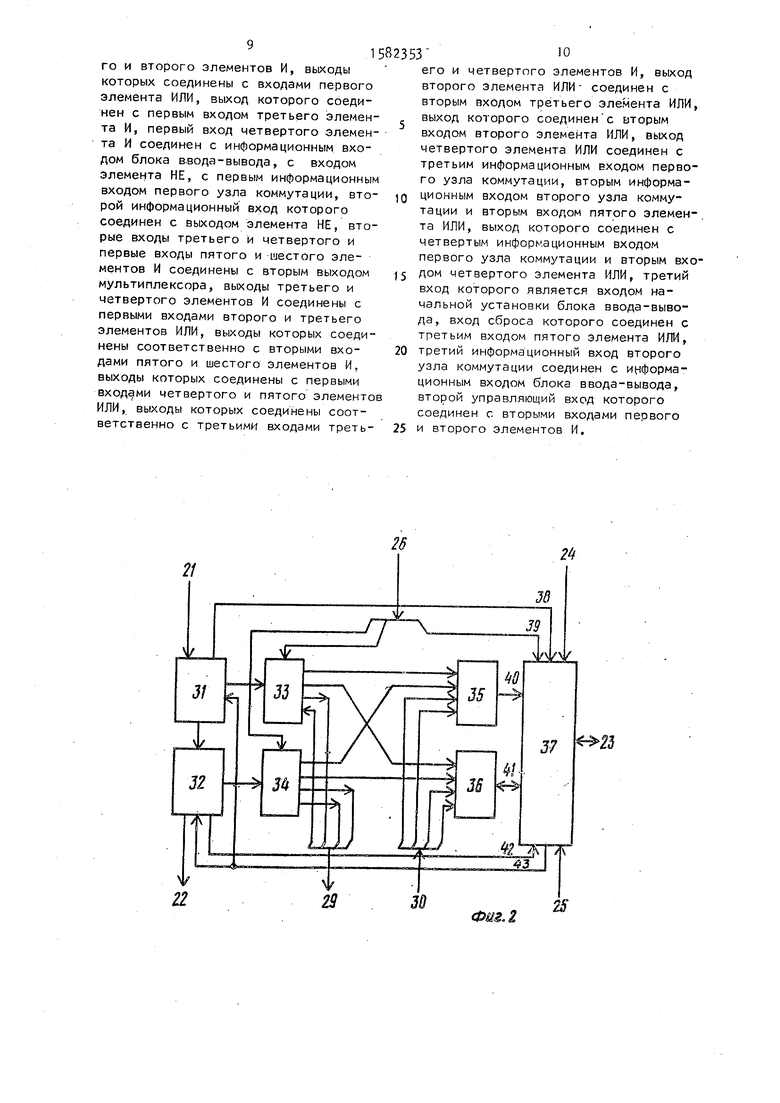

На фиг. 1 представлена структур- ная схема матрицы; на фиг. 2 - струтурная схема 1-го коммутационного блока; на фиг. 3 - структурная схема блока ввода-вывода.

Матрица (фиг 1) содержит с пер- вого по четвертый блоки 1-4 памяти, с первого по N-й коммутационные блоки 54 блок б дешифраторов, вход 7 начальной установки устройства, группу управляющих входов 8 устрой- ства, первые адресные входы с первого по четвертый блоков памяти, вторые адресные входы 13-16 с первого по четвертый блоков памяти, информационные выходы с первого по четвертый блоков памяти, первую группу информационных входов 21 1-го коммутационного блока, первую группу выходов 22 1-го коммутационного бло

Перестраиваемый триггер, реализованный на элементах , предназначен для хранения одного разряда внутреннего состояния автомата, реализуемого на логической матрице с программируемой памятью. Подача на второй управляющий вход блока 37 сигнала О или 1 определяет соответственно настройку триггера на реализацию D- или Т-триггер а.

Устройство работает следующим образом.

Перед началом работы на вход начальной установки устройства приходи сигнал, устанавливающий перестраиваемые триггеры устройства в начальное состояние. Работа устройства начинается с подачи на его группу управляющих входов настроечного кода, который через блок б дешифраторов задает мультиплексорам 33, 34 и 44 и узлам 45 и 46 коммутации 1-го коммутационного блока, где i 1,... N, соответствующий режим работы. По этому же настроечному коду i-и вход-выход устройства настраивается либо на выход устройства, либо на вход устройства в зависимости от сиг

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО БУФЕРИЗАЦИИ И СИНХРОНИЗАЦИИ ДЛЯ ОБРАБОТКИ НЕПРЕРЫВНОГО СИГНАЛА | 1990 |

|

SU1812885A1 |

| Коммутационное устройство | 1989 |

|

SU1672464A1 |

| Коммутационное устройство | 1989 |

|

SU1645963A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Логический анализатор | 1987 |

|

SU1476474A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ МОНТАЖА, ПАРАМЕТРОВ ЭЛЕКТРИЧЕСКИХ ЦЕПЕЙ И ДИАГНОСТИКИ НЕИСПРАВНОСТЕЙ СЛОЖНЫХ УСТРОЙСТВ ЭЛЕКТРОАППАРАТУРЫ И ТОКОРАСПРЕДЕЛИТЕЛЬНЫХ СЕТЕЙ | 2008 |

|

RU2377585C1 |

| Коммутационное устройство | 1990 |

|

SU1730635A1 |

| Матричный процессор | 1987 |

|

SU1534466A1 |

| МНОГОМОДУЛЬНОЕ УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ТЕКСТОВОЙ И ГРАФИЧЕСКОЙ ИНФОРМАЦИИ | 1992 |

|

RU2037885C1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1987 |

|

SU1472913A1 |

Изобретение относится к вычислительной технике и может быть использовано для реализации управляющих и коммутирующих устройств в микропроцессорных системах. Цель изобретения - увеличение информационной емкости логической матрицы, достигаемое путем динамической перестройки триггеров. Устройство содержит с первого по четвертый блоки 1 - 4 памяти, с первого по N-й коммутационные блоки 5 1 - 5 N, блок 6 дешифраторов, вход 7 начальной установки устройства, группу управляющих входов 8, первые 9 - 12 и вторые 13 - 16 адресные входы с первого по четвертый блоков памяти, а также информационные выходы 17 - 20 этих блоков, первые группы входов 21 и выходов 22, вход-выход 23, синхровход 24, вход 25 начальной установки управляющих входов 26 I-го коммутационного блока, первый 27 и второй 28 синхровходы устройства, вторые группы выходов 29 и информационных входов 30 I-го коммутационного блока. 1 з.п. ф-лы, 3 ил.

ка, вход-выход 23 1-го коммутационно- о нала на управляющем входе элемента го блока, синхровход 24 1-го комму- 47. Соответствующий настроечный код

тационного блока, вход 25 начальной установки 1-го коммутационного блока группу управляющих входов 26 1-го коммутационного блока, первый 27 и второй 28 синхровходы устройства, вторую группу выходов 29 1-го коммутационного блока и вторую группу информационных входов 30 1-го коммутационного блока.

i-й коммутационный блок (фиг. 2) включает первый 31 и второй 32 узлы памяти, первый 33 и второй 34 мультиплексоры, первый 35 и второй 36 элементы ИЛИ, блок 37 ввода-вывода, первый синхровход 38 блока ввода вывода, пеовый управляющий вход 39 блока ввода-вывода, информационный вход 40 блока ввода-вывода, второй управляющий вход 41 блока ввода-вывода, вход 42 сброса блока ввода-вывода и выход 43 блока ввода-вывода. Блок ввода-вывода (фиг. 3) образуют мультиплексор 44, первый 45 и второй 46 узлы коммутации, элемент 4 с тремя состояниями, элемент НЕ 48, с первого по шестой элементы И и с первого по пятый элементы ИЛИ 55-59.

5

0

5

0

5

позволяет использовать для реализации булевой функции на информационном или втором управляющем входе блока 37 от одного до четырех узлов памяти устройства. При этом возможно использование информации (термов) одних и тех же узлов памяти для реализации от двух до четырех булевых функций. Такт работы устройства определяется в зависимости от сигналов на первом и втором синхровходах устрой-г ства, а также информации на первом информационном выходе узла 31 памяти 1-го коммутационного блока, , о.., N. Пусть на первый и второй синхровходы устройства поступает один и тот же тактовый сигнал Т , а на вход 8 устройства подан настроечный код, который настраивает мультиплексор 44 на выдачу сигнала на входы элементов И 51-54. Тогда такт работы устройства определяется периодом следования тактового сигнала Т . Рассмотрим t-й такт работы устройства. На информационные входы и входы-выходы устройства, настроенные по настроечному коду как входы, поступает входной код, который обозначим соетоянием х . Код х. и состояние пео У

рестраиваемых триггеров коммутационных блоков устройства, составляющих

внутреннее состояние а , логической

матрицы, определяют адреса на адресных входах блоков 1-4 памяти и узлов 31 и 32 памяти коммутационных блоков устройства. На информационных выходах блоков 1-4 памяти и узлов 31 и 32 памяти появляются коды, определяющие

процессе его функционирования, что позволяет задавать оптимальный набор типов триггеров не статически (как , в известном устройстве, т.е. не изме- няя этот набор в процессе функционирования автомата), а динамически в каждом такте работы устройства,

Ю Формула изобретения

код выходного состояния уД , который

t

выдается по входам-выходам устройства, настроенным как выходы логической матрицы. Одновременно на вторые управляющие входы блоков 37 ввода-вывода с выходов элементов ИЛИ 3& поступает код настройки Р

мых триггеров на типы триггеров в следующем (сН)-м такте работы. На информационные входы блоков 37 ввода- вывода коммутационных блоков устройства с выходов элементов ИЛИ 35 коммутационных блоков поступает код возбуждения R. При поступлении сле1. Логическая матрица с программируемой памятью, содержащая с первого по четвертый блоки памяти, с

15 первого по N-й коммутационные блоки, где N - число входов-выходов устройства, блок дешифраторов, причем группа управляющих входов устройства соединена с группой информационных переелраива- 20 входов блока дешифраторов, вход начальной установки устройства подключен к входу начальной установки К-го коммутационного блока, К 1, „..,N, i-й информационный вход устройства

25 соединен с первым адресным входом 1-го блока памяти, i 1,4, вторые адресные входы первого и второго блоков памяти соединены с информационными выходами соответственно

дующего (t+1)-ro сигнала на первый

и второй синхровходы устройства пере- тоетьего и четвертого бжжов памяти

страиваемые триггеры коммутационных

вторые адресные входы которых соединены с первыми группами выходов соответственно первого и (М/2+1)-го коммутационных блоков, информационные выходы первого и второго блоков памяти соединены с первыми группами информационных входов соответственно N-ro и N/2-го коммутационных блоков, первая группа информационных входов j-ro коммутационного блока соединена с первой группой выходов (j+1)-ro коммутационного блока, j 1, ...,

блоков устанавливаются в новые состояния, что соответствует коду следующего внутреннего состояния at + 1.

Информация в блоках 1 - 4 памяти и узлах 31 и 32 памяти коммутационных блоков определяет режим коммутации информационных входов и выходов устройства наряду с информацией на группе управляющих входов 8. Это позволяет использовать устройство для реализации различных функций коммутации, систем булевых функций, а также функций возбуждения автомата.

Логическая матрица с программируемой памятью позволяет при эквивалентных аппаратных затратах увеличить эффективную информационную емкость устройства по записи в него реализуемой системы булевых функций коммутаций или цифрового автомата. Это достигается за счет двух факторов:

в устройстве используются общие термы для реализации различных как выходных функций коммутации, так и функций возбуждения автоматов;

в устройстве динамически перестраиваются типы триггеров автомата в

процессе его функционирования, что позволяет задавать оптимальный набор типов триггеров не статически (как в известном устройстве, т.е. не изме- няя этот набор в процессе функционирования автомата), а динамически в каждом такте работы устройства,

Формула изобретения

вторые адресные входы которых соединены с первыми группами выходов соответственно первого и (М/2+1)-го коммутационных блоков, информационные выходы первого и второго блоков памяти соединены с первыми группами информационных входов соответственно N-ro и N/2-го коммутационных блоков, первая группа информационных входов j-ro коммутационного блока соединена с первой группой выходов (j+1)-ro коммутационного блока, j 1, ...,

(N 2-1), (N/2+1)N-1, вход-выход

К-го коммутационного блока, К 1, .... N является входом-выходом устройства, первый синхровход устройства соединен с синхро входами с первого по N/2-й коммутационных блоков, второй синхровход устройства соединен с Q синхровходами с (N/2+1)-ro по N-й коммутационных блоков, К-я группа выходов блока дешифраторов соединена с группой управляющих входов К-го коммутационного блока, ,...,N, вторая группа выходов 1-го коммутационного блока соединена с второй группой информационных входов (1+1)- го коммутационного блока, 1 1,3,5, ..., N-1j вторая группа информацион5

0

5

нь: вчодовч 1-го коммутационного блока соединена с второй группой выходов (1+1)-то коммутационного блока, I i ,3,5,..„,N-1, примем К-й ком- мутационный блок содержит первый узел памяти, первый элемент ИЛИ и блок ввода-вывода„ причем первая группа информационных входов Кто коммутационного блока соединена с первым адресным входом первого узла памяти, первый информационный выход первого узла памяти соединен с первым синхровходом блока ввода-вывода, второй синхровход которого соединен с синхровходом К-го коммутационного блока, лервый вхор группы управляющих входов которого соединен с первы управляющим входом блока ввола-вывода, вход начальной установки которо- го соединен с одноименным входом К-го коммутационного блока, вход-выход которого соединен с входом-выходом блока ввода-вывода, выход кото рого соединен с вторым адресным вхо дом первого узла памяти К-го коммутационного блока, информационный вход блока ввода-вывода соединен с выходом первого элемента ИЛИ коммутационного блока, о т л и ч а- ю щ а я с я тем, что, с целью увеличения информационной емкости устройства за счет динамической леэест- ройки триггеров, в К-й коммутационны блок устройства введены второй узел памяти, первый и второй мультиплексоры, второй элемент ИЛИ, причем второй информационный выход первого узла памяти соединен с первым адресным входом второго узла памяти К-г с ком- мутационного блока, первый инйсоме ционный выход которого соединен г первой группой информационных выходов К-го коммутационного блока, в го

рой адресный вход второго узла памяти 45 рого соединен с управляющими входами

соединен с выходом блока ввода-вывода К-го коммутационного блока, второй управляющий вход которого соединен с выходом второго элемента ИЛИ, второй информационный выход второго узла памяти соединен с входом сброса блока ввода-вывода К-го коммутационного блока, третьи информационные выходы первого и второго узлов памяти соединены с информационными входами соответственно первого и второго мультиплексоров К-го коммутационного блока, управляющие входы которых соединены соответственно с вторым и

5 , 0

5

третьим входами группы управляющих входов К-го коммутационного блока, первые выходы первого и второго мультиплексоров соединены соответственно с первым и вторым входами первого элемента ИЛИ К-го коммутационного блока, третьи и четвертые входы которого соединены с первым и вторым входами второй группы информационных входов К-го коммутационного блока, вторые выходы первого и второго мультиплексоров соединены соответстве,н- но с первым и вторым входами второго элемента ИЛИ К-го коммутационного блока, третьи и четвертые входы которого соединены соответственно с Фетьим и четвертым входами второй группы информационных входов К-го коммутацией -ого блока, первый и второй выходы второй группы выходов которого соединены соответственно с третьим и четвертым выходами первого мультиплексора К-го коммутационного блока, третьи и четвертые выходы второго мультиплексора К-го коммутационного блока соединены соответственно с третьим к четвертым выходами второй группы выходов К-го коммутационного оло1 а.

2, Матрица поп, 1, о т л и ч а - ю щ а с я тем, что блок ввода- выЕодг, содержит мультиплексор, первый и второй :злы коммутации, элемент слгремя состояниями, элемент НЕ, с первого п шестой элементы ИЛИ причем первый и второй информационные входы нультиппексора соединены соответственно с шиной логической единицы и нуля, третьи и четвертые информационные входы мультиплексора соединены соответственно с первым и вторым синхровходами блока ввода-вывода, первый управляющий вход кото0

5

мультиплексора первого и второго узлов коммутации, выход второго узла коммутации является выходом блока ввода -вывода, вход-выход которого соединен с первым информационным входом второго узла коммутации и с входом-выходом элемента с тпемя состояниями, управляющий вход которого соединен с первым выходом мультиплексора, информационный вход элемента с тремя состояниями соединен с выходом первого узла коммутации, информационный вход блока ввода-вывода соединен с первыми входами перво™

го и второго элементов И, выходы которых соединены с входами первого элемента ИЛИ, выход которого соединен с первым входом третьего элемента И, первый вход четвертого элемента И соединен с информационным входом блока в.вода-вывода, с входом элемента НЕ, с первым информационным входом первого узла коммутации, второй информационный вход которого соединен с выходом элемента НЕ, вторые входы третьего и четвертого и первые входы пятого и шестого элементов И соединены с вторым выходом мультиплексора, выходы третьего и четвертого элементов И соединены с первыми входами второго и третьего элементов ИЛИ, выходы которых соединены соответственно с вторыми входами пятого и шестого элементов И, выходы которых соединены с первыми входами четвертого и пятого элементо ИЛИ, выходы которых соединены соответственно с третьими входами треть21

82353 0

его и четвертого элементов И, выход второго элемента ИЛИ соединен с вторым входом третьего элемента ИЛИ, выход которого соединен с вторым входом второго элемента ИЛИ, выход четвертого элемента ИЛИ соединен с третьим информационным входом первого узла коммутации, вторым информаЮ ционным входом второго узла коммутации и вторым входом пятого элемента ИЛИ, выход которого соединен с четвертым информационным входом первого узла коммутации и вторым вхоJ5 Дом четвертого элемента ИЛИ, третий вход которого является входом начальной установки блока ввода-вывода, вход сброса которого соединен с третьим входом пятого элемента ИЛИ,

20 третий информационный вход второго узла коммутации соединен с информационным входом блока ввода-вывода, второй управляющий вход которого соединен с вторыми входами первого

25 и второго элементов И.

Фт,2

CMV

f

Авторы

Даты

1990-07-30—Публикация

1988-10-14—Подача