Изобретение относится к вычислительной технике связи и может быть использовано при разработке и конструировании коммутационных систем. Цель изобретения - повышение быстродействия в режиме настройки ветвящихся связей за счет параллельной настройки матричного коммутатора.

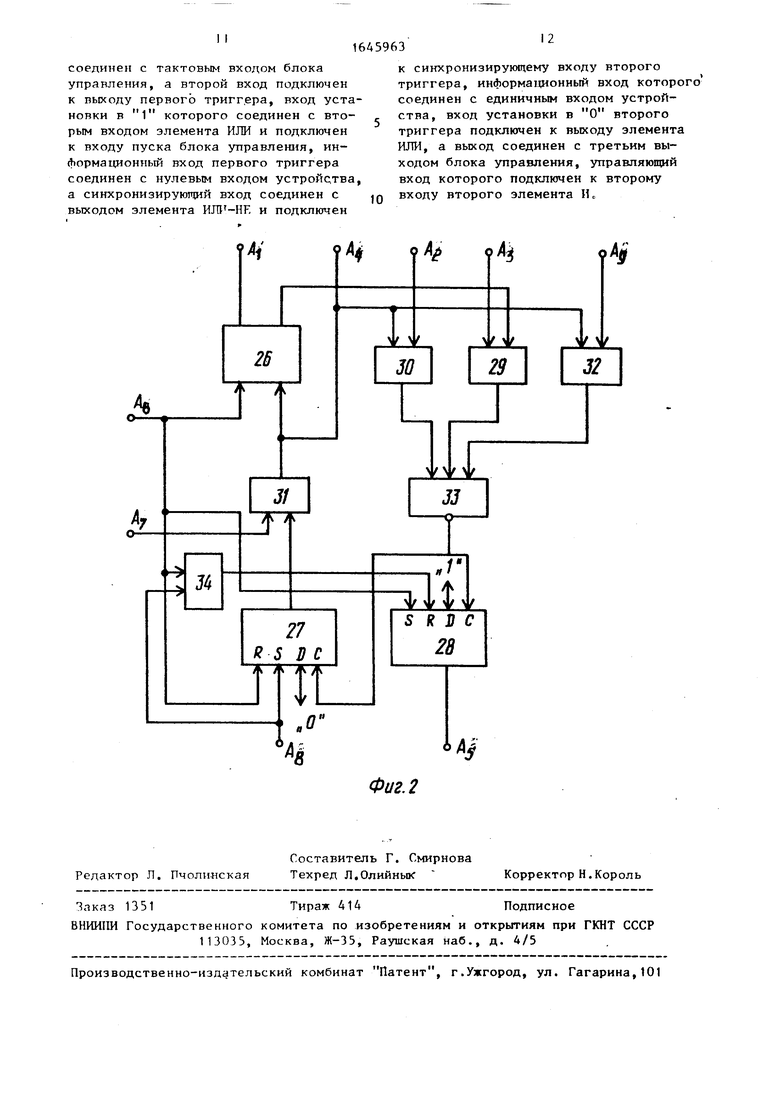

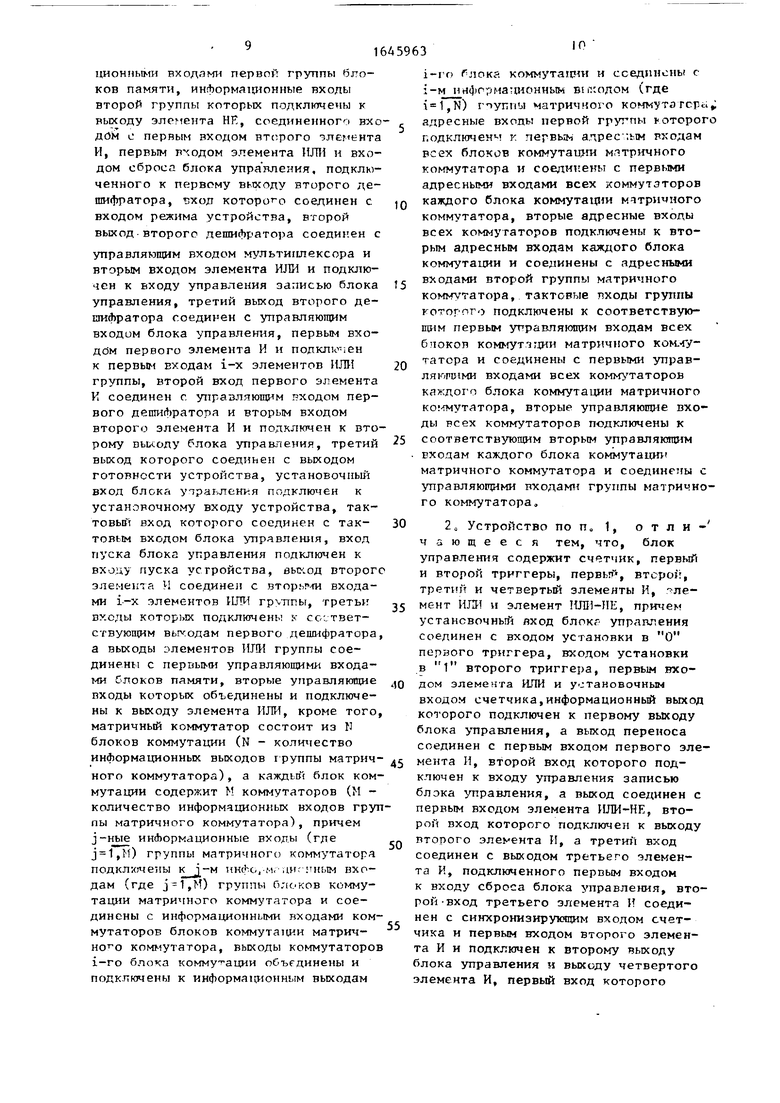

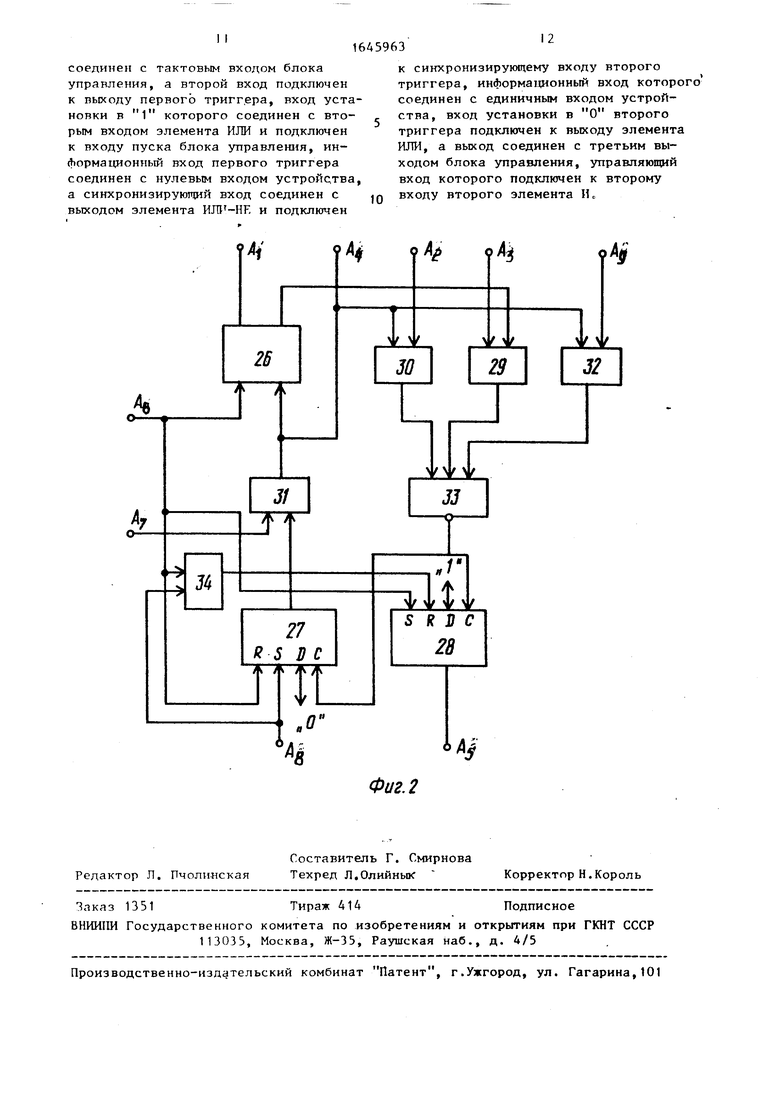

На фиг с 1 представлено коммутационное устройство; на фиг. 2 - блок управления.

Коммутационное устройство содержи матричный коммутатор 1, включающий в себя N«M коммутаторов 2, объединенных в N блоков 3 по М коммутаторов коммутации в каждом, группу дешифраторов 4, N блоков 5 памяти, группу элементов И 6, группу элементов ИЛИ 7, первый 8 и второй 9 элементы И, элемент ИЛИ 10, первый 11 и второй 12 дешифраторы, мультиплексор 13, элемент НЕ 14 и блок 15 управления „

Устройство имеет группу информационных входов 16, группу информационных выходов 17, адресный вход 18, вход 19 второго адреса, вход 20 первого адреса, тактовый вход 21, вход 22 пуска, выход 23 готовности, вход 24 режима и установочный вход 25.

Блок 15 управления содержит счетчик 26, первый 27 и второй 28 триггеры, первый 29, второй 30, третий 31 и четвертый И 32 элементы, элемент ИЛИ-НЕ 33 и элемент ИЛИ 34.

Предлагаемое коммутационное устройство работает в четырех режимах: Подготовка, Загрузка, Настройк и Обмен о

В режиме Подготовка приводятся в исходные состояния блоки 5 памяти В режиме Загрузка в блоке 5 памят загружается программа коммутациис В режиме Настройка программа комму

0

0

5

0

45

50

55

тации загружается в матричный коммутатор 1, что обеспечивает установление требуемых коммутационных связей„ По окончании режима Настройка устройство готово к работе в режиме Обмен, в котором осуществляется передача информации через матричный коммутатор 1 с входов 16 на выходы 17.

Коммутационное устройство работает следующим образом,, I

Импульсом начальной установки,

поступающим на вход 25, приводятся в исходные состояния триггеры 27 и 28 и счетчик 26„ Выбор режима работы коммутационного устройства осуществляется кодом, поступающим на вход 24 с. При работе в режиме Подготовка на первом выходе дешифратора 12 формируется логический сигнал высокого уровня, что обеспечивает работу блоков 5 памяти в режиме записи воздействием на управляющие входы второй группы через элемент ИЛИ 10 и управление записью информации в блоки 5 памяти посредством воздействия на управляющие входы первой группы стро- бирующих импульсов с выхода блока управления А 4 через элемент И 9 и элементы ИЛИ 7, кроме того, на информационные входы группы блоков 5 памяти поступает логический сигнал низкого уровня с выхода элемента НЕ 14, что обеспечивает идентификацию всей записываемой в блок 5 памяти информации как недействительной, т.е. фактически эмулируется процедура очистки памяти. Выбор подготавливаемой (очищаемой) области памяти осуществляется по адресу, который поступает на вход 18 устройства и фактически определяет номер фрагмента программы коммутации. После выполнения указанных процедур импульсом Пуск, поступающим на вход 22 коммутационного

5

устройства, осуществляется запуск режима Подготовка. При этом на выходе триггера 27 устанавливается логический сигнал высокого уровня, который открывает элемент И 31„ Тактовые импульсы, поступающие на вход 21 коммутационного устройства, через открытый элемент И 31 воздействуют на синхронизирующий вход счетчика 26, что обеспечивает формирование адреса, который поступает через мультиплексор 13 на адресные входы блока 5 памяти и на второй вход элемента И 9, что обеспечивает поступление импульсов управления записью через элементы ТШИ 7 на управляющие входы первой группы блоков 5 памяти. При появлении на выходе переноса счетчика 26 логического сигнала высокого уровня, который через открытый элемент И 29 и элемент ИЛИ-НЕ 32 поступает на синхронизирующий вход триггеров 27 и 28, формирование тактовых импульсов и соответствующих адресных кодов блоком 15 управления прекращается При этом на выходе триггера 27 устанавливается логический сигнал низкого уровня, который запрещает работу элемента И 31, а на выходе триггера 2S устанавливается логический сигнал высокого уровня, который поступает на выход 23 устройства и может быть идентифицирован внешним устройством как признак готовности коммутационного устройства к дальнейшей работе„ появление признака готовности на выходе 23 устройства при работе в режиме Подготовка определяет, что об- |Ласть памяти,соответствующая вибран- ноку фрагменту программы коммутации, очищена Работа предлагаемого коммутационного устройства в режиме подготовки к загрузке Фрагмента программы коммутации на этом завершается,,

При работе в режиме Загрузка на вход 24 устройства подается соответствующий код, что обеспечивает появление на втором выходе дешифратора 12 логического сигнала высокого уровня, который открывает элемент И 30, обеспечивает работу блоков 5 памяти в режиме записи и переключает направление мультиплексора 13„ На входе 18 устанавливается адрес области памяти, в которую загружается фрагмент программы коммутации, на входе 20 устанавливается адрес входа матричного коммутатора, а на входе 19 - адрес

, 645963

ы,хо;,л

г. яурпчног(-- коммуТгП опа ,

т ч

поел г

-чс-го ттульс Пуск с н: ода 2 --л- пускается блок I5 упракленш . h,: i этом на выводе триггера : у- ьпавли- вается логичегкт: скгнлл уровня, который открывает пгс-мелт И 31, Тактовый импульс с выхода элемента И 31 стробирует дешифратор 11 ь с соотJQ ветствую/дего выхода которого ттмлульс через соответствующий элемент ШП1 7 поступает на 1-й упг-авляклгнп вход группы первой группы соответ. г ующего 1-го блока 5 памяти. Гропе того, ука5 , занннй управляющий импульс яадли : фронтс.м нпкрементируст содкрлсш-юе счетчлка 26 и, прохода через зг -мппы И 30 н ИЛИ-HF, З 3 упмн.- вппвапт на -лт- ХОДР триггера 27 .гиг-и скиг cm ПРЛ

20 низкого уровня, кот рьи: Зс кр шалг1 элемент И 31, а на выходе триггера 2В - логический сигнал высокого уровня, который, поступая на выход 23 устройства, индицирует готовность

25 к загрузке адреса следующей о -п ч

коммутации с На входах 19 и 0 устной- ства устанавливается адрес связи н процедура затру.тки ъозоГчо - ляется w-тулъсом с 22 ус.трог0

5

0

ства. После завершения загрузки адресной информации о всех связях вь. - ранного фрагмента лрограммы коммутации на входе 18 устро; CTIV- ciTiaвливается номер следующего фрагмента программы коммутации, после чего процедуры подготовки и загрузки мо ут продолжаться

При работе устройства в режиме Настройки иа вход 24.устройства подается соответствующий код, что обеспечивает появление на третьем выходе дешифратора 12 логического сигнала высокого уровня, который открывает элементы И 8 и 32 и, прохо- дя через элементы ИЛИ 7, выбирает все блоки 5 паяти. При наличии логического сигнала высокого уровня на выходе 23 устройства процедура настройки коммутационного устройства начинается импульсом, поступившим на вход 22 устройства. При этом тактовые импульсы и коды адресов формируются в блоке 15 управления элементом И 31 и счетчиком 26 аналогично режиму Подготовка о С выхода А блока 15 управления адресные коды, представляющие собой адреса выходов блоков 3 коммутации, поступают на адресные входы второй группы матрич0

ного коммутатора 1 и далее через вторые адресные входы блоков 3 коммутации - на вторые адресные входы коммутаторов 2. Кроме того, указан- ные адресные коды через мультиплексор 13 поступают на адресные входы блоков 5 памяти, на адресные входы первой группы которых с входа 18 устройства подается адрес, соответст вующий настраиваемому фрагменту программы коммутации.

Блоки 5 памяти приведены в режим чтения логическим сигналом низкого уровня, сформированным элементом ИЛИ 10. По каждому из адресных кодов, сформированных блоком 15 управления, из блоков 5 памяти выбирается информация об адресе входа коммутатора и признак достоверности выбранной информации, причем на первых выходах блоков 5 памяти формируется признак достоверности выбранной информации, на вторых выходах блоков 5 памяти - адреса входов коммутаторов 2, выбранных соответствующими дешифраторами 4 по адресным кодам, сформированным на третьих выходах соответствующих блоков 5 памяти. При наличии логического сигнала высокого уровня на первых выходах (признака достоверности) блоков 5 памяти, определяющего достоверность выбранной информации, соответствующие подключенные к ним элементы.И 6 открываются и пропускают тактовый импульс, сформированный блоком 15 управления, который, поступая на первые управляющие входы коммутаторов 2, стробируе

0

5

0

5

устанавливает на выходе триггера 28 логический сигнал высокого уровня, который, поступая на выход 23, устанавливает готовность коммутационного устройства к обмену либо к выполнению дальнейших процедур подготовки, загрузки или настройки.

Формула изобретения

1. Коммутационное устройство, содержащее матричный коммутатор, группу дешифраторов, N блоков памяти, причем информационные входы группы и информационные входы матричного коммутатора соединены с информационными группами входов и выходов устройства соответственно, отличающееся тем, что, с целью повышения быстродействия в режиме настройки ветвящихся связей за счет параллельной настройки матричного коммутатора, в него введены группа элементов И, группа элементов ИЛИ, первый и второй элементы И, элемент ИЛИ, первый и второй дешифраторы, мультиплексор, элемент НЕ, блок ynj- равления, причем i-й вход (где , N - количество информационных входов группы, группы тактовых входов матричного коммутатора подключен к выходу 1-го элемента И (где ,N) группы, первые входы группы элементов И группы объединены и подключены к выходу первого элемента И, а вторые входы элементов И группы соединены с первыми выходами соответствующих блоков памяти, вторые выходы которых подключены к соответствую

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутационное устройство | 1990 |

|

SU1730635A1 |

| Коммутационное устройство | 1989 |

|

SU1672464A1 |

| Коммутационное устройство | 1989 |

|

SU1621041A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Коммутационное устройство | 1984 |

|

SU1246109A1 |

| Коммутационное устройство | 1988 |

|

SU1539790A1 |

| Модуль матричного коммутатора | 1990 |

|

SU1793436A2 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1144108A1 |

| ДИСКРЕТНАЯ МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1997 |

|

RU2110827C1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ МОНТАЖА, ПАРАМЕТРОВ ЭЛЕКТРИЧЕСКИХ ЦЕПЕЙ И ДИАГНОСТИКИ НЕИСПРАВНОСТЕЙ СЛОЖНЫХ УСТРОЙСТВ ЭЛЕКТРОАППАРАТУРЫ И ТОКОРАСПРЕДЕЛИТЕЛЬНЫХ СЕТЕЙ | 2008 |

|

RU2377585C1 |

Изобретение относится к вычислительной технике связи и может быть использовано при разработке и конструировании коммутационных систем. Пелью изобретения является повышение быстродействия в режиме настройки ветвягцихся связей за счет параллельной настройки матричного коммутатора , Устройство содержит матричный коммутатор 1, состоящий из К«М коммутаторов 2, объединенных в N блоков 3 коммутации по М коммутаторов

45

установление связи в узлах 2 коммута- 40 Р адресным входам первой группы ции« Если считываемая из какого-либо из блоков 5 памяти информация сопровождается значением признака, соответствующим недостоверности информации, связь в соответствующем блоке 3 коммутации не устанавливается. После этого задним фронтом указанный импульс инкрементирует счетчик 26 и процедура установления следующих связей осуществляется аналогично. При выполнении n-го такта настройки коммутатора на выходе переноса счетчика 26 формируется логический сигнал высокого уровня, который проходит через открытый элемент И 32 и элемент ИЛИ-НЕ 33 и своим задним фронтом устанавливает на выходе триггера 27 логический сигнал низкого уровня, который , закрывает элемент И 31 и, кроме того,

50

55

матричного коммутатора, управляющи входы группы которого соединены с выходами дешифраторов группы, вход которых подключены соответственно к третьим выходам блоков памяти, в ды адреса программы которых объеди нены и подключены к адресному вход устройства, адресные входы блоков памяти объединены и подключены к в ходу мультиплексора, первый информ ционный вход которого соединен с а ресными входами второй группы матр ного коммутатора и подключен к пер вому выходу блока управления, втор информадионный вход мультиплексор подключен к информационному входу первого дешифратора и входу второг адреса устройства, вход пе рвого.ад са устройства соединен с информа

Р адресным входам первой группы

матричного коммутатора, управляющие входы группы которого соединены с выходами дешифраторов группы, входы которых подключены соответственно к третьим выходам блоков памяти, входы адреса программы которых объединены и подключены к адресному входу устройства, адресные входы блоков памяти объединены и подключены к выходу мультиплексора, первый информационный вход которого соединен с адресными входами второй группы матричного коммутатора и подключен к первому выходу блока управления, второй информадионный вход мультиплексора подключен к информационному входу первого дешифратора и входу второго адреса устройства, вход пе рвого.адреса устройства соединен с информационными входами первой группы блоков памяти, информационные входы второй группы которых подключены к выходу элемента НЕ, соединенного входом с первым входом второго олемента И, первым входом элемента ИЛИ и входом сброса блока управления, подключенного к первому выходу второго дешифратора, Т5ХОД КОТОРОГО Соединен С

входом режима устройства, второй выход второго дешифратора соединен с

управляющим входом мультиплексора и вторым входом элемента ИЛИ и подключен к входу управления записью блока управления, третий выход второго де- ииАратора соединен с управляющим входом блока управления, первым входом первого элемента И и подключен к первым входам 1-х элементов ИЛИ группы, второй вход первого элемента И соединен г управляющим РХОДОМ первого дешифратора и вторым входом второго элемента И и подключен к второму вьиоду блока управления, третий выход которого соединен с выходом готовности устройства, установочный вход блока утраьления подключен к установочному входу устройства, тактовый вход которого соединен с так- товым входом блока управления, вход пуска блока управления подключен к вхоц пуска устройства, выход второго элемента Ч соединен с вторыми входами 1-х элементов ИЛИ группы, третьи входы которых подключены к со-твет- ствующим выводам первого дешифратора, а выходы элементов ИЛИ группы соединены с первыми управляющими входами Слоков памяти, вторые управляющие входы которых объединены и подключены к выходу элемента ИЛИ, кроме того, матричный коммутатор состоит из N блоков коммутации (N - количество информационных выходов группы матрич- ного коммутатора), а каждый блок коммутации содержит М коммутаторов (М - количество информационных входов группы матричного коммутатора), причем j-ные информационные входы (где ,M) группы матричного коммутатора подключены ишН,, м, дн гным входам (где ,M) группы блоков коммутации матричного коммутатора и соединены с информационными входами коммутаторов блоков коммутации матрич- коммутатора, выходы коммутаторов 1-го блока коммутации объединены и подкпючены к информатсионным выходам

i-iо Fлокй коммутации и соединены г i-м информационным В с:одом (где ) глупиы матриччого кочмутз тер адресные входы первой гругпы юторо подключен г первым ачрес ;ым входам всех блоков коммутации матричного коммутатора и соединены с первыми адресными входами всех коммутаторов каждого блока коммутации м-чтрнчного коммутатора, вторые адресные входы всех коммутаторов подключены к вторым адресным входам каждого блока коммутации и соединены с адресными входами второй группы матричного коммутатора, тактовые лходы группы которого подключены к соответствующим первым управляющим входам всех бчоков коммутации матричного коммутатора и соединены с первыми управляющими входами всех коммутаторов каждого блока коммутации матричного коммутатора, вторые управляющие входы всех коммутаторов подключены к соответствующим вторым управляющим входам каждого блока коммутации матричного коммутатора и соединетш с управляющими входами группы матри«н го коммутатора,

2а Устройство по п„ 1, о т л и чающееся тем, что, блок управления содержит счетчик, первый и второй триггеры, первьп, второй, третий и четвертый элементы И, ле- мент ИЛР и элемент 1ШИ-НЕ, причем установочный яход блокг управления соединен с входом установки в О первого триггера, входом установки в 1 второго триггера, первым входом элемента ИЛИ и установочным входом счетчика,информационный выход которого подключен к первому выходу блока управления, а выход переноса соединен с первым входом первого элемента И, второй вход которого подключен к входу управления записью блока управления, а выход соединен с первым входом элемента ИЛИ-НЕ, второй вход которого подключен к выходу второго элемента И, а третий вход соединен с выходом третьего элемента И, подключенного первым входом к входу сброса блока управления, второй -вход третьего элемента И соединен с синхронизирующим входом счетчика и первым входом второго элемента И и подключен к второму выходу блока управления и выходу четвертого элемента И, первый вход которого

16

соединен с тактовым входом блока управления, а второй вход подключен к выходу первого триггера, вход установки в 1 которого соединен с вто- рым входом элемента ИЛИ и подключен к входу пуска блока управления, информационный вход первого триггера соединен с нулевым входом устройства, а синхронизирующий вход соединен с выходом элемента ИЛИ-НЕ и подключен

12

к синхронизирующему входу второго триггера, информационный вход которого соединен с единичным входом устройства, вход установки в О второго триггера подключен к выходу элемента ИЛИ, а выход соединен с третьим выходом блока управления, управляющий вход которого подключен к второму входу второго элемента И„

| Коммутационное устройство | 1984 |

|

SU1246109A1 |

| Г, 06 F 15/16, 1986 | |||

| Коммутационное устройство | 1986 |

|

SU1387006A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-04-30—Публикация

1989-04-06—Подача