Изобретение относится к вычислительной технике и может быть использовано для коммутации ресурсов в отказоустойчивых вычислительных системах.

Целью изобретения является сокращение времени корректировки программ коммутации при отказах коммутируемых ресурсов с

На фиг01 представлено коммутационное устройство; на фиг„2 - блок управления; на фиг.З - блок преобразования адреса; на фиг о 4 - блок настройки; на фиг с 5 - фрагмент графа связей

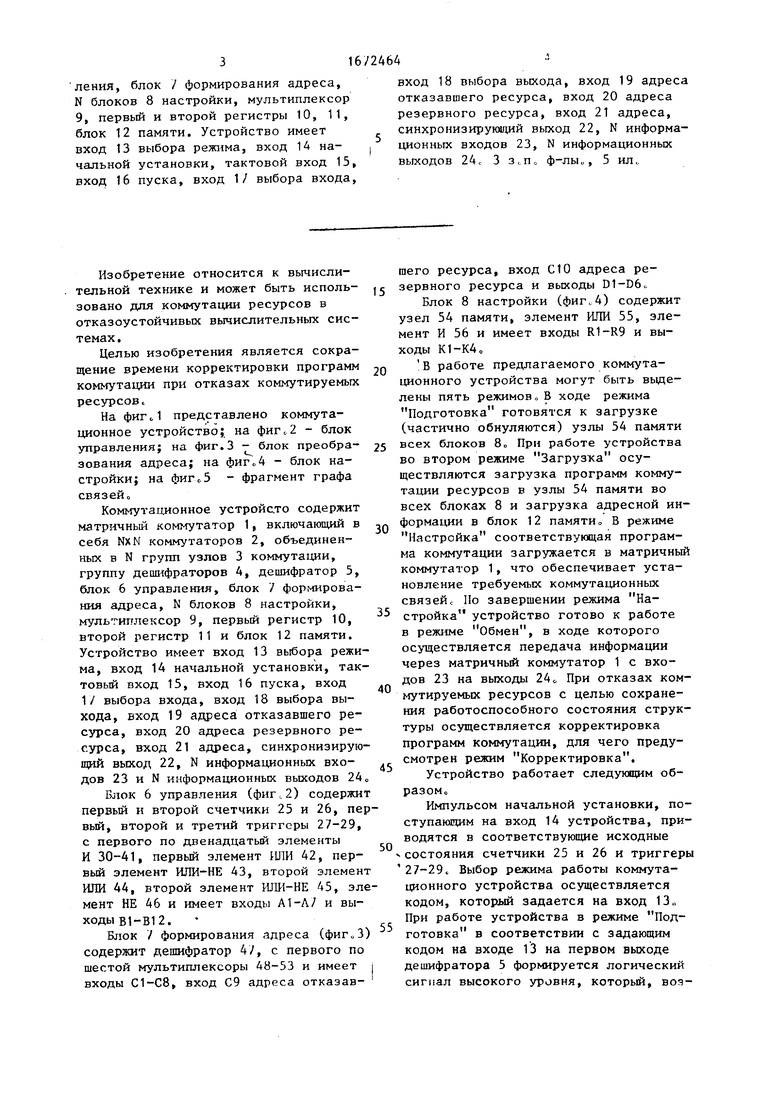

Коммутационное устройсго содержит матричный коммутатор 1, включающий в себя NXN коммутаторов 2, объединенных в N групп узлов 3 коммутации, группу дешифраторов 4, дешифратор 5, блок 6 управления, блок 7 формирования адреса, N блоков 8 настройки, мультиплексор 9, первый регистр 10, второй регистр 11 и блок 12 памяти. Устройство имеет вход 13 выбора режима, вход 14 начальной установки, тактовый вход 15, вход 16 пуска, вход 1/ выбора входа, вход 18 выбора выхода, вход 19 адреса отказавшего ресурса, вход 20 адреса резервного ресурса, вход 21 адреса, синхронизирующий выход 22, N информационных входов 23 и N информационных выходов 24„

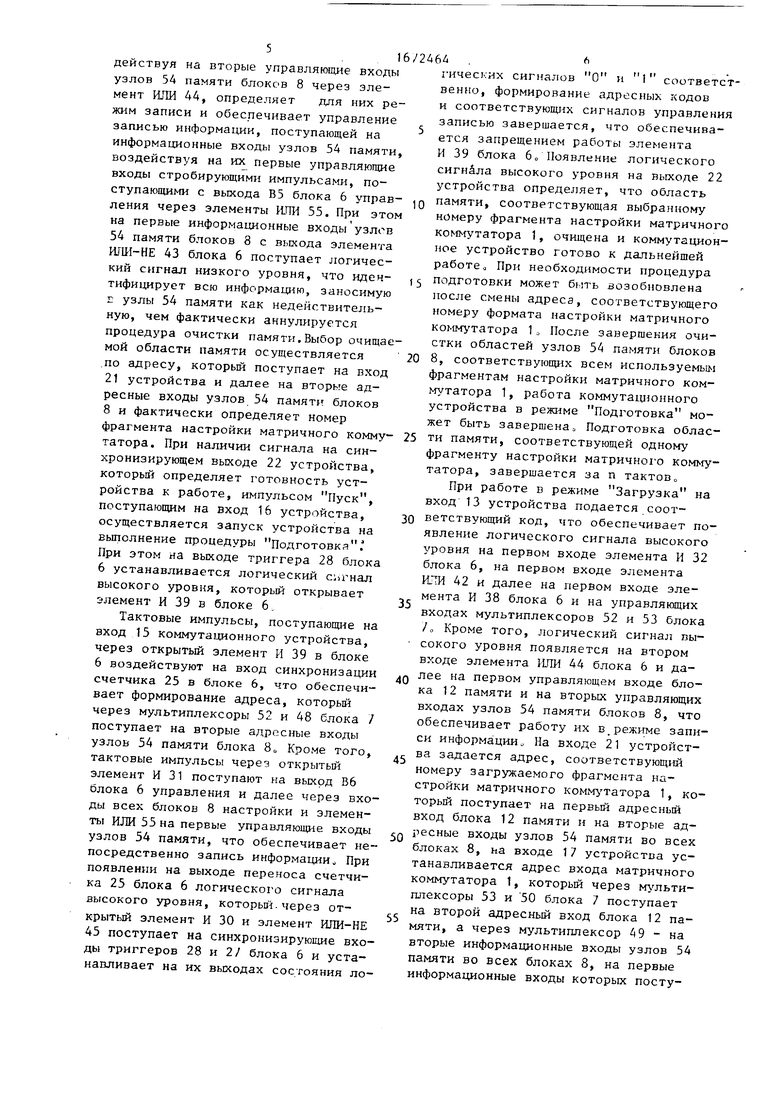

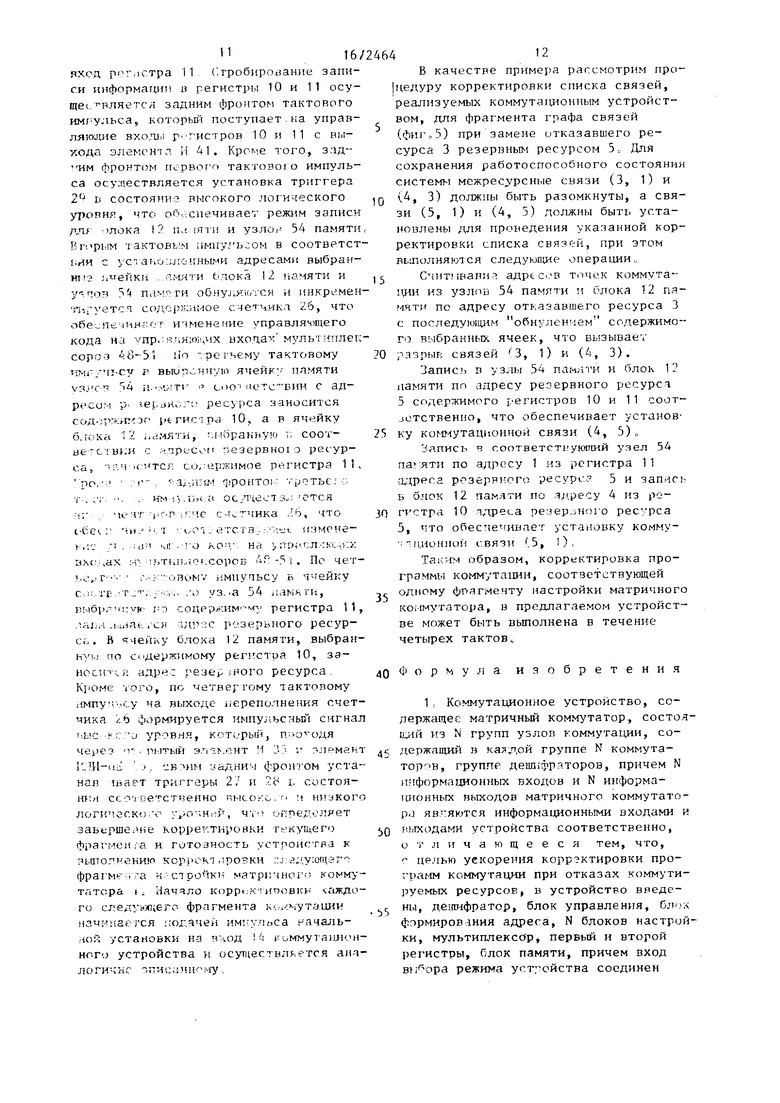

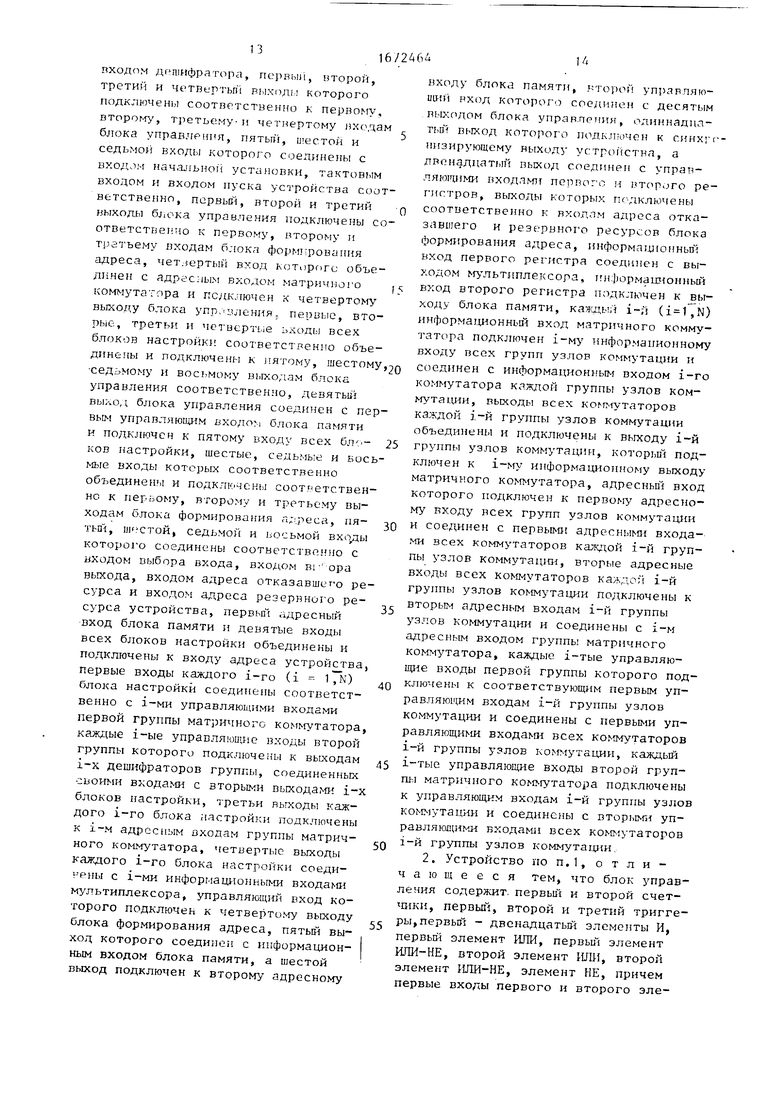

Блок 6 управления () содержит первый и второй счетчики 25 и 26, первый, второй и третий триггеры 27-29, с первого по двенадцатый элементы И 30-41, первый элемент ИЛИ 42, первый элемент ИЛИ-НЕ 43, второй элемент ИЛИ 44, второй элемент ИЛИ-НЕ 45, элемент НЕ 46 и имеет входы А1-А/ и выходы В1-В12.

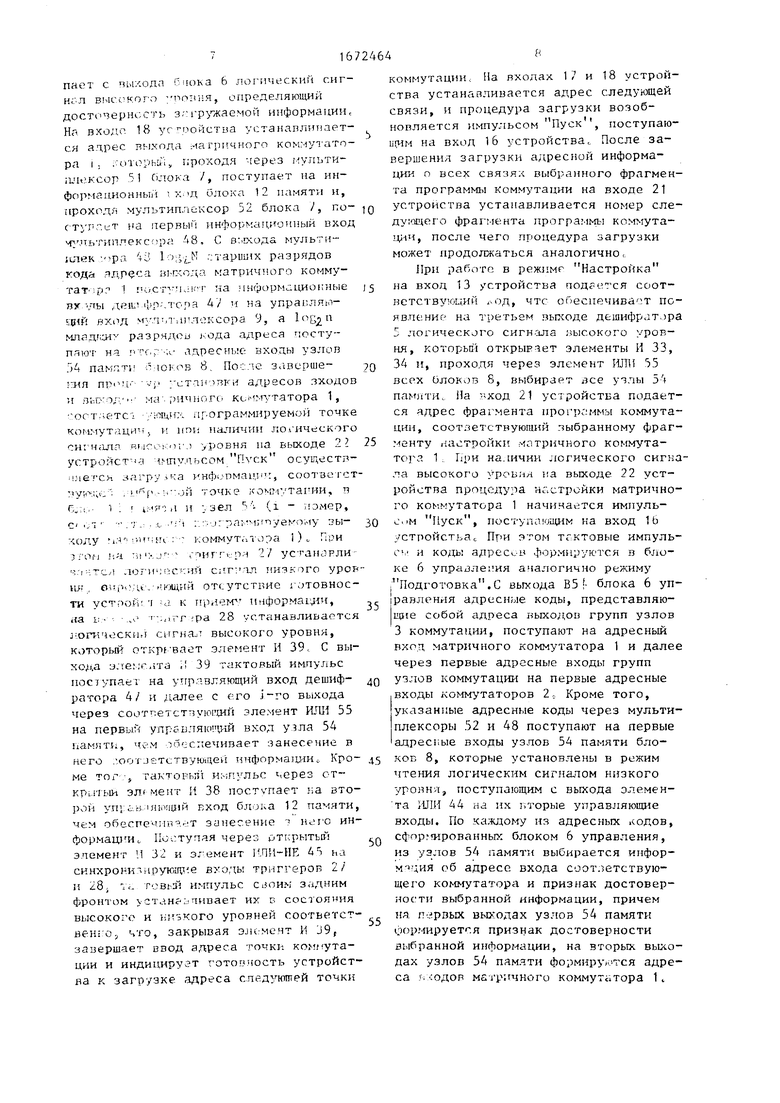

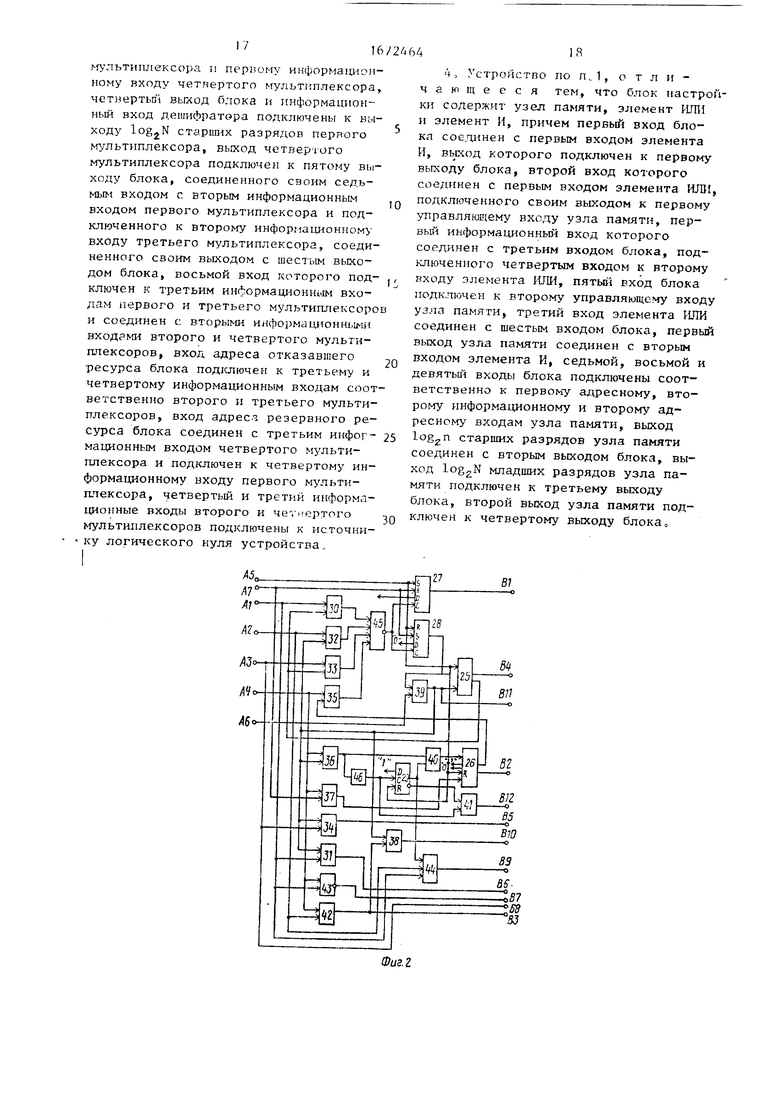

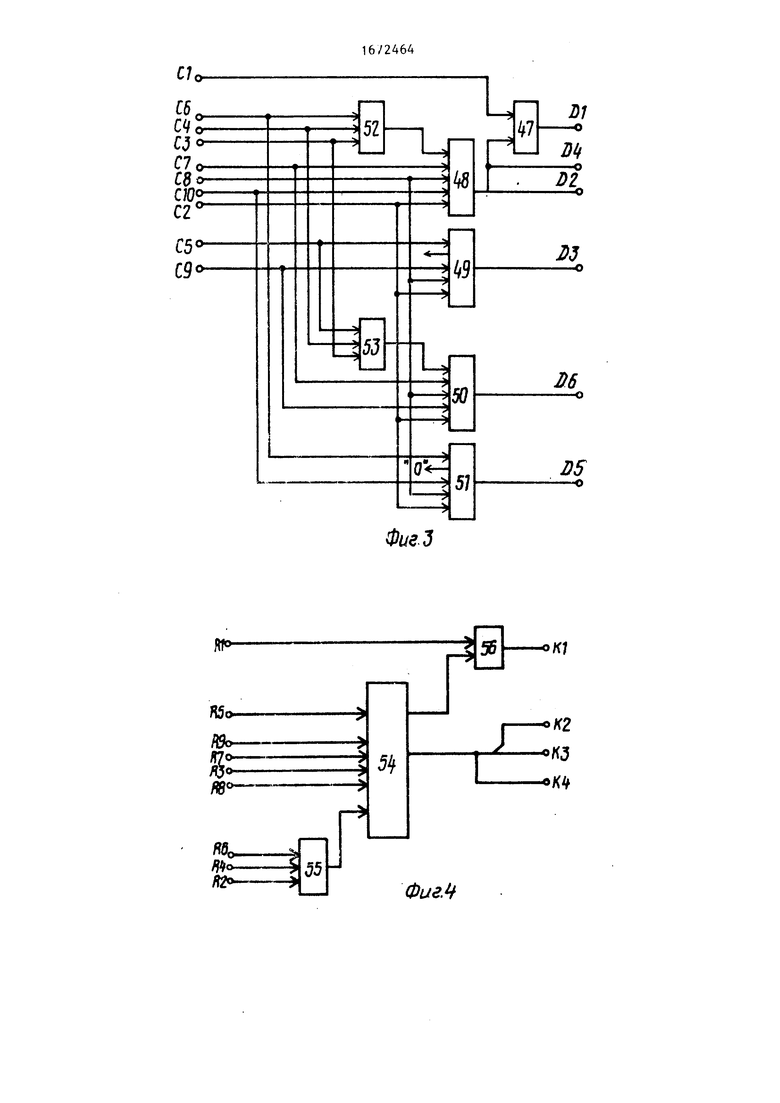

Блок 7 формирования адреса (фиг„3) содержит дешифратор 47, с первого по шестой мультиплексоры 48-53 и имеет входы С1-С8, вход С9 адреса отказав-

5

0

5

0

5

0

5

0

5

шего ресурса, вход С10 адреса резервного ресурса и выходы D1-D6o

Блок 8 настройки () содержит узел 54 памяти, элемент ИЛИ 55, элемент И 56 и имеет входы R1-R9 и выходы К1-К40

В работе предлагаемого коммутационного устройства могут быть выделены пять режимов В ходе режима Подготовка готовятся к загрузке (частично обнуляются) узлы 54 памяти всех блоков 8о При работе устройства во втором режиме Загрузка осуществляются загрузка программ коммутации ресурсов в узлы 54 памяти во всех блоках 8 и загрузка адресной информации в блок 12 памяти „ В режиме Настройка соответствующая программа коммутации загружается в матричный коммутатор 1, что обеспечивает установление требуемых коммутационных связей с Но завершении режима Настройка устройство готово к работе в режиме Обмен, в ходе которого осуществляется передача информации через матричный коммутатор 1 с входов 23 на выходы 24„ При отказах коммутируемых ресурсов с целью сохранения работоспособного состояния структуры осуществляется корректировка программ коммутации, для чего предусмотрен режим Корректировка.

Устройство работает следующим об- разомо

Импульсом начальной установки, поступающим на вход 14 устройства, приводятся в соответствующие исходные - состояния счетчики 25 и 26 и триггеры 27-29, Выбор режима работы коммутационного устройства осуществляется кодом, который задается на вход 13„ При работе устройства в режиме Подготовка в соответствии с задающим кодом на входе 13 на первом выходе дешифратора 5 формируется логический сигнал высокого уровня, который, воздействуя на вторые управляющие входы узлов 54 памяти блоков 8 через элемент ИЛИ 44, определяет для них режим записи и обеспечивает управление записью информации, поступающей на информационные входы узлов 54 памяти, воздействуя на их первые управляющие входы стробирующими импульсами, поступающими с выхода В5 блока 6 управления через элементы ИЛИ 55. При этом на первые информационные входы узлов 54 памяти блоков 3 с выхода элемента ИЛИ-НЕ 43 блока 6 поступает логический сигнал низкого уровня, что идентифицирует всю информацию, заносимую Е узлы 54 памяти как недействительную, чем фактически аннулируется процедура очистки памяти.Выбор очищаемой области памяти осуществляется по адресу, которьй поступает на вход 21 устройства и далее на вторне адресные входы узлов 54 памяти блоков 8 и фактически определяет номер

10

/24646

гичесьих сигналов О и 1 соответственно, формирование адресных кодов и соответствующих сигналов управления записью завершается, что обеспечивается запрещением работы элемента И 39 блока 6 о Появление логического сигнала высокого уровня на выходе 22 устройства определяет, что область памяти, соответствующая выбранному номеру фрагмента настройки матричного коммутатора 1, очищена и коммутационное устройство готово к дальнейшей работе о При необходимости процедура ( подготовки может бить возобновлена после смены адреса, соответствующего номеру формата настройки матричного коммутатора 1„ После завершения очистки областей узлов 54 памяти блоков , соответствующих всем используемым фрагментам настройки матричного коммутатора 1, работа коммутационного устройства в режиме Подготовка может быть завершена о Подготовка облас20 8,

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутационное устройство | 1990 |

|

SU1730635A1 |

| Коммутационное устройство | 1989 |

|

SU1645963A1 |

| Коммутационное устройство | 1989 |

|

SU1621041A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Коммутационное устройство | 1988 |

|

SU1539790A1 |

| Модуль матричного коммутатора | 1990 |

|

SU1793436A2 |

| Устройство для централизованного управления вычислительной системой | 1985 |

|

SU1259261A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1144108A1 |

| Устройство ввода-вывода матричной вычислительной системы | 1987 |

|

SU1529234A1 |

| ДИСКРЕТНАЯ МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1997 |

|

RU2110827C1 |

Изобретение относится к вычислительной технике и может быть использовано для коммутации ресурсов в отказоустойчивых вычислительных системах. Целью изобретения является сокращение времени корректировки программ коммутации при отказах коммутируемых ресурсов. Коммутационное устройство содержит матричный коммутатор 1, включающий в себя N.N коммутаторов 2, объединенных в N групп узлов 3 коммутации, группу дешифраторов 4, дешифратор 5, блок 6 управления, блок 7 формирования адреса, N блоков 8 настройки, мультиплексор 9, первый и второй регистры 10, 11, блок 12 памяти. Устройство имеет вход 13 выбора режима, вход 14 начальной установки, тактовой вход 15, вход 16, пуска, вход 17 выбора входа, вход 18 выбора выхода, вход 19 адреса отказавшего ресурса, вход 20 адреса резервного ресурса, вход 21 адреса, синхронизирующий выход 22, N информационных входов 23, N информационных выходов 24. 3 з.п. ф-лы., 5 ил.

фрагмента настройки матричного комму- 25 ти памяти, соответствующей одному

татора. При наличии сигнала на синхронизирующем выходе 22 устройства, который определяет готовность устройства к работе, импульсом Пуск, поступающим на вход 16 устройства, осуществляется запуск устройства на выполнение процедуры Подготовка.1 При этом на выходе триггера 28 блока 6 устанавливается логический сигнал высокого уровня, который открывает элемент И 39 в блоке 6

Тактовые импульсы, поступающие на вход 15 коммутационного устройства, через открытый элемент И 39 в блоке 6 воздействуют на вход синхронизации счетчика 25 в блоке 6, что обеспечивает формирование адреса, который через мультиплексоры 52 и 48 блока / поступает на вторые адросные входы узлов 54 памяти блока 8„ Кроме того, тактовые импульсы через открытый элемент И 31 поступают на выход В6 блока 6 управления и далее через входы всех блоков 8 настройки и элементы ИЛИ 55 на первые управляющие входы узлов 54 памяти, что обеспечивает непосредственно запись информациио При появлении на выходе переноса счетчика 25 блока 6 логического сигнала высокого уровня, который через открытый элемент И 30 и элемент ИЛИ-НЕ 45 поступает на синхронизирующие входы триггеров 28 и 2/ блока 6 и устанавливает на их выходах сое гояния ло0

5

фрагменту настройки матричного коммутатора, завершается за п тактов,,

При работе в режиме Загрузка на вход 13 устройства подается соответствующий код, что обеспечивает появление логического сигнала высокого уровня на первом входе элемента И 32 блока 6, на первом входе элемента И7И 42 и далее на первом входе элемента И 38 блока 6 и на управляющих входах мультиплексоров 52 и 53 блока /о Кроме того, логический сигнал высокого уровня появляется на втором входе элемента ИЛИ 44 блока 6 и далее на первом управляющем входе блока 12 памяти и на вторых управляющих входах узлов 54 памяти блоков 8, что обеспечивает работу их в.режиме записи информации. На входе 21 устройст- ва задается адрес, соответствующий номеру загружаемого фрагмента настройки матричного коммутатора 1, который поступает на первый адресный вход блока 12 памяти и на вторые адресные входы узлов 54 памяти во всех блоках 8, на входе 17 устройства устанавливается адрес входа матричного коммутатора 1, которьй через мультиплексоры 53 и 50 блока 7 поступает на второй адресный вход блока 12 па0

0

5

мяти, а через мультиплексор 49 - на вторые информационные входы узлов 54 памяти во всех блоках 8, на первые информационные входы которых поступока Ь ло ическин гиго пр е д е л я юши и

пае т с nHi-сода

Не Т BHLi KOrO ПРПьЧ,

достояерн гп, з рожаемой информации, Н входе1 18 vc тройства з- -танаплияает- ся адрес рчхода -(агрнчногп ком iyn ато- ра i oioi bui г.роходя (ерез ГУПЪТИ- q 1 Олоьа /, поступает на информационный х д блока 12 памяти и, црохгдл мультиплексор 52 блока /, по- ст}Г т на первым информационный вход мучь типпекс -р. , С в-кода JL.-IPK ф i -J 1 ;,М т арших разрядов года чдрееа ыс одч матричного комму- тат pn I r -icr i i r на информационные ВУ ,i,Piu il 4/ и на упрагляю- НИИ ЯУОД м/д л штмчсора J, a младг,г разрядов ода адреса чпсту- пткн HI л адресные входы узлов

loi ов 8 По е завершеi i in ;ки адресов зходов

и ,чпьог( Ki птатора 1, .чц1г. лгограммируемои г тн наличии „riOt ического 11 ,ровня па выходе 22

10

15

70

22 25

С 1

соду } он а

1Ы О

ти ус114 аа i

14 naMiTi

ИЯ ПГ 1Т1

и -иг 5; ос т етс

КОГГ ТпЦИ1 J Ш PI К

устройст а IMIIVII псом ПУСК осущестя- 1 ie CH загр,- т а инсЪ. , COOTBOICT- Tiyso si, ;,i -,очке сочп тагии, я

Г„I i 4 «Я1, И . €Л С - 1 - DiMGp,

. 1 г a; Mi nyer vi,-i зы- 30 г .1 }ч i оммут,11 ооа ).. Г., И

г ч .-iHT in 11 усган рли с .in с,т 1л кия- тго урор- -. s иклдий от утстнис i JTOBHOC- 1О1, i к гтрлем1 информл уин, ,

, т i т pa 28 останавливается j огкческн-i cirrus высокого уровня, к)торый oTKpf влет элемент И С выхода ле:,г,ггс , 39 тактояый импульс иоступяе на VIP згяющий вход дешиф- дд ратора 4/ и далее с с го J-ro через соот ет сттчгю щй элемент ИЛИ 55 на перв-ьЛ улггягтякнчий вход узла 54 uaMSiTJ., ;KJM in с:;ечивает занесение в него оо i информа)щиь Кро- д ме тог s гакто1ь;и и .гульс 11ерез ст- крч1ыи эл меиг II 38 поступает ьа зто- рои yni е. в вход GjtJixa 12 памяти, чем обеспеа, занесение HOIO ин формации,, Поступая мере.; ртг рытьй , эпеменг Ч 3 и элемент ГПИ-НЕ 4е) на синхроьктарукягр е ВУО ТЫ тр.щ ероп 2/ и .8, -. с. импульс саоим задним фронтом ciaH тивает их Б состояния

коммутации На входах. 17 и 18 устр ства устанавливается адрес следующ связи, и процедура загрузки возобновляется импульсом Пуск, поступ щим на вход 16 устройства, После з вершения загрузки адресной информа ции о всех свячях выбранного фрагм та программы коммутации на входе 2 устроисгва устанавливается номер с ду:ощего фрагмента программы коммут ции, после чего процедура загрузки может продолжаться аналогично,

При работе в режиме Настройка на вход 13 устройства соо ветствующий ОД, ЧТС О ССПРЧИВа Т явпенир на третьем выходе дешифрлт логического сигнала ;,ысокого vpo ня, которьп открывает элементы И 3 34 и, проходя через элемент ИЛИ 55 всех олокоч 8, выбирает дсе заы 5 памичя На -«ход 21 устройства пода ся адрес фра мента программы комму ции, соответствующий тыбранному фр менту настройки матричного коммута тор 1 М и на щчии .готического си ла высокого на выходе 22 ус ройства процедура матрич го коммутатора 1 начинается импуль .м Пуск, поступающим на вход 1Ь устройстьас При згом тгктовые импу с1 и коды адресов формируются в бл ке 6 упрсылегия аналогично режиму Подготовка.С выхода В5 блока 6 равления адресные коды, представля щие собой адреса выходов групп узл 3 коммутации, поступают на адресны вход матричного коммутатора 1 и да через первые адресные входы групп узлов коммутации на первые адресны входы коммутаторов 2 Кроме того, указанные адресные коды через муль плексоры 52 и 48 поступают на перв адрес ые входы узлов 54 памяти бло ков 8, которые установлены в режим чтения логическим сигналом низкого уронна, поступающим с выхода элеме та ИЛИ 44 аа их ьторые управляющие входы. По каждому из адресных кодо сформированных блоком 6 управления из узлов 54 памяти выбирается инфо мчдия об адресе входа соответствую щего коммутаторе и признак достове ности выбранной информации, причем

высокого и уровней соответст- ня гфвых выходах узлов 54 памяти

веше, что, закрывая И 39, завершав ввод адреса го«ки коммутации и индиииру т т ото чость устройства к заго/зке адреса спедуюшрй точки

нормируется признак достоверности выбранной информации, на вторых вы дах узлов 54 памяти формируется ад са -одов матричного коммутатора К

0

5

0

5

0

,

дд д ,

коммутации На входах. 17 и 18 устройства устанавливается адрес следующей связи, и процедура загрузки возобновляется импульсом Пуск, поступающим на вход 16 устройства, После завершения загрузки адресной информации о всех свячях выбранного фрагмента программы коммутации на входе 21 устроисгва устанавливается номер сле- ду:ощего фрагмента программы коммутации, после чего процедура загрузки может продолжаться аналогично,

При работе в режиме Настройка на вход 13 устройства соответствующий ОД, ЧТС О ССПРЧИВа Т ПО- явпенир на третьем выходе дешифрлт ра логического сигнала ;,ысокого vpoB- ня, которьп открывает элементы И 33, 34 и, проходя через элемент ИЛИ 55 всех олокоч 8, выбирает дсе заы 54 памичя На -«ход 21 устройства подается адрес фра мента программы коммутации, соответствующий тыбранному фрагменту настройки матричного коммутатор 1 М и на щчии .готического сигнала высокого на выходе 22 уст- ройства процедура матричного коммутатора 1 начинается импуль- .м Пуск, поступающим на вход 1Ь устройстьас При згом тгктовые импуль- с1 и коды адресов формируются в блоке 6 упрсылегия аналогично режиму Подготовка.С выхода В5 блока 6 управления адресные коды, представляющие собой адреса выходов групп узлов 3 коммутации, поступают на адресный вход матричного коммутатора 1 и далее через первые адресные входы групп узлов коммутации на первые адресные входы коммутаторов 2 Кроме того, указанные адресные коды через мультиплексоры 52 и 48 поступают на первые адрес ые входы узлов 54 памяти блоков 8, которые установлены в режим чтения логическим сигналом низкого уронна, поступающим с выхода элемента ИЛИ 44 аа их ьторые управляющие входы. По каждому из адресных кодов, сформированных блоком 6 управления, из узлов 54 памяти выбирается инфор- мчдия об адресе входа соответствующего коммутаторе и признак достоверности выбранной информации, причем

нормируется признак достоверности выбранной информации, на вторых выходах узлов 54 памяти формируется адреса -одов матричного коммутатора К

При наличии логического сигнала высокого уровня на первых выходах узлов 54 памяти, определяющего достоьерность выбранной информации, соответст- ,- ветственно отказавшего

вующие подключенные к ним элементы И 56 открываются и пропускают тактовый импульс, поступающий с выхода элемента И 34, открытого логическим сигналом высокого уровня, поступающим с третьего выхода дешифратора 5, Тактовый импульс с выходов элементов И 56 поступает на первые управляющие входы коммутаторов 2 и стробирует установление в соответствующих коммутаторах коммутации, ЕСЛИ считываемая из узлов 54 памяти информация сопровождается значением признака, соответствующим недостоверности информации, установления связи ь соответствующей группе узлов 3 коммутации не происходит. Тактовый импульс задним фронтом осуществляет инкремен- тирование счетчика 25, после чего процедура установления следующих коммутационных связей осуществляется аналогично. При выполнении n-го такта настройки матричного коммутатора 1 на выходе переноса счетчика 25 формируется логический сигнал высокого уровня, который, проходя через открытый элемент И 33 и через элемент ИЛИ-НЕ 45, задним фронтом устс 1авли- вает на выходе триггера 28 логический сигнал низкого уровня, который закрывает элемент И 39, и кроме того, устанавливает на выходе триггера 21 логический сигнал высокого уровня, который, поступая на выход 22 устройства, устанавливает готовность коммутационного устройства к выполнению последующих процедур подготовки, загрузки или обмена информацией через матричный коммутатор 1 .,

При работе в режиме Корректировка на вход 13 устройства подается соответствующий код, что обеспечивает появление ка четвертом выходе де- илфратора 5 логического сигнала высокого уровня, который открывает элементы И 35, 36 и 3/ и, поступая на вторые входы элементен ИЛИ 42 и ИЛИ-НЕ 43, устанавливает на их выходах логические сигналы соответственно высокого и низкого уровней. На входе 21 устройства задается номер фрагмента настройки матричного коммутатора, подлежащий корректировке, который поН ступает на первый адресный вход бло10

20

25

30

35

40

45

50

55

ресурсов,, Кроме того, равляющие входы узлов первый управляющий вход мяти с выхода элемента логический сигнал низк обеспечивающий режим чт мяти. При наличии приз ти на выходе 22 устрой режима Корректировка подачей на вхол 16 сигн который через открытый поступает на вход синхр чика 26, что обеспечива па его информационных ляющего кода, зашитого ствующих информационных этом с выходов мультипл соответствующие входы б стройки подается адрес ного коммутатора 1, соо номеру отказавшего ресу ляющий вход мультиплекс дов мультиплексора 48 п группы коммутаторов 2, щей выбранному выходу м мутатора 1, а на первый блока 12 памяти с выход ра 50 подается адрес вх коммутатора 1, соответс отказавшего ресурса. На ные входы узлов памяти {ы логические сигналы н с выходов мультиплексор Кроме того, импульсом ляется установка тригге соответственно в состоя высокого логических уро этом тактовый импульс ч элемент И 39, управляющ шифратора 4/ и соответс мент ИЛИ 55 поступает н равляющий вход соответс 54 памяти и осуществляе адреса входа матричного 1, соответствующего отк сурсу, который через му поступает на информацио гистра 10. Кроме того, товый импульс через отк И 38 поступает на второ вход блока 12 памяти и считывание соответствую выхода матричного комму торый поступает на инфо

ка 12 памяти и на «торне адресные входы узлов 54 памяти На входы 19 и 20 устройства подается адреса соот- ветственно отказавшего

и

0

0

5

0

5

0

5

0

5

резервного

ресурсов,, Кроме того, на вторые управляющие входы узлов 54 памяти и нл первый управляющий вход блока 12 памяти с выхода элемента ИЛИ поступает логический сигнал низкого уровня, обеспечивающий режим чтения узлам памяти. При наличии признака готовности на выходе 22 устройства реализации режима Корректировка начинается подачей на вхол 16 сигнала Пуск, который через открытый элемент ИЗ/ поступает на вход синхронизации счетчика 26, что обеспечивает установку па его информационных выходах управляющего кода, зашитого на соответствующих информационных входах. При этом с выходов мультиплексора 48 на соответствующие входы блоков 8 настройки подается адрес выхода матричного коммутатора 1, соответствующий номеру отказавшего ресурса, на управляющий вход мультиплексора 9 с выходов мультиплексора 48 подается адрес группы коммутаторов 2, соответствующей выбранному выходу матричного коммутатора 1, а на первый адресный вход блока 12 памяти с выхода мультиплексора 50 подается адрес входа матричного коммутатора 1, соответствующий номеру отказавшего ресурса. На информационные входы узлов памяти при этом пода- {ы логические сигналы низкого уровня с выходов мультиплексоров 49 и 51. Кроме того, импульсом осуществляется установка триггеров 27 и 28 соответственно в состояния низкого и высокого логических уровней, При этом тактовый импульс через открытый элемент И 39, управляющий вход дешифратора 4/ и соответствующий элемент ИЛИ 55 поступает на первый управляющий вход соответствующего узла 54 памяти и осуществляет считывание адреса входа матричного коммутатора 1, соответствующего отказачшему ресурсу, который через мультиплексор 9 поступает на информационный вход регистра 10. Кроме того, указанный тактовый импульс через открытый элемент И 38 поступает на второй управляющий вход блока 12 памяти и осуществляет считывание соответствующего адреса выхода матричного коммутатора 1, который поступает на информационный

1116/

Ггробирование эапиРХОЦ ро- 11 си информации в регистры 10 и 11 осу- щв( гвляетсл задним фронтом тактового ишулъса, который поступает на управ- лягодие вхочь р петров 10 и 11 с выхода элемент;1 Л 41. Креме того, з 1Д- им фронтом первого импульса осуществляется установка триггера 2° ь состояни высокого логического уровне, тс об спечивает режим записи лл лока i па win и узлог 54 памяти, T r- рым тактовом ампугь-ом в СООТВРТСТ- ьии с j с. .личными адресами выбранит,1 ячейки лмяти блока 12 чамятн и 4 nav-ги обнулял,сн и инкремен

изменение тправляччцего ччялчих вхоца мульч члеобе nt чв кода на vnp соре з 8-51 Но - DC i ьему тактовому ттмг/41-су г выип, янмо ячеик памяти ч-ч. тч r 4 ii -.i- Ti з соо1 с ад- ресоч р ei jHv. i1 ре.}рса заносится сиД г ит :кл I trnc pci 10 а в ячейку o.ii KK l , ораььуо i coo iс --Tpi.Cv.4f -резервно о ресур- чтс со, ер;кнмое регистра 1 1

r I, all- фрОНТО i ,

км i i,,v а ос... JCTCH t n r;c с о, что j ч . .ч e re i н t ичмрчеаь с вьиоа, i г

1О,

t г е .

ti 1 41 О л О

соре Б

uBuMV liMIIV TbCV

на i, D

if -S , .

г Л hi . - Y

Пс чет-

,

, уз .а 54 соцрр/гим м регистра 11, ;;i е р зерьного ресурnxt ,ax

i ,, Г с п г,--.., pi (бргчг VH : i vi/ и ,i..jat 11.я c(J. h ячейку блока 1/ памяти, выбран- hvij по содержимому реггстиа 10, зэ- адрр: резервного ресурса Кроме ioro, по четвертому тактовому .очпу: ч у ча выходе переполнения счетчика /Ь формируется импу.1 ъсчьй сигнал 1 Ь с ) уровня, , г ri ) 1 J. ; r.7H-uJ СБ нп JcviriH-i фрон i ом уста-- нав триггеры 21 н b i. состоя- се т 1 еггст«енно ысс.- ч низкого лс1ГИ геко т ,vo -н г, чч 1 -.гпегОЛЯРТ заьерше.нте корректировки г- кущего фрагмен а и готозность етпоисгвл к :иптояиеьи о ксреект . з У. фрагмр i -a i слройкь матрг.чноГ 5 коммутатора i. Начало корр.кгиповкь каждого сгеду и егс фрагмента к /мутации |)лч;-1(г J CH :;огачеи нмт упг.са гачальiof; установки на ччод

г ммут аил шног устройства и осущег вляется апп- логичьг -innoaMirvry

12

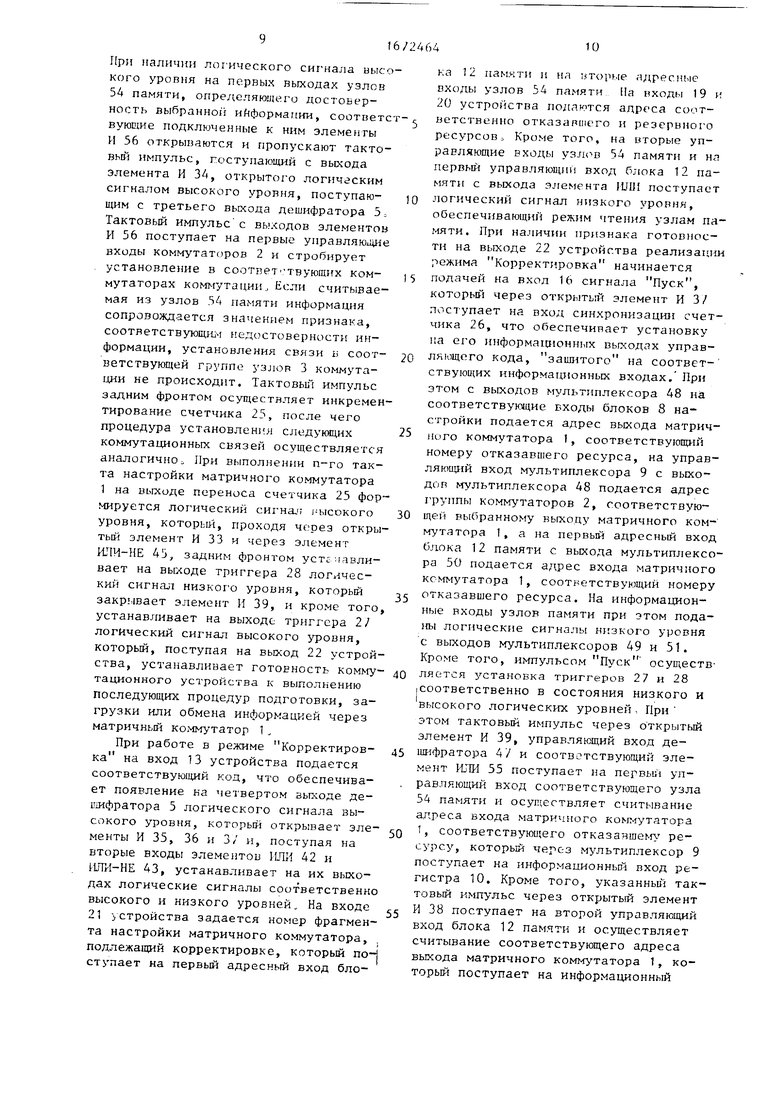

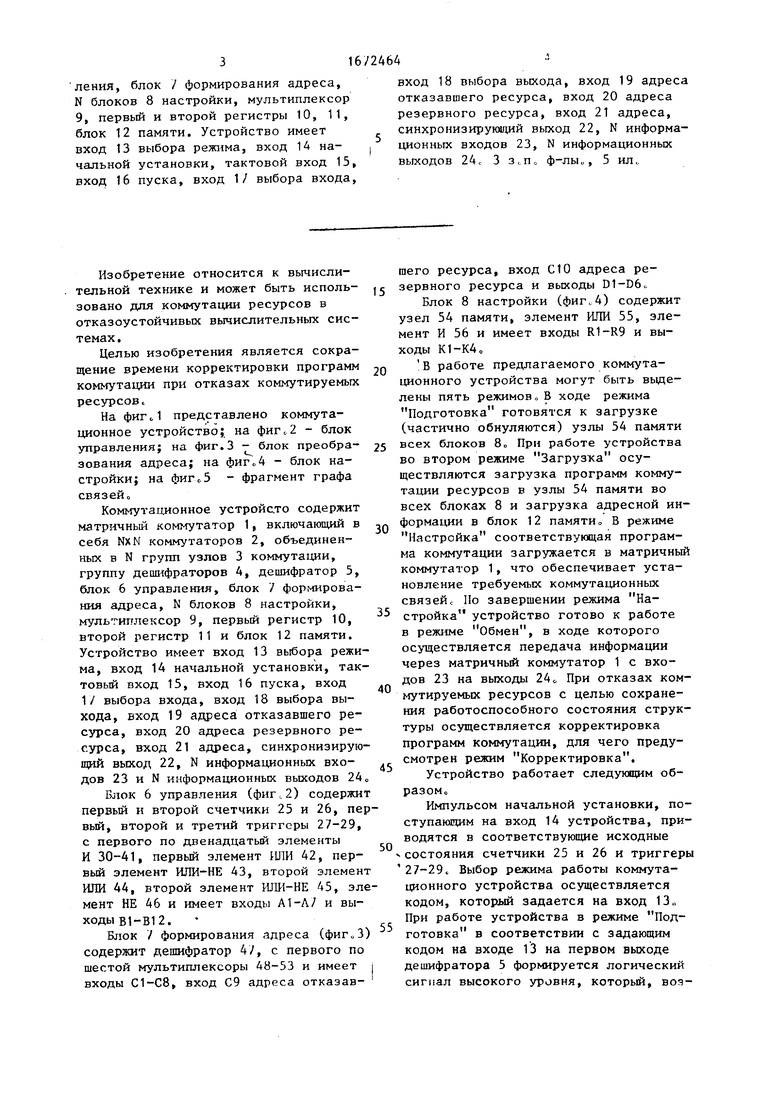

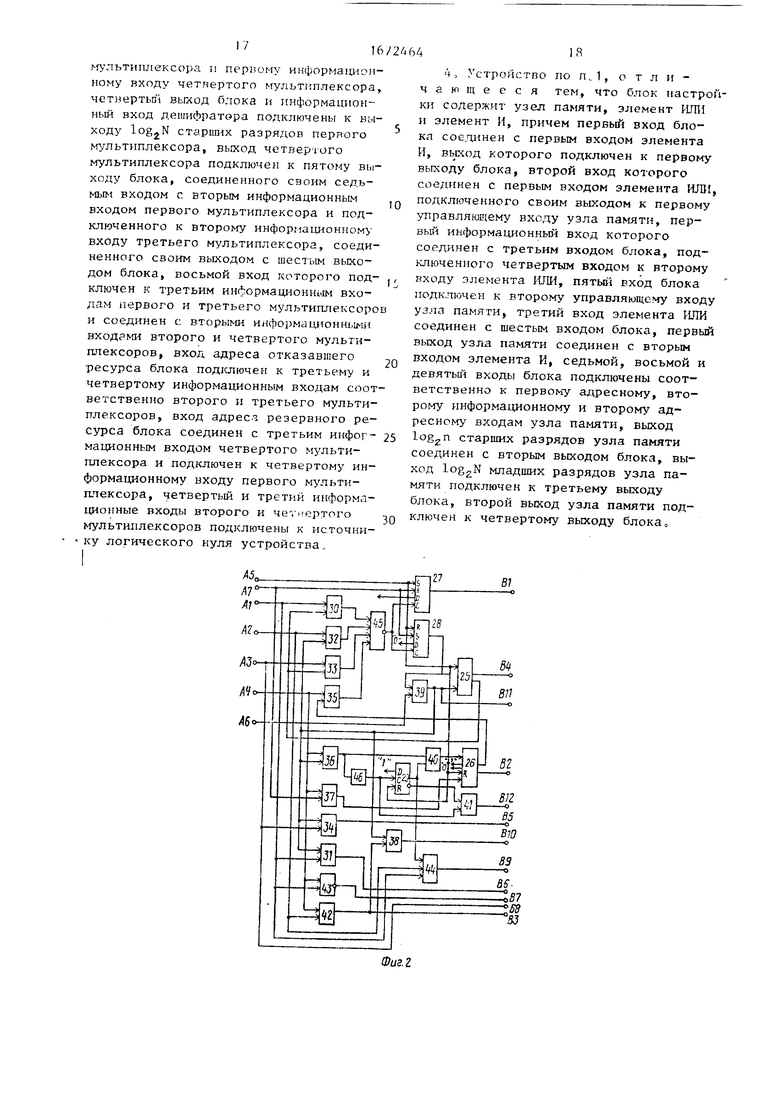

В качестве примера рассмотрим процедуру корректировки списка связей, реализуемых коммутационным устройством, для фрагмента графа связей Сфиг о 5) при замене отказавшего ресурса 3 резервным ресурсом 5 Для сохранения работоспособного состояния системы межресз рсные связи (3, 1) и v4, 3) должны быть разомкнуты, а связи (5, 1) и (4, 5) должны быть установлены для проведения укатанной корректировки списка связей, при этом выполняются следуюпше операции

Считмванн адресов точек коммутации из узлоь 54 памяти п блока 12 памяти по адресу отказавшего ресурса 3 с последующим обю ленчем содержимого выбранных ячеек, что вызываем рлзрыг, связей 3, 1) и (4, 3).

Запись в з.1ы 5ч памлти и блок 12 памяти по адресу резервного ресурся 5 содержимого регистров 10 и 11 соот- зетственно, что обеспечивает уставов- Ч ку коммутационной связи (4, 5)„

Запись ч соответструютий узел 54 па яти по адресу 1 из регистра 11 )-ого ресурс0 5 и ь бчок 12 памлти по чдресу 4 из ре- гт стра 10 адреса резервно о ресурса 5, что обесчечнвает установку комму- г.ионпои i вязи С5, О

Та.ч-г-i образом, корректировка программы коммутации, соответствующей одному фрагменту настройки матричного KOitMy raropa, в предлагаемом устройстве может быть вьтолнена в течение четырех тактов

0

5

40 Ф о р м у л

изобретения

1 Коммутационное устройство, содержащее матричный коммутатор, состояний из N групп узлов коммутации, содержащий в ка/,ой группе N коммута- тор В, группе деил1фрчторов, причем N информационных входов и N информационных выходов матричного коммутато- pj являются информационными входами и

рыходами устройства соответственно, о г л н ч а ю щ е е с я тем, что, г- ЦРЛЬЮ ускорения коррэктировки программ коммутации при отказах коммутируемых ресурсов, в устройство вяедены, дешифратор, блок управления, Сл л формирования адреса, N блоков настройки, мультиплексор, первый н второй регистры, Слок памяти, причем вход вьрора режима устройства соединен

входом дешифратора, первый, «торой, третий и четвертый вычпдм которого подключены соответственно к первому, второму, третьему и четвертому входам блока управления, пятый, шеетон и седьмой входы которого соединены с вход vi начальной установки, тактовым входом и входом пуска устройства соответственно, первый, второй и третий выходы блока управления подключены соответственно к первому, второму и третьему входам блока формирования адреса, чет тертый которого объединен с адрес 1ым входом матричисп о коммутатора и псдк тючен к четвертому выходу блока упр мления первые, вто- рыс, третьи и четвертые оходы всех бпоков настройки соответственно объединены и подключены к пятому, шестому седьмому и выходам бчока управления соответственно, девятый вы..од блока управления соединен с первым управляющим входов блока памяти и подключен к пятому входу всех бл - ков настройки, шестые, седьмье и восьмые входы которых соответственно объединены и подключены соот етствен- нс к пегиому, второму и третьему выходам блока формирования п;реса, пя

которого соединены соответ ст венно с входом выбора входа, входом BI opa выхода, входом адреса отказавшего ресурса и входом адреса резервного ресурса устройства, первый адресный вход блока памяти и девятые входы всех блоков настройки объединены и подключены к входу адреса устройства первые входы каждого i-го (i - 1,N) блока настройки соединены соответственно с i-ми управляющими входами первой группы матричного коммутатора каждые i-ые управляющие входы второй группы которого подключены к выходам i-x дешифраторов группы, соединенных своими входами с вторыми выходами 1блоков настройки, третьи выходы каждого 1-го блока настройки подключены к 1-м адресным входам группы матричного коммутатора, четвертые выходы каждого 1-го блока настройки соеди- ены с i-ми информационными входами мультиплексора, управляющий вход которого подключен к четвертому выходу блока формирования адреса, пятый выход которого соединен с информационным входом блока памяти, а шестой выход подключен к второму адресному

п 5

0

5

0

5

0

5

входу блока памяти, «торой управ плющи и вход которого соединен с десятым выходом блока управгтения, одиннадцатый выход которого подклочен к синх;г- ннзирующему выходу устройства, а двенадцатый выход соединен с упражняющими входами первого и второго регистров, выходы югорых пгдключены соответственно к входам адреса отказавшего и резервного ресурсов блока формирования адреса, информационный вход первого регистра соединен с выходом мультиплексора, информационный вход второго регистра подключен к выходу блока памяти, каждый i-й (,N) информационный вход матричного коммутатора подключен i-му информационному входу всех групп узлов коммутации и соединен с информационным входом i-ro коммутатора каждой группы узлов коммутации, ВЬЕХОДЫ всех коммутаторов каждой з -й группы узлов коммутации объединены и подключены к выходу i-й группы узлов коммутации, который подключен к i-му информационному выходу матричного коммутатора, адресный вход которого подключен к первому адресному входу всех групп узлов коммутации и соединен с первыми адресными входами всех коммутаторов каждой i-й группы узлов коммутации, вторые адресные входы всех коммутаторов кадкой i-й группы узлов коммутации подключены к вторым адресным входам i-й группы узлов коммутации и соединены с i-м адресным входом группы матричного коммутатора, каждые i-тые управляющие входы первой группы которого подключены к соответствующим первым управляющим входам i-й группы узлов коммутации и соединены с первыми управляющими входами всех коммутаторов i-й группы узлов коммутации, каждый i-тые управляющие входы второй группы матричного коммутатора подключены к управляющим входам i-й группы узлов коммутации и соединены с вторыми управляющими входами всех коммутаторов i-й группы узлов коммутации

ментов И, nepBiiо элемента ИЛИ-НЕ и второго элемента ИЛИ объединены и подключены к первому входу блока, второй вход которого соединен с первым входом третьего элемента И, первого элемента ИЛИ и вторым входом второго элемента ИЛИ, третий вход блока соединен с первым входом чет- верто;о и пятого элементов И, четвертый вход блока соединен с первым входом I ccroio, седьмого, восьмого и пятого -элементов И и вторыми входами первого эпемеша ИЛИ-НЕ и первого элемента И1ТЛ, кот первого элемента ИЛИ по хклк;- -и к ьервому входу девя- ттго эле И и третьему выходу блока, пягыи вход которого соединен с входом v с Tail Вки в 1 первого триггера, f ъходами ст новки в О вто- рого и тгеть.го триггеров и дервого и второ-о счетчиков, шестой вход блока подп к первому входу деся- :-ле,:енга И, выход которого соединен с вторым входом второго, третьего nj -mrc, седьмого и девятого элементов И ь счетно,j jходом первого счет- вх д Ото а управления : -i устачонкч в О перС РХОДОМ УСТДНОЬГИ В

k- i п ,1иТ1 лючен к ч .L-МОГО юмгнта И,

. Н. J..H Н С ЗХОДОЧ

тороги счетч. ча, под:.;ол :i Oi о i i чгткьсч r..uriOi-i к вы- xi ду одиннадцатого нта М, первый вх i.r ,г, i-opoi о с ишдом c-.fcx) jj PMi- i a И и вьтсодом элемен- а .Г, - ixод эчек,. .та НЕ соединен с вх дог: v t Hxpoi Huai.4H третьего триггера и ; PBLIM входом двенадцатого элемента И, вюрой вход которого подключен к инлер но выходу третьего триггера, лрямой выход кс гсрого со-. еднн- Н с третьим входом второго элемента ИЛИ и подключен к второ -гу входу одиннадцатого элемента И, инфор- Mai.i.oHK.ite PM оды пергого ь второго счетчиков подьлючнн1 .-оотяетственно к пepвo y и второму m гкода -- блока, пыход переноса второго гчика подключен к второго входу шестого ле- .чента I, соедиченного споим выходом с перв входом элемента ИЛИ-НЕ, дторс, третий и четвертый входы которто подключены соогветст- ченно к выходам первого, третьего и четвертого элементов И, выход второго элемента ИЛИ-НЕ соединен с вхо

0

- „ 5 Q

J ;

0

5

С

5

дами синхронизации первого и второго триггеров, выход второго триггера подключен к второму входу десятого элемента И, выход первого элемента ИЛИ соединен с третьим выходом блока, четвертый выход которого подключен к информационному вьходу перлого счетчика, выход переноса которо:о соединен г вторыми входами первого и четвертого элементов И, пятый и шестой выходы блока подключены к выходам пятого и второго элементов И, седьмой выход блока подключен к выходу первого элемента ИЛИ-НЕ, восьмой выход блока соединен с третьим входом блока управления, дчвп-ый, девятый, одиннадцатый и двен .дцатые выходы блока подкшчены соответственно к выходам второго элемента ИЛИ, девятого элемента И, десятого элемента И и днеьодцатого элемента Н, информационные входы первого и третьего триггеров и первый информационньм вход второго счетчика соединены с источником логической единицы устройства, информационный тход второго триггера и iторой информационный вход второго счет соединены с источником ло- гическо о нуля усiроиства

S7

°ДЗ

ФиеЗ

Фи2.5

| Коммутационное устройство | 1984 |

|

SU1246109A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-08-23—Публикация

1989-07-11—Подача