Изобретение относится к вычислительной технике, может быть использовано для буферизации сообщений при обп мене информацией между двумя электронными вычислительными мапшнами и является усовершенствованием известного устройства по авт.св. №1180906.

Цель изобретения - повышение производительности обмена информацией между ЭВМ.

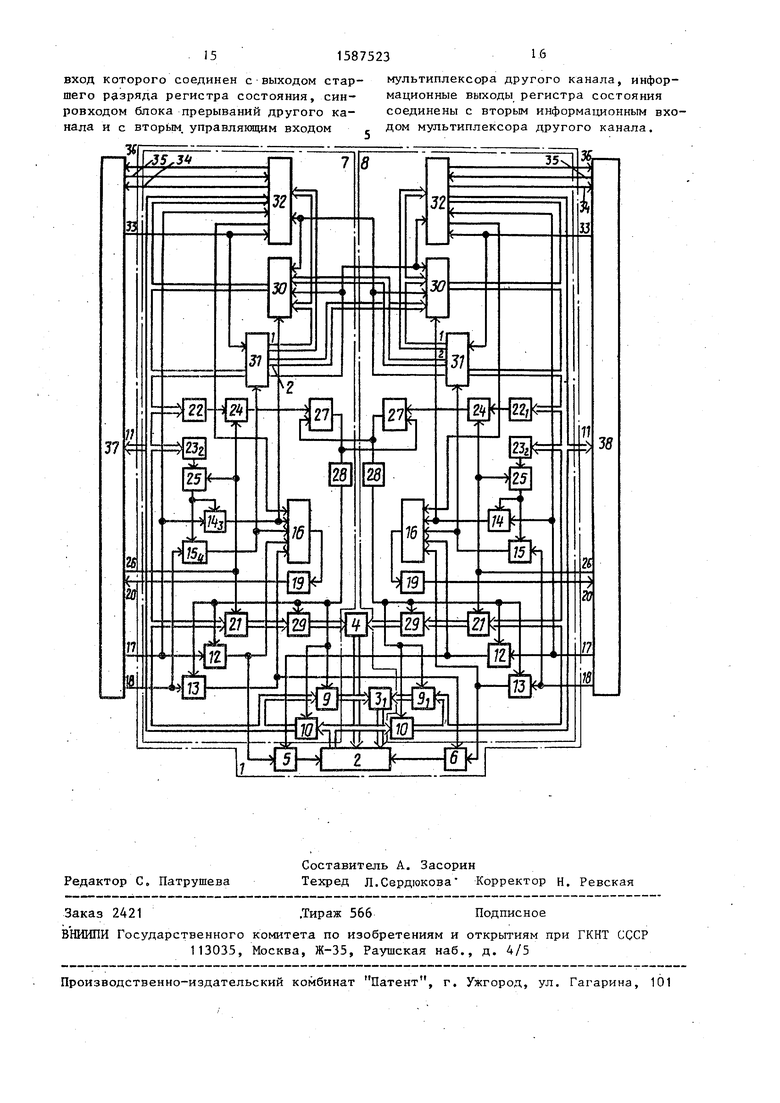

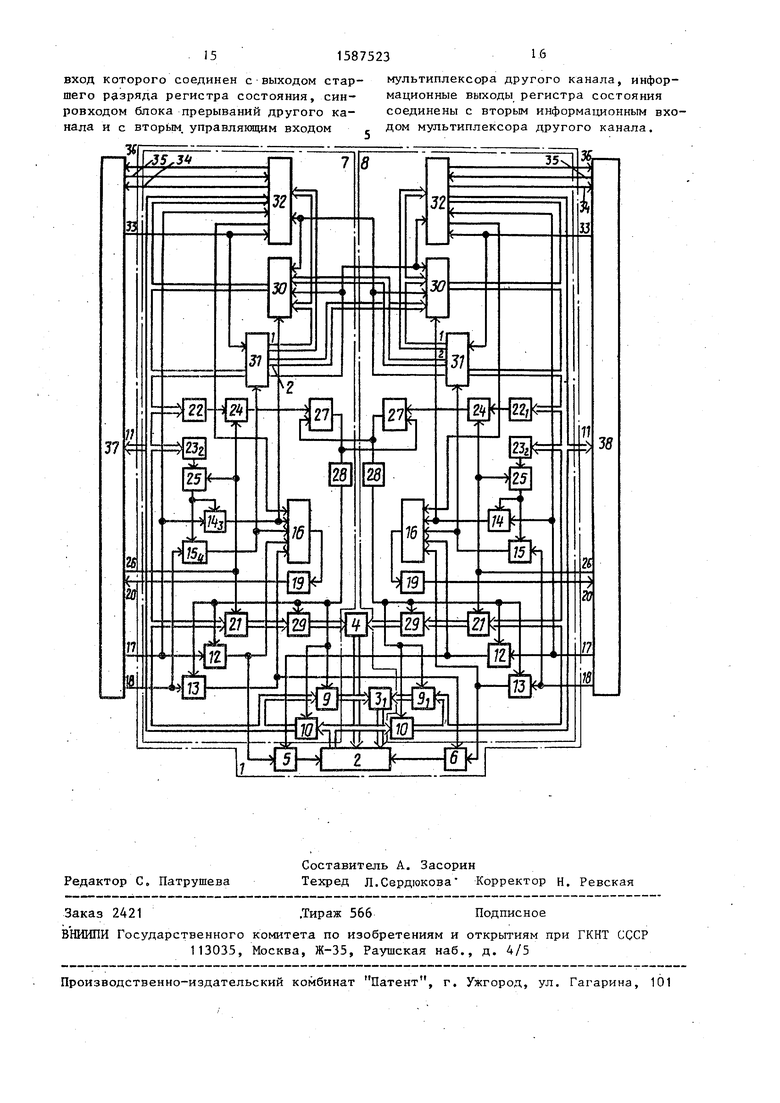

На чертеже дана схема предлагаемого устройства.

Устройство 1 сопряжения содержит блок 2 памяти, первую 3 и вторую 4 группы элементов ШШ, первый 5 и второй 6 элементы ИЛИ, первый 7 и второй 8 каналы, каящый из которых содержит первую 9 и вторую 10 группы элементов И, информационные входы-выходы (линии) 11 устройства, первый 12, второй 13, третий 14 и четвертый 15 элементы И, элемент ИЛИ 16, входы считывания 17 и записи 18 устройства, элемент 19 задержки, управляющий выход 20, регистр 21 адреса, первый 22 и второй 23 компараторы адресов, пер 1вый 24 и второй 25 трипперы, тактовый Ьход 26 устройства элемент И-НЕ 27, элемент НЕ 28, третью 29 группу элементов И, мультиплексор 30, регистр 31 состояния, блок 32 прерывания, вход 33 установки устройства, выход 34 требования прерывания устройства, вход 35 и выход 36 предоставления прерывания устройства. Первая 37 и вторая 38 ЭВМ соответственно соединены с каналами 7 и 8.

Блок 2 памяти представляет собой оперативное запоминающее устройство емкостью 4-32 К 16-разрядных слов.

Первый компаратор 22 адресов предназначен для определения группы адреСП

00

4j

INJ

сов,. соответствующих адресному полю блока 2 памяти, вьщеляемых программно из общего адресного пространства ЭВМ 37 и 38, и представляет собой обычную схему компарации двоичного кода в позиционньй. Перйый компаратор 22 адреса может быть выполнен, например, на микросхемах сравнения

из D-триггеров с входами начальной установки, информационные входы которых являются информационными входами регистра 31 состояния, а тактовые входы, соединенные вместе, и входы установки, соединенные вместе, соответственно тактовым входом и входом установки. Регистр 31 может быть выполнен

niAXl jrZl Al в I JU U.X - VXV V l- b « f м....

типа к 555 СПГ« На первые информацион-ю «а микросхемах типа К 555 ТМ8,К 555

ные входы поступает адрес устройства по линии It устройства. На вторые-входы поступает заданный код, например, с помощью перемычек или выключателей типа ВДМ-1.

Второй компаратор 23 адреса предназначен для определения адреса регистра 31 состояния из общего адресного пространства ЭВМ 37 и 38 и предТМ9 и др., представлякщих собой набор D-триггеров с входами установки в О выходных сигналов.

При подаче на входы установки сиг- 15 нала О все D-триггеры переходят в состояние логических О независимо от состояний информационных входов.

При переходе входа устаной ки в состояние логической 1 разрешается заставляет собой обычную схему компара- 20 в регистр 31 состояния.

дни двоичного кода в позиционный. Второй компаратор 23 адреса может быть вьтолнен аналогично первому компаратору 22 адресов. При совпадении адреса

D-триггеры запоминают информацию, стоящую на их информационных входах при переходе тактового импульса из состояния логического О в состояние

регистра 31 состояния с заданным вы- 25 логической 1 .

ход переходит в состояние логической

1.

Регистр 21 адреса предназначен для хранения адреса ячейки блока 2 памяти

Назначение разрядов регистра 31 состояния для каждого из каналов .7 или 8 следующее: 1 группа и оставшиеся разряды используются для организации

в пределах одного цикла обращения ЭВМ зо Работы ЭВМ 37 и 38 с устройством 1 по

37 или 38 к устройству 1.сопряжения. Регистр 21 адреса состоит из D-триггеров, информационные входы которых являются информационными входами регистра 21 адреса,- а тактовые входы, соединенные вместе, тактовым входом, количество D-триггеров регистра 21 адреса определяется количеством разрядов двоичного слова ЭВМ 37 или 38, которое обычно равно 16. Регистр 21 адреса может быть выполнен на микро- схемах типа К 155 ТМ5, К 155 та7 и др., представляющих собой D-триггеры, соЬтояние каждого из которых меняет35

40

прерьюаниям; 2 группа разрядов используется для передачи сообщения от одной ЭВМ другой, причем, разряд разрешения прерьшания 1 группы устанавливается в 1 ЭВМ 37 или 38 для разрешения работы по прерыванию и передачи адреса вектора прерьшания блока 32 прерьшания соответственно канала 7 или 8; разряд готовности канала 7 или 8 группы 1 устанавливается в 1 для выработки устройством 1 сигнала требования прерьшания соответственно в ЭВМ 37 или 38 (самопрерывание, например, при проверке работы блока 32

ся в соответствии с состоянием инфор- 45 Р РЫвания); оставшийся разряд Р азре- мационного входа, когда тактовый вход шения работы устанавливается в 1

ЭВМ 37 или 38 для вьфаботки устройст - вом 1 сигнала требования прерьюания

находится в состоянии логической 1

а при переходе тактового импульса в

О каждый

состояние логического

соответственно в ЭВМ 38 или 37

л ЧУЛ П Г ЬС , ЛГА vy ,-.,- :

D-триггер. запоминает записанную в нём Q (встречное прерьшание, например, при

..ь-.г - ..4 fi f f fimr TTTfct ч KM tf Trn

информацию и состояние его остается неизменным Независимо от состояния .информационного входа.

Триггеры 24 и 25 представляют сопередаче сообщения от одной ЭВМ к другой) .

Считывание информации с регистров 31 состояния происходит в каждом каJt,Lfim Л- в в л.л-г - .,---f,. бой D-триггеры аналогично триггерам , нале через четвертую группу 30 элемен- регистра 21 адреса.iтов И. Количество элементов определяРегистры 31 состояния предназначе- ется разрядностью двоичного слова ны для обмена сообщениями между ЭВМ ЭВМ 37 и 38. 37 и 38. Регистр 31 состояния состоит

из D-триггеров с входами начальной установки, информационные входы которых являются информационными входами регистра 31 состояния, а тактовые входы, соединенные вместе, и входы установки, соединенные вместе, соответственно тактовым входом и входом установки. Регистр 31 может быть выполнен

...

«а микросхемах типа К 555 ТМ8,К 555

ТМ9 и др., представлякщих собой набор D-триггеров с входами установки в О выходных сигналов.

При подаче на входы установки сиг- нала О все D-триггеры переходят в состояние логических О независимо от состояний информационных входов.

При переходе входа устаной ки в состояние логической 1 разрешается в регистр 31 состояния.

D-триггеры запоминают информацию, стоящую на их информационных входах при переходе тактового импульса из состояния логического О в состояние

логической 1 .

Назначение разрядов регистра 31 состояния для каждого из каналов .7 или 8 следующее: 1 группа и оставшиеся разряды используются для организации

Работы ЭВМ 37 и 38 с устройством 1 по

прерьюаниям; 2 группа разрядов используется для передачи сообщения от одной ЭВМ другой, причем, разряд разрешения прерьшания 1 группы устанавливается в 1 ЭВМ 37 или 38 для разрешения работы по прерыванию и передачи адреса вектора прерьшания блока 32 прерьшания соответственно канала 7 или 8; разряд готовности канала 7 или 8 группы 1 устанавливается в 1 для выработки устройством 1 сигнала требования прерьшания соответственно в ЭВМ 37 или 38 (самопрерывание, например, при проверке работы блока 32

соответственно в ЭВМ 38 или 37

(встречное прерьшание, например, при

- ..4 fi f f fimr TTTfct ч KM tf Trn

передаче сообщения от одной ЭВМ к другой) .

Считывание информации с регистров 31 состояния происходит в каждом ка-.,---f,. Таким образом, для казкдой из ЭВМ 37 или 38 все разряды соответствующего регистра 31 состояния канала 7 или 8 доступны по записи, при считывании - доступны разряды 1 группы, оставшийся разряд соответствующего регистра 31 состояния канала 7 или 8, разряды 2 группы регистра 31 состояния другого

мычках. Тогда заданный с помощью пере ключател.ей (или перемычек) адрес Bei6 тора прерывания по сигналу разрешения передачи адреса вектора прерывания пе редается с информационных выходов бло ка 32 прерывания в ЭВМ.

Выполнение схем задания адресов компаратора 22,23 адресов и адреса

канала (соответственно, 8 или 7) и ос-ю вектора прерывания с применением петавшийся разряд регистра 31 состояния другого канала как готовность другого канала (собтветственно, 8 или 7).

Блок 32 прерывания в. каждом канале устройства 1 позволяет организовать работу по прерываниям с соответствующей ЭВМ и обеспечивает вьфаботку сигнала требования прерывания (ТПР), прием и передачу сигнала предо- , ставления прерывания (ППР), формирование и передачу адреса вектора прерьшания. Блок прерьшания может быть вьшолнен на микросхемах серии К 555.

15

20

реключателей (или перемычек) расширяет возможности применения устройства 1 для связи двух или более ЭВМ. По сигналу установки триггеры ТПР и ППР блока 32 прерьшания устанавливаются в . Таким образом, в начальном состоянии логика прерывания подготовлена к вьфаботке сигнала ТПР по сигналам разрешения прерывания и готовности одного из каналов, сигнал ППР в начальном состоянии пропускается с входа блока 32 прерывания на выход

Каждая из групп 9,10,29 и 3,4 пред 25 ставляет собой соответственно набор отдельных элементов И и ШШ, имеющих по два входа каждый. Количество соответствующих элементов в группе опреде ляется количеством разрядов двоичного слова ЭВМ. Как адрес, так и данные передаются по одним и тем же шинам линии 11, являются двунаправленными, что обеспечивается канальными приемопередатчиками ЭВМ. Это означает, что по одним и тем же шинам информация может как приниматься, так и передаваться ЭВМ относительно одного и того же устройства.

Основными элементами являются триггеры ТИР и НИР, которые можно выполнить на микросхемах К 555 ТМ2, Работа блока 32 прерьшания разрешена при 1 на входе разрешения прерьшания. Если на любом из входов готовности блока 32 прерьшания присутствует логическая 1, то она через элемент ИЛИ, объединяясь по И с сигналом разрешения прерывания устанавливает в t триггер ТПР, тем самым формируется сигнал ТИР на выходе 34 устройства 1. Однако, если сигналы готовности будут сброшены, то сигнал ТИР на выходе 34 устройства 1 снимается. ЭВМ, получив сигнал ТИР, вырабатьшает сигнал счи- тьшания и ИПР, поступающие на соответ ствунлцие входы считьтания и предоставления прерьшания блоку 32 прерьшания. Ио сигналу считывания при уело- ВИИ, что ТПР находится в 1, устанавливается в О триггер ПИР, тем самым запрещается прохождение сигнала ППР через блок 32 прерывания с входа 35 на выход 36 устройства 1. С друго- го плеча триггера ИПР формируется сигнал разрешения передачи адреса вектора прерьшания, по которому: сбрасывается триггер ТПР, формируется адрес вектора прерывания.

Схему формирования адреса вектора прерывания блока 32 прерьшания можно выполнить, например, на элементах И и переключателях типа ВДМ-1 или пере

мычках. Тогда заданный с помощью пере- ключател.ей (или перемычек) адрес тора прерывания по сигналу разрешения передачи адреса вектора прерывания передается с информационных выходов блока 32 прерывания в ЭВМ.

Выполнение схем задания адресов компаратора 22,23 адресов и адреса

вектора прерывания с применением пе

реключателей (или перемычек) расширяет возможности применения устройства 1 для связи двух или более ЭВМ. По сигналу установки триггеры ТПР и ППР блока 32 прерьшания устанавливаются в . Таким образом, в начальном состоянии логика прерывания подготовлена к вьфаботке сигнала ТПР по сигналам разрешения прерывания и готовности одного из каналов, сигнал ППР в начальном состоянии пропускается с входа блока 32 прерывания на выход.

Каждая из групп 9,10,29 и 3,4 пред- ставляет собой соответственно набор отдельных элементов И и ШШ, имеющих по два входа каждый. Количество соответствующих элементов в группе определяется количеством разрядов двоичного слова ЭВМ. Как адрес, так и данные передаются по одним и тем же шинам линии 11, являются двунаправленными, что обеспечивается канальными приемопередатчиками ЭВМ. Это означает, что по одним и тем же шинам информация может как приниматься, так и передаваться ЭВМ относительно одного и того же устройства.

ЭВМ 37 и 38 представляют собой микроэвм, например, типа Электроника -60.

Функции синхронизации при передаче адреса и приеме-передаче данных выполняют сигналы управления, поступающие от ЭВМ на входы 17,18,26.

Сигнал синхронизации на вход 26 устройства 1 вырабатывается ЭВМ. Передний отрицательный фронт этого сигнала означает, что адрес находится на линии 11. Сигнал на входе 26 сохраняет активный уровень до окончания цикла обращения ЭВМ к устройству 1.

I

Сигнал Ввод вырабатывается ЭВМ, поступает на вход 17 во время действия сигнала на входе 26 и означает .что ЭВМ готова принять данные от блока 2 памяти или регистра 31 состояния при операции Считьшание.

Сигнал Вывод вырабатьшается ЭВМ, поступает на вход 18 во время действия сигнала на входе 26 и означает, что на линии 11 помещены.данные ртя записи в блок 2 памяти или регистра 31 состояния при операции Запись.

Сигнал на выходе 20 формируется пу «О информацией с блокйм 2 памяти, то со

тем подачи сигналов Ввод или Вывод на элемент 9 задержки и инфор- мируеу ЭВМ о том, что данные установлены или приняты с линии 11 устройст- вон. Длительность определяется време- 15 ствующего канала нем обращения к блоку 2 памяти (время обращения к регистру 31 состояния меньше времени обращения к блоку 2 памяти), поскольку наличие сигнала на выходе 20 сигнализирует о завершении 20 операции ввода-вывода. Элемент задержки может быть выполнен на микросхемах серии К 555.

. Цри включении питания или программно ЭВМ вырабатьшает сигнал Сброс, чтобы вьшолнить начальную установку всех устройств, подключенных к ЭВМ. По сигналу Сброс, поступающему на вход 33 устройства 1, происходит начальная установка регистра 31 состояния и блока 32 прерывания.

Устройство работает следующим образом.

стороны другой ЭВМ в это же время (од новременно) возможен обмен с регистром 31 состояния или передача адреса вектора прерывания блока 32 соответОбращение ЭВМ 37 и 38 к регистрам 31 состояния устройства 1 может проходить одновременно. Рассмотрим в качестве примера циклы Вывод, Ввод при обращении к регистру 31 состояния.

25

30

ЭВМ 37 или 38 в адресной части цик ла Вьшод передает по линии 11 адреса регистра 31 состояния. На-входе 26 присутствует высокий потенциал 1 Второй компаратор 23 адреса компари- рует адрес и в случае совпадения его с адресом регистра 31 состояния сигнал логической 1 с выхода компарато ра 23 адреса устанавливает в 1 триг гер 25.

При включении питания любой из ЭВМ 37 или 38 вырабатьгоается сигнал Сброс, который уровнем логического О устанавливает в начальное состояние регистр 31 состояния и блок 32 прерывания соответствуюпцего;. канала 7 или В. После перехода сигнала начальной установки в состояние логической 1 ЭВМ 37 или 38 может выполнять операции обмена. I

Обмен информацией между ЭВМ 37 или 38 и устройством 1 сопряжения происходит циклами Ввод или Вывод. Выдача адреса вектора прерывания блоком прерьшания 32 канала 7 или 8 происходит соответственно при прерьшании программы ЭВМ 37 или 38.

Со стороны ЭВМ 37 обмен осуществляется с регистром 31 состояния, блоком 32 прерывания канала 7, блоком. 2 памяти устройства 1, со стороны ЭВМ 38 - с регистром 31 состояния, блоком 32 прерывания канала 8, блоком 2 памяти.

Так как в каждый канал устройства 1 введены блок 32 прерывания и регистр 31 состояния и доступ к ним не зависит от доступа к блоку 2 памяти, то обмен информацией ЭВМ 37 и 38 с указанными узлами устройства 1 может проходить одновременно (параллельно). Кроме того, если одна из ЭВМ обменивается

информацией с блокйм 2 памяти, то со

ствующего канала

стороны другой ЭВМ в это же время (одновременно) возможен обмен с регистром 31 состояния или передача адреса вектора прерывания блока 32 соответтвующего канала

Обращение ЭВМ 37 и 38 к регистрам 31 состояния устройства 1 может проходить одновременно. Рассмотрим в качестве примера циклы Вывод, Ввод при обращении к регистру 31 состояния.

ЭВМ 37 или 38 в адресной части цикла Вьшод передает по линии 11 адреса регистра 31 состояния. На-входе 26 присутствует высокий потенциал 1. Второй компаратор 23 адреса компари- рует адрес и в случае совпадения его с адресом регистра 31 состояния сигнал логической 1 с выхода компаратора 23 адреса устанавливает в 1 триггер 25.

С некоторой задержкой после уста- новки адреса ЭВМ 37 или 38 устанавливает на входе 26 сигнал О, триггер .25 запоминает записанную в нем информацию. .

После адресной части ЭВМ 37 или 38 помещает на линии 11 данные, которые необходимо записать в регистр 31 состояния, после чего устанавливает на входе 18 сигнал Вывод. Так как

на втором входе элемента И 15 присутствует 1, то сигнал Вьшод через элемент И 15 поступает на тактовый вход регистра 31 состояния. По переднему фронту сигнала Вывод происходит запись в регистр 31 состояния. Одновременно сигнал Вывод через, элемент ИЛИ 16 поступает на элемент 19 задержки, с выхода которого через поступает по управляющему выходу 20 в ЭВМ 37 или 38, в результате чего сигнал Вьшод устанавливается в О, снимаются данные с линии 11 и устанавливается высокий уровень 1 на входе 26.

Операция считьшания регистра 31 состояния происходит аналогично операции записи. Считывание информации в ЭВМ 37 и 38 происходит в цикле Ввод через мультиплексор 30 по линии 11.

Таким образом, при записи посредством регистра 31 состояния ЭВМ передает сообщение или подготавливает блок 32 прерьшания к работе по прерьтаниям при считьшании ЭВМ получает сообщение от другой ЭВМ либо контролирует готовность блока 32 прерьшания к работе по прерываниям.

Работу устройства 1 по прерываниям рассмотрим на примере работы блока 32 прерывания канала 7. Если прерьта- ние разрешено, то на входе разрешения прерьшания блока 32 присутствует 1 с выхода 1 группы регистра 31 состояния .

Если ЭВМ 38 готова к обмену с ЭВМ 37 по прерываниям, то она устай вли- вает оставшийся разряд регистра 31 состояния канала 8 в 1. При появ- .лении 1 на входе 8 готовности канала на выходе ТПР блока 32 прерывания устанавливается 1, Сигнал ТПР с вы- |хода 34 устройства 1 поступает в ЭВМ 37. ЭВМ 37, получив сигнал ТПР, устанавливает сигналы Ввод и через некоторое время ППР7 С входа 17 устройства Ввод поступает через вход считывания логики прерьшания и запрещает передачу сигнала Ш1Р с входа 35 через блок 32 на выход 36 устройства,1. Формируется сигнал разрешения передачи адреса вектора прерывания, пр кото

с тОм, е в15

м - я -30 о35з 58752310

Прерьгоание в ЭВМ 38 происходит аналогично прерыванию в ЭВМ 37. Таким образом, синхронизация работы двух ЭВМ при работе с устройством 1 при обмене сообщениями происходит по готовностям посредством регистров 31 состояния или прерьтаниям посредством регистров 31 состояния и блока 32.

Для понимания работы ЭВМ 37 и 38 с блоком 2 памяти устройства 1 рассмотрим в качестве примера циклы Вывод и Ввод для ЭВМ 37 и цикл Вы для .

20

25

вод

-ЭВМ 37 в адресной части цикла Вывод передает по линии 11 адрес ячейки блока 2 памяти, в которую необходимо записать информацию. На входе 26 при этом присутствует потенциал 1, который поступает на тактовые входы триггера 24 и 25 и регистра 21 адреса канала 7. В регистр 21 адреса производится запись адреса.

Первый компаратор 22 адреса компа- рирует адрес и в случае принадлежности его адресному полю блока 2 памяти подает сигнал на информационный вход первого триггера 24, который устанавливается в 1. Сигнал с выхода первого триггера 24 поступает на п ервый вход элемента И-НЕ 27, на втором входе которого присутствует высокий потенциал 1 с выхода элемента И-НЕ 21 канала 8, и вызьшает на его выходе появление сигнала О. На выходе элемента НЕ 28 появляется разрешающий сигнал 1, который поступает на вторые входы элементов 9,10,12,13,29.

С некоторой задержкой после уста

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля переключения контактов | 1986 |

|

SU1374249A1 |

| Устройство для сопряжения вычислительной машины с линиями связи | 1985 |

|

SU1262512A1 |

| Устройство для сопряжения двух вычислительных машин | 1986 |

|

SU1405064A1 |

| Двухканальное устройство для сопряжения двух электронно-вычислительных машин | 1987 |

|

SU1481780A1 |

| Устройство для сопряжения ЭВМ с магистралью | 1988 |

|

SU1605242A1 |

| Устройство для контроля и перезапуска ЭВМ | 1987 |

|

SU1464162A1 |

| Устройство для сопряжения ЭВМ | 1986 |

|

SU1462341A1 |

| Информационно-управляющая система центрального теплового пункта жилых общественных и промышленных зданий | 1987 |

|

SU1511751A1 |

| Устройство для обмена информацией двух электронно-вычислительных машин | 1984 |

|

SU1231507A1 |

| Устройство для сопряжения нескольких ЦВМ | 1982 |

|

SU1067493A1 |

Изобретение относится к вычислительной технике и может быть использовано для буферизации сообщений при обмене информацией между двумя электронными вычислительными машинами /ЭВМ/. Цель изобретения - повышение производительности обмена информацией между ЭВМ. Устройство сопряжения содержит блок памяти, две группы элементов ИЛИ, первый и второй каналы, каждый из которых содержит три группы элементов И, четыре элемента И, элемент ИЛИ, элемент задержки, регистр адреса, два компаратора адреса, два триггера, элемент И-НЕ, элемент НЕ, регистр состояния, блок прерывания, мультиплексор. 1 ил.

рому устанавливается сигнал ТПР в О 40 новки адреса ЭВМ 37 устанавливает на

и адрес вектора прерывания с выходов блока 32 прерьшания по линии 11 поступает в ЭВМ 37. Сигнал разрешения передачи адреса вектора прерывания с выхода блока 32 через элемент ИЛИ 16 поступает на элемент 19 задержки, с выхода которого через время tj, поступает по н.1ходу 20 в ЭВМ 37, в результате чего сигналы Ввод и ППР уставходе 26 сигнал О, регистр 21 адре са и триггер 24 при этом запоминают записанную в них информацию.

Спустя некоторое время после уста 45 новки адреса первой ЭВМ 37 вторая ЭВМ 38 также начинает выполнять цикл Вывод - помещает адрес на линии 11 канала 8. Компарирование адреса перв компаратором 22 адреса, установка

навливаются в О, прекращается пере- 50 триггера 24 в 1 и запись адреса в

дача вектора прерывания и устанавливается в О сигнал на выходе 20. Спеду ющая процедура прерьгеания возможна после снятия и нового появления 1 на входе готовности канала 8.

Прерьшание по готовности канала 7 с выхода 1 группы регистра 31 состоя ния канала 7 происходит аналогично прерьтанию по готовности канала 8.

входе 26 сигнал О, регистр 21 адреса и триггер 24 при этом запоминают записанную в них информацию.

Спустя некоторое время после уста- новки адреса первой ЭВМ 37 вторая ЭВМ 38 также начинает выполнять цикл Вывод - помещает адрес на линии 11 канала 8. Компарирование адреса первым компаратором 22 адреса, установка

регистр 21 адреса канала 8 происходят аналогично описанному для канала 7. Однако разрешающий сигнал на выходе элемента И-НЕ 27 не появляется, пос- КОЛЬКУ элемент И-НЕ 27 блокируется по второму входу сигналом О с выхода элемента И-НЕ 27 канала 7. После установки ЭВМ 38 адреса на входе 26 nor является сигнал О, что приводит к

запоминанию записанной информации в регистре 21 адреса и триггере 24 канала 8.

После адресной части ЭВМ 37, а с некоторой задержкой и ЭВМ 38 помещают на линии 11 данные,которые необходимо записать в блок 2 памяти, после чего на линиях 18 появляются сигналы Вывод.Так как на втором входе эле- мента И 13 канала 7 присутствует сигнал 1, то сигнал Вьшод через -элемент ИЛИ 6 поступает на управляющий вход блока 2 памяти Запись. При этом на адресных и информационных вхо дах блока 2 памяти присутствуют соответственно адрес с вьпсодов элементов И 29 через элементы ИЛИ 4 и данные с выходов элементов И 9 через элементы ИЛИ 3. Следовательно, происходит one- рация записи вьщанных ЭВМ 37 данных по необходимому адресу. Одновременно сигнал Вывод с элемента И 13 через элемент ИЛИ 16 поступает на элемент 19 задержки, с выхода которого через время ti поступает с выхода 20 устройства 1 в ЭВМ 37, в результате чего сигнал Вьшод устанавливается в О, снимаются данные с линии 11 и устанавливается высокий уровень 1 на входе 26. В это время сигнал Вывод на входе 18 канала 8 никаких действий не производит, так как он блокируется элементом И 13, на втором входе которого присутствует сиг нал О с выхода элемента НЕ 28.

Как только на входе 26 канала 7 утановится сигнал 1, триггер 24 и регистр 21 адреса устанавливаются в О, поскольку на линии 11 информа- ция отсутствует На выходе элемента И-НЕ 27 появляется сигнал 1, на выходе НЕ 28 - О, на выходах элемента И-НЕ 27 и элемента НЕ 28 канала 8 соответственно О и 1. Сигна с выхода элемента НЕ 28 поступает на вторые входы элементов И 9, 10, 12, 13, 29 канала 8. Аналогично каналу 7 сигнал Вьшод с входа 18 через .элемент ИЛИ 6 поступает на управляю- щий вход блока 2 памяти Запись, призводя операцию записи, и через элемент ИЛИ 16 на элемент 19 задержки. Завершение цикла Вывод дпя ЭВМ 38 происходит аналогично описанному дл

ЭВМ 37.

; Если во время операции записи даных, выполняющейся со стороны ЭВМ 38, ЭВМ 37 начинает выполнять цикл

Ввод, помещая адрес на линии 11, происходит заполнение адреса в регистре 21 адреса, установка триггера 24 и появление 1 на входе 17. Данное состояние сохраняется до момента установления триггера 24 канала 8 после окончания цикла Вывод в состояние О, что приводит к разбло- кированию элемента И-НЕ 27 канала 7 и, как следствие, к появлению сигнала 1 на выходе элемента НЕ 28. Сигнал Ввод через элемент И 12 поступает на управляющий вход блока 2 памяти Считьюание, производя считьша- ние информации из блока 2 памяти по заданному адресу, и через элемент ИЛИ 16 и элемент 19 задержки на выход 20, инциируя тем самым завершение цикла Ввод со стороны ЭВМ 37.

В случае одновременного обращения ЭВМ 37 и 38 к устройству 1 сопряжения т.е. одновременного помещения адреса на линии 11, происходит появление 1 на входах элементов И-НЕ 27, запомина ние . адресов в регистрах 21 адресов и присутствие сигналов Ввод или. Вывод на одном из входов 17 или 18 каналов 7 и 8.

Так как элементы И-НЕ 27 с их взаимными связями представляют собой RS-триггер, то одновременное поступление на их первые входы сигналов 1 приводит к неопределенному (непредсказуемому) состоянию выходов элемен- тбв И-НЕ 27. Однако это состояние будет одним из двух: на рыходе элемента И-НЕ 27 канала 7 присутствует О, а на выходе элемента И-НЕ 27 канала 8 1, или наоборот. Таким образом, работа устройства 1 сопряжения в дальнейшем происходит аналогично работе, описанной для режима последовательного обращения ЭВМ 37 и 38 к устройству 1 сопряжения

ЭВМ во время работы обмениваются как массивами информации, так и отдельными сообщениями-управляющего характера. В основном изобретении весь обмен информацией между двумя ЭВМ происходит через общую память. Функции синхронизации работы двух ЭВМ при одновременном обращении к устройству выполняются посредством семафора, расположенного в области памяти. Это усложняет работу с устройством, так как для синхронизации работы двух ЭВМ необходимо постоянно или периодически вести опрос семафора, что ведет к снижению производительности двух ЭВМ. Кроме этого, при одновременном обращении двух ЭВМ к памяти снижается быстродействие обмена: цикл обмена одной ЭВМ с устройством увеличивается в 1- 1,5 раза, а так как семафор расположе в области памяти, то быстродействие . устройства зависит от частоты опроса семафора, следовательно, быстродейст- вие устройства при обращении к памяти снижается в 1-1,5 раза.

В предлагаемом устройстве в аналогичных случаях обмена информацией между двумя ЭВМ имеется возможность организовать: обмен информацией через общую память устройства; обмен сообщениями посредством регистров состояния синхронизацию работы двух ЭВМ посредством встречных прерьюаний и регист- ров состояния.

Кроме этого, имеется возможность самопрерывания в каждом канале устройства, например, с целью проверки работы блока прерывания.

Существенными отличиями предлагаемого двухканального устройства сопряжения двух электронно-вычислительных машин от известного являются: введение в каждый канал устройства регист- ра состояния и четвертой группы элементов И, а также в каждом канале соответственное соединение входов регистра состояния и выходов четвертой группы элементов И с информационными входами-выходами устройства, соединение второй группы выходов регистра состояния с первыми входами соответствующих элементов И четвертой- группы другого канала, что позволяет произво дить обмен сообщениями между двумя ЭВМ посредством регистров состояния устройства; введение в каждый канал устройства логики прерьшания, а также в каждом канале соответственное со единение выходов логики прерывания с информационными входами-выходами уст ройства, соответственное соединение первой группы выходов регистра состояния с входами готовности данного ка- нала и разрешения прерывания логики прерьшания и с первыми входами соответствующих элементов И четвертой группы, соединение оставшегося выхода регистра состояния с первым входом со ответствующего элемента И четвертой группы, с входом готовности данного канала логики прерывания другого канала и с первым входом соответствующего элемента И четвертой группы друго го канала, что позволяет организоватв .работу двух ЭВМ в реальном масштабе времени по прерываниям.

Формула изобретения

Двухканальное устройство для сопряжения двух электронно-вычислительных машин по авт.св. № 1180906, о т-; личающееся тем, что, с целью повьшения производительности обмена информацией между ЭВМ, в каждый канал устройства введены второй компаратор адреса, второй триггер, регистр состояния, мультиплексор, блок прерывания, третий и четвертый элементы И, при этом в каждом канале информационные входы второго компаратора адреса, информационные входы регистра состояния, выходы мультиш1ек- сора, информационные выходы блока прерьшания подсоединены к информационным входам-выходам устройства, выход второго компаратора адреса соединен с D-входом второго триггера, синхро- вход которого подключен к синхровходу регистра адреса, третий и четвертый входы элемента ИЛИ соединены -соответственно с выходами третьего и четвертого элементов И, выход второго триггера соединен с первыми входами третьего и четвертого элементов И, вторые входы которых являются соответственно входами чтения и записи устройства, вторые входы элементов И четвертой группы и тактовый вход регистра состояния соединены соответственно с выходами третьего и четвертого элементов И, вход установки регистра состояния соединен с входом установки блока прерьшаний и является входом начальной установки устройства, выходы требования прерьшания и предоставления прерывания блока прерываний являются соответственно одноименными выходами устройства, а ;входы чтения и предоставления прерывания блока прерьшаний являются одноименными входами устройства, выход разрешения передачи адреса вектора прерывания блока прерывания соединен с пятым входом элемента ИЛИ, выходы разряда готовности данного канала и разрешения прерывания регистра состояния соединены с информационными входами блока прерываний и с первым информационным входом мультиплексора, первый управляющий

вход которого соединен с выходом стар- мультиплексора другого канала, инфор- шего разряда регистра состояния, син- мационные выходы регистра состояния ровходом блока прерываний другого ка- соединены с вторым информационным вхонала и с вторьм. управляющим входом К

(

Редактор С. Патрушева

Составитель А. Засорин

Техред Л.Сердюкова Корректор н. Ревская

Заказ 2421

.Тираж 566

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

дом мультиплексора другого канала.

Подписное

| Двухканальное устройство для сопряжения двух электронно-вычислительных машин | 1984 |

|

SU1180906A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-08-23—Публикация

1988-02-25—Подача