дом элемента задержки, выход дешифратора адреса соединен с информационным входом триггера, выход которого соединен с первым входом элемента ИНЕ, выход которого соединен с входом элемента НЕ и с вторым входом элемента И-НЕ другого канала, причем выходы элементов И третьей группы первого и второго каналов соединены с первыми и вторыми входами элементов ИЛИ первой группы соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля хода программ | 1988 |

|

SU1539785A1 |

| Устройство для контроля хода программ | 1989 |

|

SU1645960A1 |

| Устройство для прерывания программ | 1985 |

|

SU1256029A1 |

| Двухканальное устройство для сопряжения двух электронно-вычислительных машин | 1987 |

|

SU1425692A2 |

| Двухканальное устройство для сопряжения двух электронно-вычислительных машин | 1989 |

|

SU1647581A2 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1425683A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для отладки программно-аппаратных блоков | 1986 |

|

SU1363219A1 |

| Двухканальное устройство для сопряжения двух электронно-вычислительных машин | 1987 |

|

SU1481780A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1550523A1 |

ДВУХКАНАПЬНОЕ УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ДВУХ ЭЛЕКТРОННО-ВЫЧИСЛИТЕЛЬНЫХ МАШИН, содержащее блок памяти, два элемента ИЛИ, две группы элементов ИЛИ, причем каждый из каналов содержит два элемента И и две группы элементов И, при этом выходы элементов И первой группы соединены с первыми входами элементов И второй группы первого и второго каналов и образуют первый и второй информационные входы-выходы устройства соответственно, первые входы первого и второго элементов И первого и второго каналов являются входами считывания и записи устройства соответственно, адресный и информационный входы блока памяти соединены с выходами элементов ИЛИ первой и второй групп, первые и вторые входы второй группы элементов ИЛИ соединены соответственно с выходами элементов И второй группы первого и второго каналов, первые входы элементов И первой группы первого канала соединены с первыми входами элементов И первой группы второго канала и с информационными выходами блока памяти, входы считывания и записи которого соединены с выходами первого и второго элементов ИЛИ соответственно, выход первого элемента И первого канала соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом первого элемента И второго канала, выход второго элемента И первого канала соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом второго элеменI та И второго канала, отличающееся тем, что, с целью повыше(Л ния быстродействия, в каждый канал с устройства введены дешифратор адреса, регистр адреса, триггер, элемент задержки, третья группа элементов И, элемент ИЖ, элемент И-НЕ, элемент НЕ, при этом в каждом канале информационные входы дешифратора адреса соеди00 нены с информационными входами регисто со о ра адреса и с выходами элементов И первой группы, тактовьй вход триггера соединен с тактовым входом регистО) ра адреса и является тактовым входом устройства, выход элемента задержки является управляющим выходом устройства, выход элемента НЕ соединен с вторыми входами элементов И первой и второй групп, первого и второго элементов И и первыми входами элементов И третьей группы, вторые входы которых соединены с выходами регистра адреса, выходы первого и второго элементов И соединены с первым и вторым входами элемента ИЛИ соответст- венно, выход которого соединен с вхо

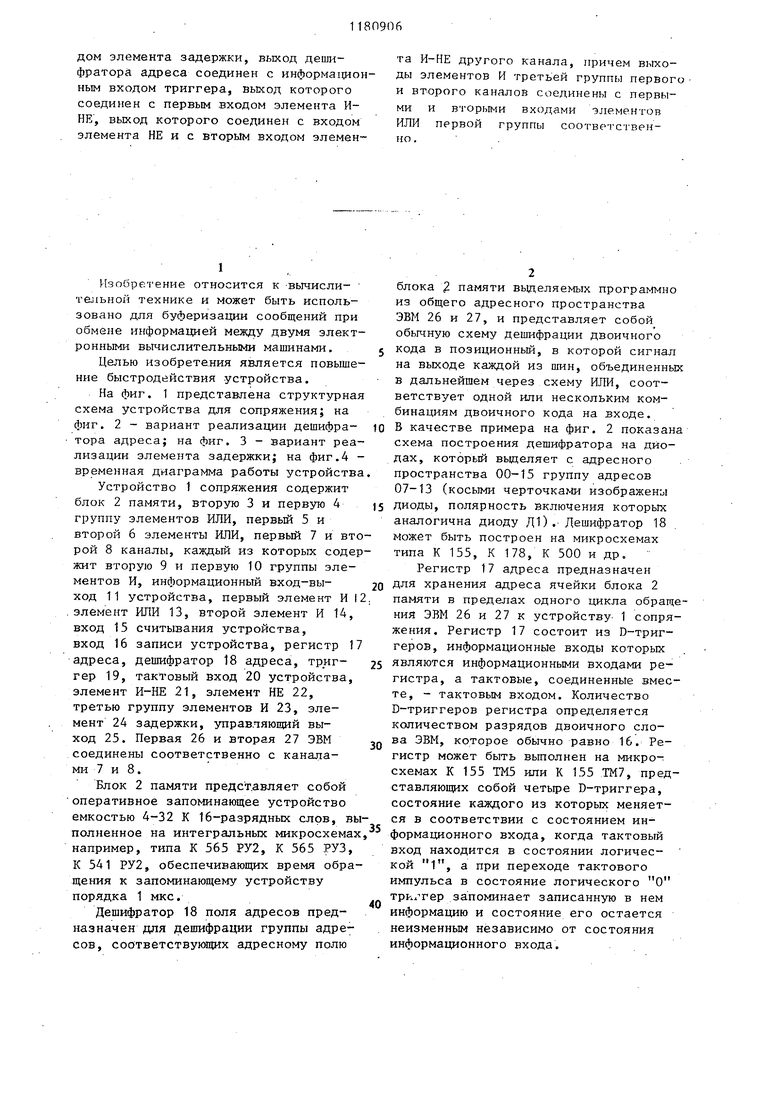

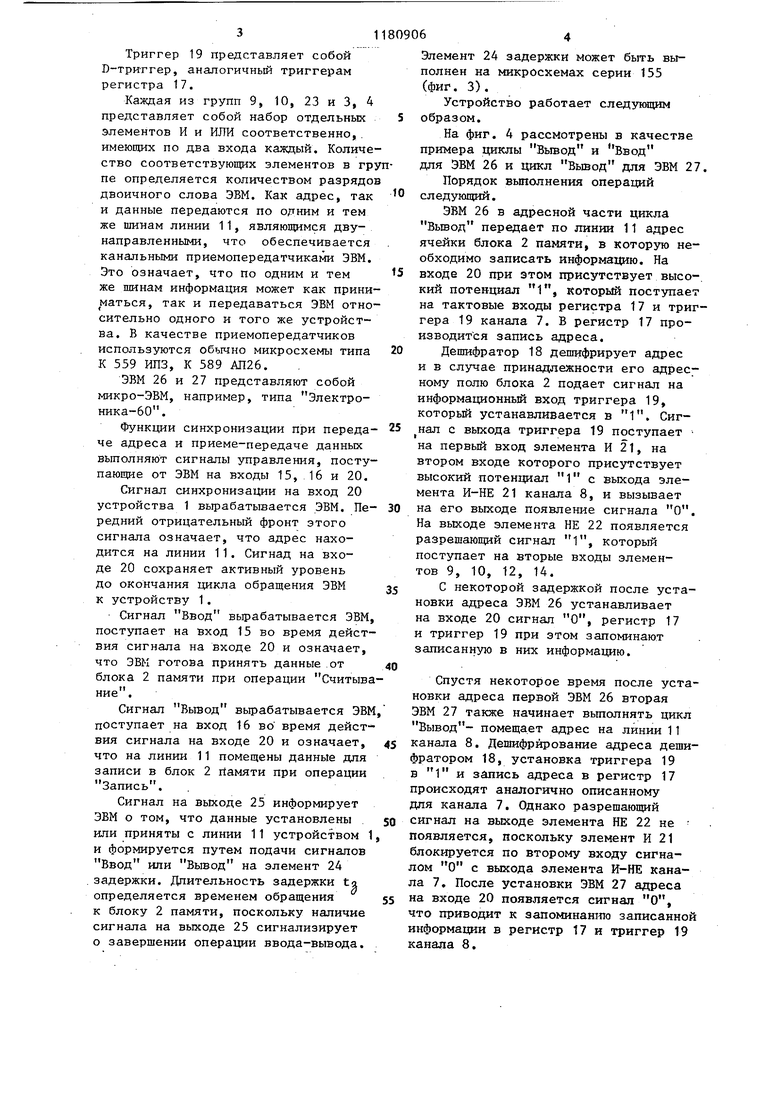

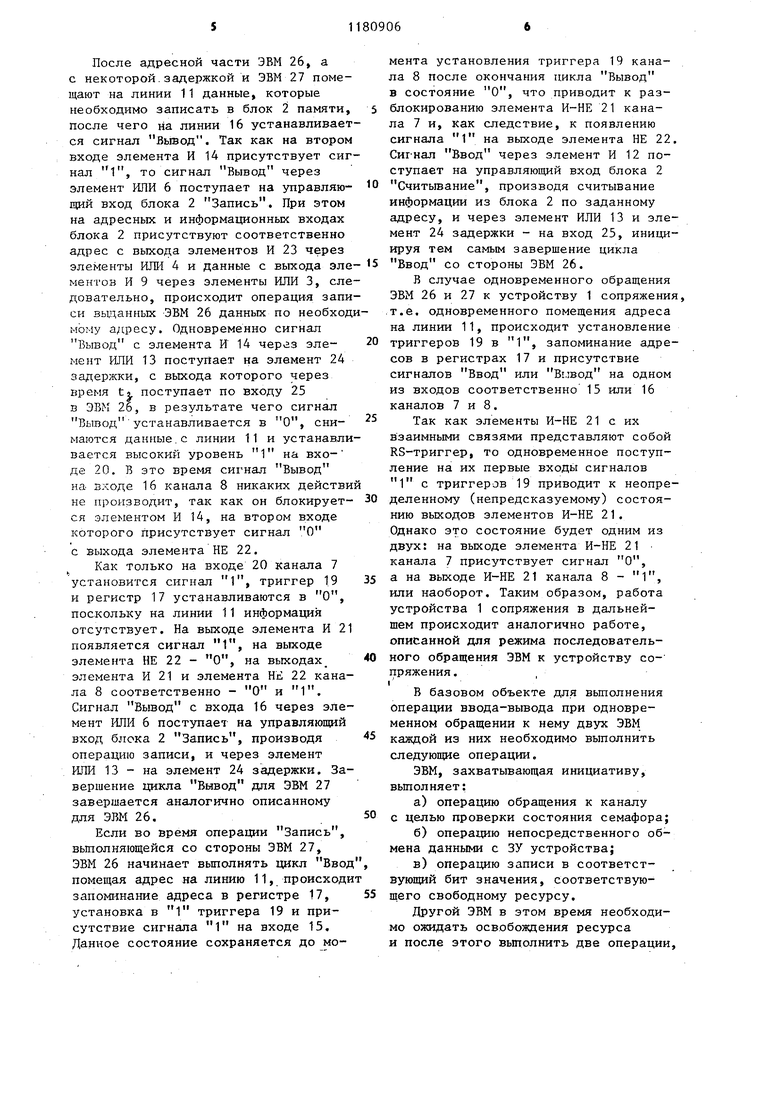

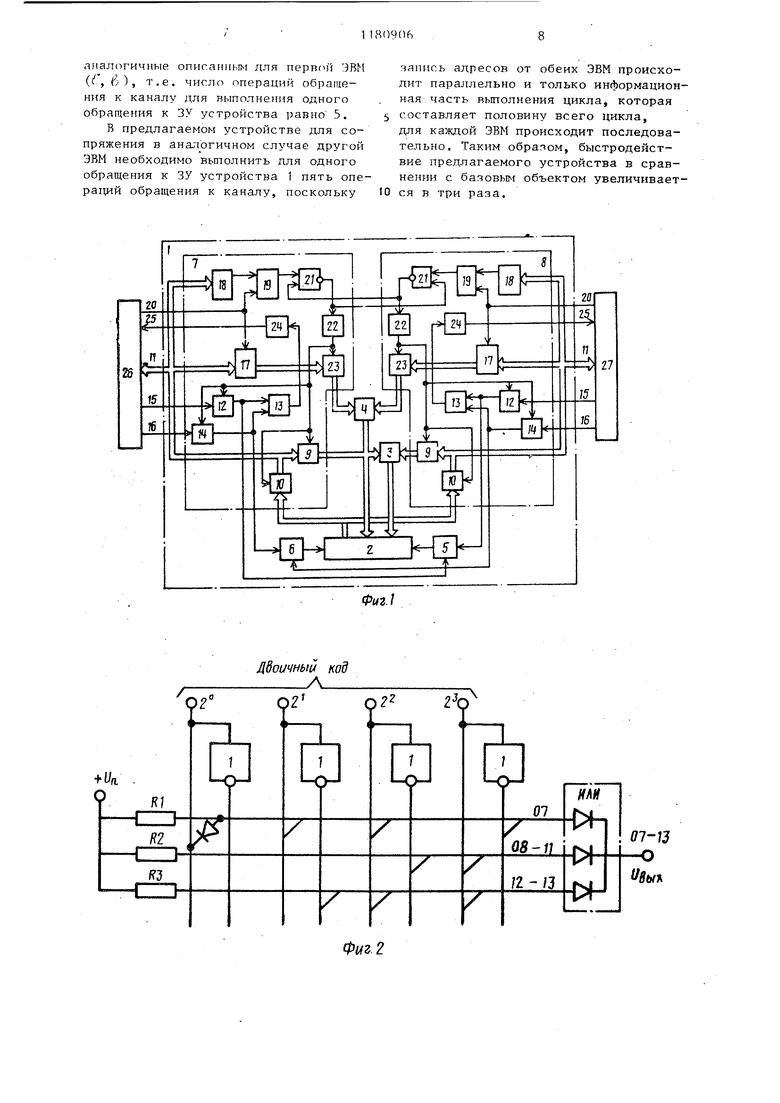

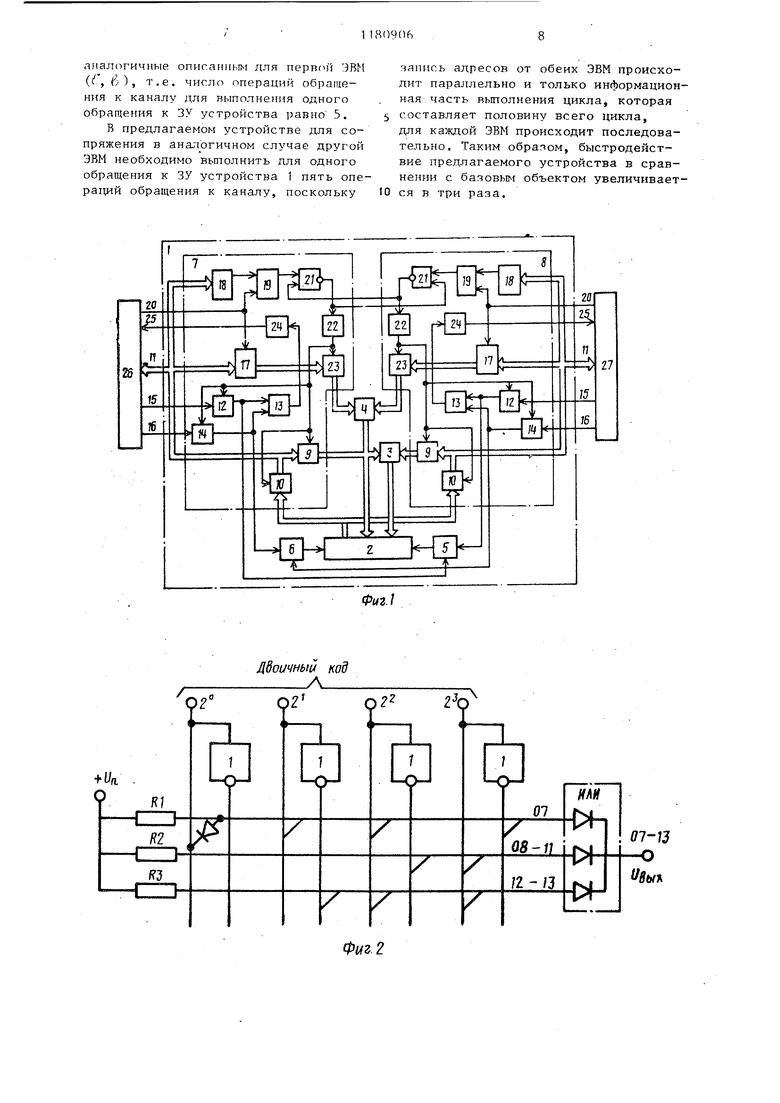

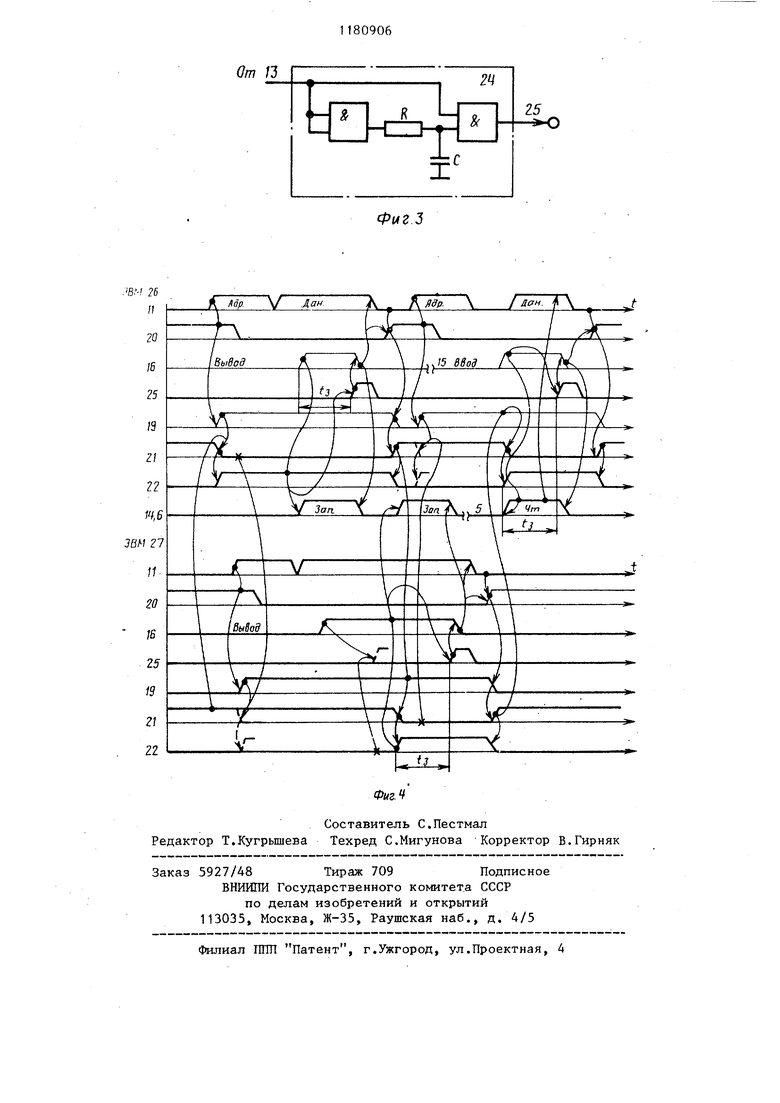

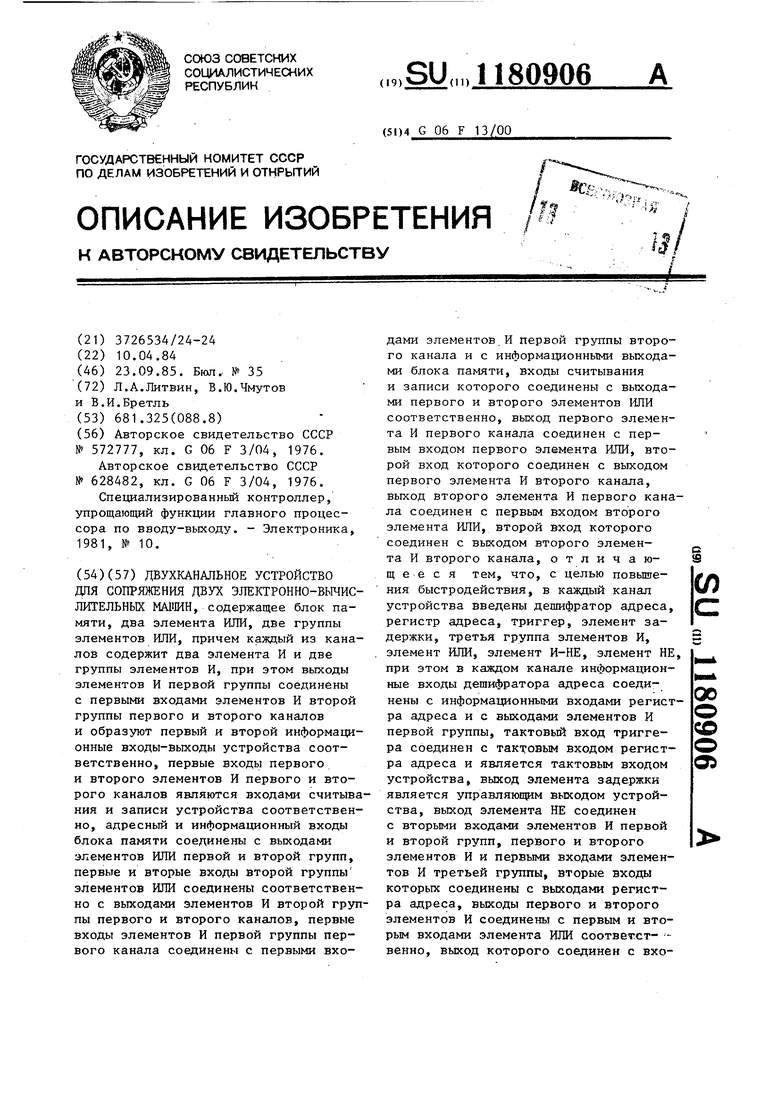

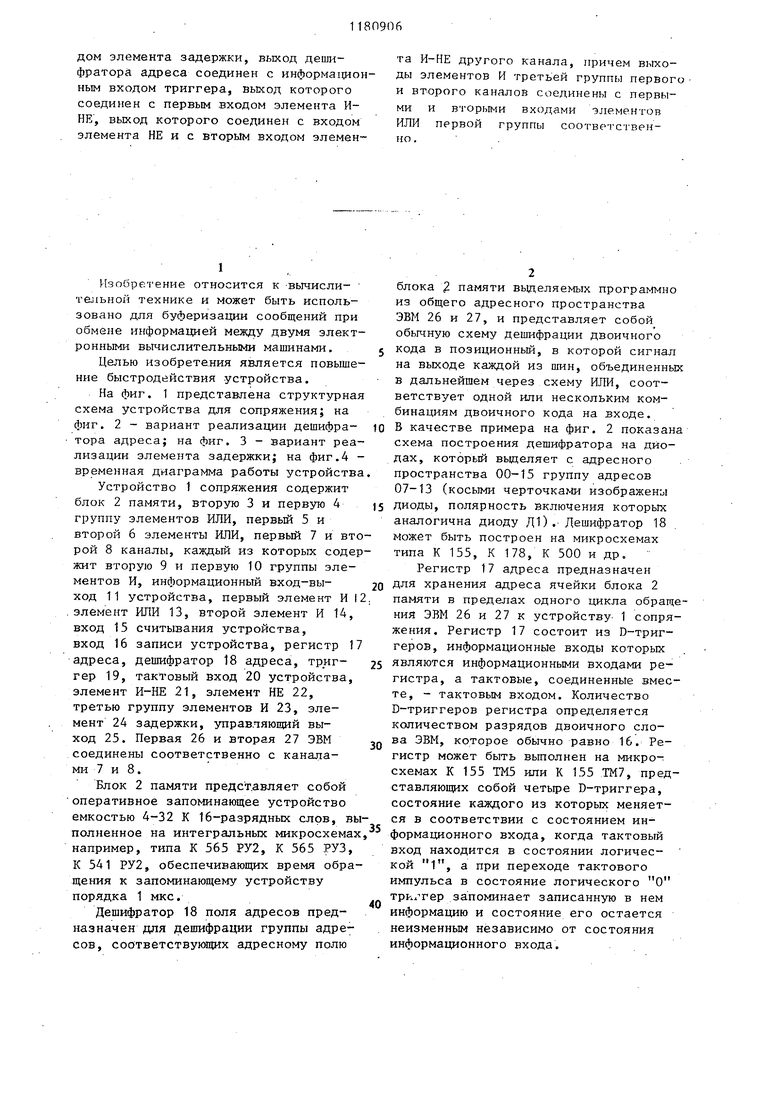

Изобретение относится к -вычислительной технике и может быть использовано для буферизации сообщений при обмене информацией между двумя элект ронными вычислительными машинами. Целью изобретения является повыше ние быстродействия устройства. На фиг. 1 представлена структурна схема устройства для сопряжения; на фиг. 2 - вариант реализации дешифратора адреса; на фиг. 3 - вариант реа лизации элемента задержки; на фиг.4 временная диаграмма работы устройств Устройство 1 сопряжения содержит блок 2 памяти, вторую 3 и первую 4 группу элементов ИЛИ, первый 5 и второй 6 элементы ИЛИ, первый 7 и вт рой 8 каналы, каждый из которых соде жит вторую 9 и первую 10 группы элементов И, информационный вход-выход 11 устройства, первый элемент И элемент ИЛИ 13, второй элемент И 14, вход 15 считывания устройства, вход 16 записи устройства, регистр 1 адреса, дешифратор 18 адреса, триггер 19, тактовый вход 20 устройства, элемент И-НЕ 21, элемент НЕ 22, третью группу элементов И 23, элемент 24 задержки, управляющий выход 25. Первая 26 и вторая 27 ЭВМ соединены соответственно с каналами 7 и 8 . Блок 2 памяти представляет собой оперативное запоминающее устройство емкостью 4-32 К 16-разрядных слов, в полненное на интегральных микросхема например, типа К 565 РУ2, К 565 РУЗ, К 541 РУ2, обеспечивающих время обра щения к запоминающему устройству порядка 1 МКС. Дешифратор 18 поля адресов предназначен для дешифрации группы адресов, соответствующих адресному полю блока памяти выделяемых программно из общего адресного пространства ЭВМ 26 и 27, и представляет собой обычную схему дешифрации двоичного кода в позиционный, в которой сигнал на выходе каждой из шин, объединенных в дальнейшем через схему ИЛИ, соответствует одной или нескольким комбинациям двоичного кода на входе. В качестве примера на фиг. 2 показана схема построения дешифратора на дИодах, который вьщеляет с адресного пространства 00-15 группу адресов 07-13 (косыми черточками изображены диоды, полярность включения которых аналогична диоду Д).- Дешифратор 18 может быть построен на микросхемах типа К 155, К 178, К 500 и др. Регистр 17 адреса предназначен для хранения адреса ячейки блока 2 памяти в пределах одного цикла обращения ЭВМ 26 и 27 к устройству- 1 сопряжения. Регистр 17 состоит из D-триггероз, информационные входы которых являются информационными входами регистра, а тактовые, соединенные вместе, - тактовым входом. Количество D-триггеров регистра определяется количеством разрядов двоичного слова ЭВМ, которое обычно равно 16. Регистр может быть вьшолнен на микросхемах К 155 ТМ5 или К 155 ТМ7, представляющих собой четыре D-триггера, состояние каждого из которых меняется в соответствии с состоянием информационного входа, когда тактовый вход находится в состоянии логической 1, а при переходе тактового импульса в состояние логического триггер запоминает записанную в нем информацию и состояние его остается неизменным независимо от состояния информационного входа. Триггер 19 представляет собой D-тритгер, аналогичный триггерам регистра 17. Каждая из групп 9, 10, 23 и 3, 4 представляет собой набор отдельных элементов И и ИЛИ соответственно,. имеющих по два входа каждый. Количе ство соответствующих элементов в гру пе определяется количеством разрядо двоичного слова ЭВМ. Как адрес, так и данные передаются по одним и тем же шинам линии 11, являющимся двунаправленными, что обеспечивается канальными приемопередатчиками ЭВМ. Это означает, что по одним и тем же пинам информация может как прини маться, так и передаваться ЭВМ отно сительно одного и того же устройства. В качестве приемопередатчиков используются обычно микросхемы типа К 559 ИПЗ, К 589 АП26. ЭВМ 26 и 27 представляют собой микро-ЭВМ, например, типа Электроника-60. Функции синхронизации при передаче адреса и приеме-передаче данных выполняют сигналы управления, поступающие от ЭВМ на входы 15, 16 и 20. Сигнал синхронизации на вход 20 устройства 1 вырабатывается ЭВМ. Передний отрицательный фронт этого сигнала означает, что адрес находится на линии 11. Сигнад на входе 20 сохраняет активный уровень до окончания цикла обращения ЭВМ к устройству 1. Сигнал Ввод вырабатывается ЭВМ поступает на вход 15 во время действия сигнала на входе 20 и означает, что ЭВМ готова принять данные от блока 2 памяти при операции Считыва ние. Сигнал Вывод вырабатывается ЭВМ поступает на вход 16 во время действия сигнала на входе 20 и означает, что на линии 11 помещены данные для записи в блок 2 йамяти при операции Запись. Сигнал на выходе 25 информирует ЭВМ о том, что данные установлены или приняты с линии 11 устройством и формируется путем подачи сигналов Ввод или Вывод на элемент 24 задержки. Длительность задержки ta определяется временем обращения к блоку 2 памяти, поскольку наличие сигнала на выходе 25 сигнализирует о завершении операции ввода-вывода. 1 64 Элемент 24 задержки может быть выполнен на микросхемах серии 155 (фиг. 3). Устройство работает следлощим образом. На фиг. 4 рассмотрены в качестве примера циклы Вьгеод и Ввод для ЭВМ 26 и цикл Вьшод для ЭВМ 27. Порядок выполнения операций следующий. ЭВМ 26 в адресной части цикла Вьшод передает по линии 11 адрес ячейки блока 2 памяти, в которую необходимо записать информацию. На входе 20 при этом присутствует высо-, кий потенциал 1, который поступает на тактовые входы регистра 17 и триггера 19 канала 7. В регистр 17 производится запись адреса. Дешифратор 18 дешифрирует адрес и в случае принадлежности его адресному полю блока 2 подает сигнал на информационный вход триггера 19, который устанавливается в 1. с выхода триггера 19 поступает на первый вход элемента И 21, на втором входе которого присутствует высокий потенциал 1 с выхода элемента И-НЕ 21 канала 8, и вызывает на его выходе появление сигнала О. На выходе элемента НЕ 22 появляется разрешающий сигнал 1, который поступает на вторые входы элементов 9, 10, 12, 14. С некоторой задержкой после установки адреса ЭВМ 26 устанавливает на входе 20 сигнал О, регистр 17 и триггер 19 при этом запоминают записанную в них информацию. Спустя некоторое время после установки адреса первой ЭВМ 26 вторая ЭВМ 27 также начинает вьшолнять цикл Вывод - помещает адрес на линии 11 анала 8. Дешифрирование адреса деширатором 18, установка триггера 19 1 и зались адреса в регистр 17 роисходят аналогично описанному ля канала 7. Однако разрешающий сигнал на выходе элемента НЕ 22 не оявляется, поскольку элемент И 21 блокируется по второму входу сигнаом О с выхода элемента И-НЕ канаа 7. После установки ЭВМ 27 адреса а входе 20 появляется сигнал О, то приводит к запоминанию записанной нформации в регистр 17 и триггер 19 анала 8. После адресной части ЭВМ 26, а с некоторой.задержкой и ЭВМ 27 помещают на линии 11 данные, которые необходимо записать в блок 2 памяти после чего на линии 16 устанавливает ся сигнал Вьгоод. Так как на втором входе элемента И 14 присутствует сиг нал 1, то сигнал Вывод через элемент ИЛИ 6 поступает на управляющий вход блока 2 Запись. При этом на адресных и информационных входах блока 2 присутствуют соответственно адрес с выхода элементов И 23 через элементы ИЛИ 4 и данные с выхода эле ментов И 9 через элементы ИЛИ 3, сле довательно, происходит операция запи си выданных ЭВМ 26 данных по необход мому адресу. Одновременно сигнал Вывод с элемента И 14 чергз элемент ИЛИ 13 поступает на элемент 24 задержки, с выхода которого через время tj. поступает по входу 25 в ЭВМ 26, в результате чего сигнал Вывод устанавливается в О, снимаются данные.с линии 11 и устанавли вается высокий уровень 1 на входа 20. В это время сигнал Вывод на входе 16 канала 8 никаких действи не производит, так как он блокируется элементом И 14, на втором входе которого присутствует сигнал О с выхода элемента НЕ 22. Как только на входе 20 канала 7 установится сигнал 1, триггер 19 и регистр 17 устанавливаются в О, поскольку на линии 11 информация отсутствует. На выходе элемента И 2 появляется сигнал 1 , на выходе элемента НЕ 22 - О, на выходах элемента И 21 и элемента Нь 22 канала 8 соответственно - О Сигнал Вывод с входа 16 через эле мент ИЛИ 6 постзшает на управляющий вход блока 2 Запись, производя операцию записи, и через элемент ИЛИ 13 - на элемент 24 задержки. За вершение цикла Вывод для ЭВМ 27 завершается аналогично описанному для ЭВМ 26.. Если во время операции Запись, вьтолняющейся со стороны ЭВМ 27, ЭВМ 26 начинает выполнять цикл Ввод помещая адрес на линию 11, происходи запоминание адреса в регистре 17, установка в 1 триггера 19 и присутствие сигнала 1 на входе 15. Данное состояние сохраняется до момента установления триггера 19 канала 8 после окончания цикла Вывод в состояние О, что приводит к разблокированию элемента И-НЕ 21 канала 7 и, как следствие, к появлению сигнала 1 на выходе элемента НЕ 22. Сигнал Ввод через элемент И 12 поступает на управляющий вход блока 2 Считьгоание, производя считывание информации из блока 2 по заданному адресу, и через элемент ИЛИ 13 и элемент 24 задержки - на вход 25, инициируя тем самым завершение цикла Ввод со стороны ЭВМ 26. В случае одновременного обращения ЭВМ 26 и 27 к устройству 1 сопряжения, т.е. одновременного помещения адреса на линии 11, происходит установление триггеров 19 в 1, запоминание адресов в регистрах 17 и присутствие сигналов Ввод или Вмвод на одном из входов соответственно 15 или 16 каналов 7 и 8. Так как элементы И-НЕ 21 с их взаимными связями представляют собой RS-триггер, то одновременное поступление на их первые входы сигналов 1 с триггеров 19 приводит к неопределенному (непредсказуемому) состоянию выходов элементов И-НЕ 21. Однако это состояние будет одним из двух: на выходе элемента И-НЕ 21 канала 7 присутствует сигнал О, а на выходе И-НЕ 21 канала 8 - 1, или наоборот. Таким образом, работа устройства 1 сопряжения в дальнейшем происходит аналогично работе, описанной для режима последовательного обращения ЭВМ к устройству сопряжения. I В базовом объекте для выполнения операции ввода-вывода при одновременном обращении к нему двух ЭВМ каждой из них необходимо выполнить следующие операции. ЭВМ, захватывающая инициативу, вьшолняет: а)операцию обращения к каналу с целью проверки состояния семафора; б)операцию непосредственного обмена данными с ЗУ устройства; в)операцию записи в соответствующий бит значения, соответствуюш.его свободному ресурсу. Другой ЭВМ в этом время необходимо ожидать освобождения ресурса и после этого вьтолнить две операции.

лналгиичные описанным для перпсч ЭВМ ( , 6 ) , т.е. число операций обращения к каналу для выполне ия одного обрагце П1Я к ЗУ устройства равно 5.

В предлагаемом устройстве для сопряжения в аналогичном случае другой ЭВМ необходимо вьтолнить для одного обращения к ЗУ устройства 1 пять опера1щй обращения к каналу, поскольку

запись адресов от обеих ЭВМ происходит параллельно и только информационная часть вьтолнения цикла, которая

5 составляет половину всего цикла, для каждой ЭВМ происходит последовательно. Таким обраяом, быстродействие предлагаемого устройства в сравнении с базовым объектом увеличивается в три раза.

Дбоичны1 код У

+

О

IL

Ж

Фиг 2

| Устройство управления для сопряжения вычислительных машин | 1975 |

|

SU572777A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения | 1975 |

|

SU628482A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Специализированньй контроллер, упрощаюпщй функции главного процессора по вводу-выходу | |||

| - Электроника, 1981, № 10. | |||

Авторы

Даты

1985-09-23—Публикация

1984-04-10—Подача