1

(21 ) 4292943/24-24

(22)03.08.87

(46) 30.08.90, Бюл. № 32

(72) Н.В.Шмарук, А.И.Подгорский,

М.Г.Дайновский, С.А.Муравьев

и А.В.Шачок

(53)681.326.7 (088.8)

(56 ) Авторское свидетельство СССР №1174944, кл. G 06 F 15/46, 1983.

Авторское свидетельство СССР № 117934, кл. G 06 F 11/00, 1984.

(54)СИГНАТУРНЫЙ АНАЛИЗАТОР

(57) Изобретение относится к вычислительной технике и может использоваться zyiH контроля-и диагностирования дискретных объектов, Целъ изобрете- .. НИН - повышение достоверности контроля. Сигнатурный анализатор-содержит элемент ИЛИ 1, шифратор 2, переключатель 3, блок 4 переключателей, блок 5 сравнения, элемент И 6, формироваг тель 7 сигнатур и блок 8 индикации. Анализатор позволяет блокировать вли- . яние цепей обратной связи при поиске неисправных элементов объекта диагностирования, 2 и-п..

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1985 |

|

SU1298771A2 |

| Сигнатурный анализатор для поиска перемежающихся неисправностей | 1986 |

|

SU1495799A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

| Сигнатурный анализатор | 1985 |

|

SU1363210A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1987 |

|

SU1562864A1 |

| Сигнатурный анализатор | 1982 |

|

SU1108452A1 |

| Сигнатурный анализатор | 1985 |

|

SU1270760A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1985 |

|

SU1302220A2 |

| Сигнатурный анализатор | 1987 |

|

SU1434437A1 |

| Сигнатурный анализатор | 1986 |

|

SU1388869A1 |

Изобретение относится к вычислительной технике и может использоваться для контроля и диагностирования дискретных объектов. Цель изобретения - повышение достоверности контроля. Сигнатурный анализатор содержит элемент ИЛИ 1, шифратор 2, переключатель 3, блок 4 переключателей, блок 5 сравнения, элемент И 6, формирователь 7 сигнатур, блок 8 индикации. Анализатор позволяет блокировать влияние цепей обратной связи при поиске неисправных элементов объекта диагностирования. 2 ил.

РФ

фиг 1

ИзоОретение относится к вычислительной техннке и предназначено для поиска неисправностей в аппаратных средствах цифровой вычислительной техники, в том числе для анализа выходных послецовательностей при тестовом контроле цифровых узлов ЭВМ,

Цель изобретения - повышение достоверности контроля.

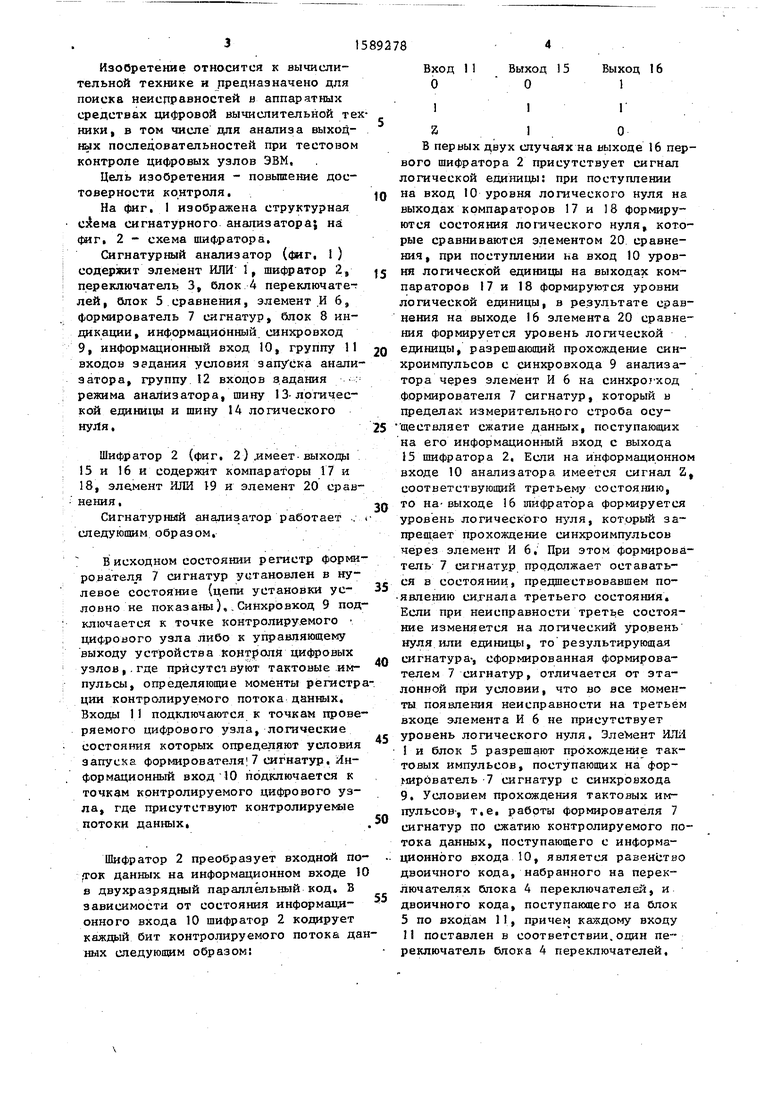

На фиг, 1 изображена структурН(1я сигнатурного анализатора; ни фиг, 2 - схема шифратора.

Сигнатурный анализатор (фиг, 1 ) содержит элемент ИЛИ 1, шифратор 2, переключатель 3, блок 4 переключате-г лей, блок 5 сравнения, элемент .И 6, формирователь 7 сигнатур, блок 8 индикации, информационный синхровход 9, информационный вход 10, группу 11 входов задания условия запуска ан.али- затора, группу 12 входов задания : режима анализатора, шину 13-ло1 ичес- кой единицы и шину 14 логического нуля,

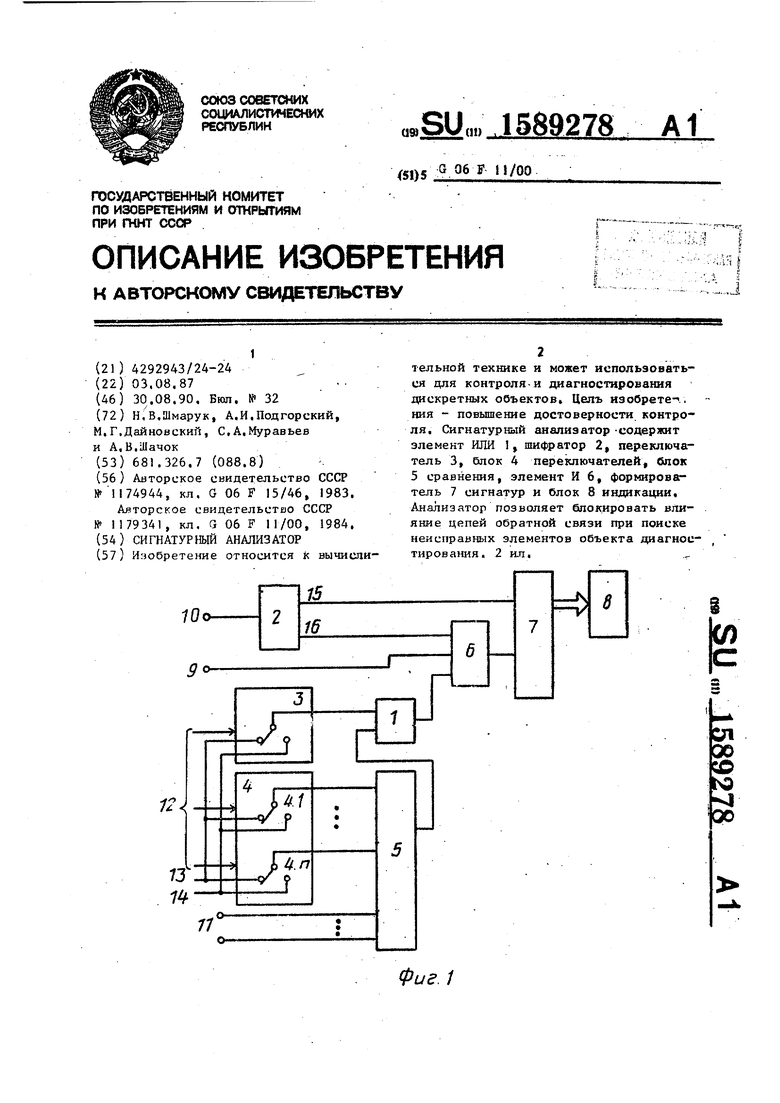

Шифратор 2 (фиг, 2) лмеет-выхода 15 и 16 и содержит компараторы 17 и 18, элемент ИЛИ 19 и элемент 20 сравнения.

Сигнатурный анализатор работает : следующим образом.

7 В исходном состоянии регистр формирователя 7 сигнатур установлен в нулевое состояние (цепи установки ус- ловно не показаны),,Синхровход 9 подключается к точке контролируемого цифрового узла либо к управляющему выходу устройства контроля цифровых узлов,. где прйсутс вуют тактовые .импульсы, определяющие моменты регистрации контролируемого потока данных. Входы 1 подключаются к точкам проверяемого цифрового узла, логические состояния которых определяют условия запуска формирователя 7 сигнатур. Информационный вход 10 подключается к точкам контролируемого цифрового узла, где присутствуют контролируемые потоки данных.

Шифратор 2 преобразует входной по- /ГОК данных на информационном входе 10 в двухразрядный параллельный код. В зависимости от состояния информаид- онного входа 10 шифратор 2 кодирует каждьй бит контролируемого потока данных следующим образом:

I1

Выход 15 О

1

Выход 16 1

Г

Q

0 5

0

0

5

5 0

Z1О

В первых двух случаях на выходе 16 первого шифратора 2 присутствует сигнал логической единицы: при поступлении на вход 10 уровня логического нуля на выходах компараторов 17 и 18 формируются состояния логического нуля, которые сравниваются элементом 20. сравнения, при поступлении на вход 10 уровня логической единищл на выходах компараторов 17 и 18 формируются уровни логической единицы, в результате сравнения на выходе 16 элемента 20 сравнения формируется уровень логической единицы, разрешающий прохождение синхроимпульсов с синхровхода 9 анализатора через элемент И 6 на синхрот ход ф.ормирователя 7 сигнатур, который в пределах измерительного строба осу- ществляет сжатие данных, поступающих на его информационный вход с выхода 15 шифратора 2, Если на информационном входе 10 анализатора имеется сигнал Z, соответствующий третьему состоянию, то на-выходе 16 шифратора формируется уровень логического , который запрещает прохождение синхроимпульсов через элемент И 6, При этом формирователь 7 сигнатур продолжает оставаться в состоянии, предшествовавшем по- явлению сигнала третьего состояния. Если при неисправности третье состояние изменяется на логический уро.вень нуля или единицы, то результирующая сигнатура-, сформированная формирователем 7 сигнатур, отличается от эталонной при условии, что во все моменты появления неисправности на третьем входе элемента И 6 не присутствует уровень логического нуля,

Iи блок 5 разрешают прохождение тактовых импульсов, поступающих на фор- шрбватель -7 сигнатур с синхроахода 9, Условием прохождения тактовых импульсов-, т,е. рабрты формирователя 7 сигнатур по сжатию контролируемого потока данных, поступающего с информационного входа 10, является равенство двоичного кода, набранного на переключателях блока 4 переключателей, и двоичного кода, поступающего на блок

5 по входам 11, причем каждому входу

IIпоставлен в соответствии.одан переключатель блока 4 переключателей.

Таким образом, сжатие контролируемого потока данных в формирователе 7 сигнатур происходит только в моменты времени, определяемые настройкой элемента ИЛИ и блока 5. Переключатель 3 предназначен для блокировки результата работы блока 5, При установке переключателя 3 в положение , что

соответствует уровню логической едани- д отличающийся тем, что, с

цы, на выходе элемента ШШ 1 формируется уровень логической единицы неза висимо от результата ср авнения кодов, поступающих с блока 4 переключателей и с входов 11, При этом сигнатурный анализатор может быть использован для снятия сигнатур в обычном режиме. При установке переключателя 3 в положе- ние О, что соответствует уровню логического нуля,-Логическое состояние выхода элемента ИЛИ 1 зависит от. результата сравнения кодов, поступающих на входа блока 5, Указанный режим позволяет блокировать влияние цепей обратной связи при поиске неисправных элементов.

Таким образом, предлагаем(эе устройство обеспечивает увеличение достоверности контроля за счет исключения ситуации, когда сигнатура исправного элемента, входящего в кольцо обратной связи, не соответствует эталонной из- за неисправности другого элемента кольца. Формула изобретения

Сигнатурньй анализатор, содержащий шифратор, элемент И, элемент ИЛИ,

15

20

целью повышения достоверности контро ля, он дополнительно содержит переключатель, блок переключателей и блок сравнения, выход которого соединен с первым входом элемента ИЛИ, второй вход и выход которого соединены соот ветственно с выходом переключателя и вторым входом элемента И, третий вход и выход которого соединены соот ветственно с вторым выходом шифратор и Тактовым входом формирователя сигнатур, первая группа входов блока сравнения подключена к группе выходо Блока переключателей, вторая группа входов блока- сравнения является груп пой входов задания условия запуска анализатора, первый информационный , вход переключателя и перв группа

информационных входов блока переклю- 30 чателей подключены к шине логаческой единицы, второй информационный вход .переключателя и вторая группа информа ционных входов блока переключателей подключены к шине логического нуля управляющий вход переключателя и гру па управляющих входов блока переключателей Являются входами задания режима анализатора.

25

35

формирователь сигнатур и блок индикации, ВХОФ1 которого подключены к выходам формирователя сигнатур, инфор- мацибнный вход которого подключен к - первому выходу шифратора, вход, которого является информационным входом анализатора, первый вход элемента И является синхровходом анализатора,

5

0

целью повышения достоверности контроля, он дополнительно содержит переключатель, блок переключателей и блок сравнения, выход которого соединен с первым входом элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом переключателя и вторым входом элемента И, третий вход и выход которого соединены соответственно с вторым выходом шифратора и Тактовым входом формирователя сигнатур, первая группа входов блока сравнения подключена к группе выходов Блока переключателей, вторая группа входов блока- сравнения является группой входов задания условия запуска анализатора, первый информационный , вход переключателя и перв группа

информационных входов блока переклю- 0 чателей подключены к шине логаческой единицы, второй информационный вход .переключателя и вторая группа информационных входов блока переключателей подключены к шине логического нуля управляющий вход переключателя и гругг па управляющих входов блока переключателей Являются входами задания режима анализатора.

5

5

IB

о-f7

IB

19

fS

20

16

Фuz.Z

Авторы

Даты

1990-08-30—Публикация

1987-08-03—Подача