.tamsAu/S

СО 00 30

00

05

со

Лиг.1

Пуск бмшнчв

Изобретение относится к вычислительной технике и может быть использовано для контроля и локализации неисправностей в цифровых схемах.

Целью изобретения является увеличение полноты контроля за счет обеспечения режима логического анализа.

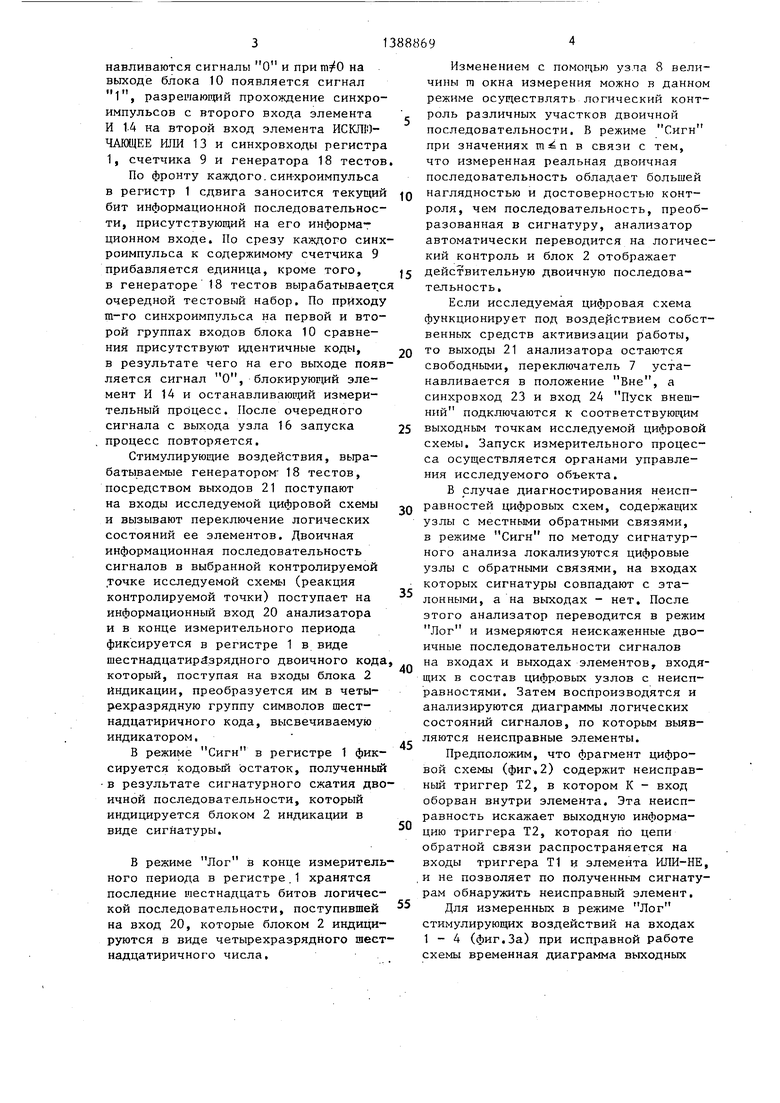

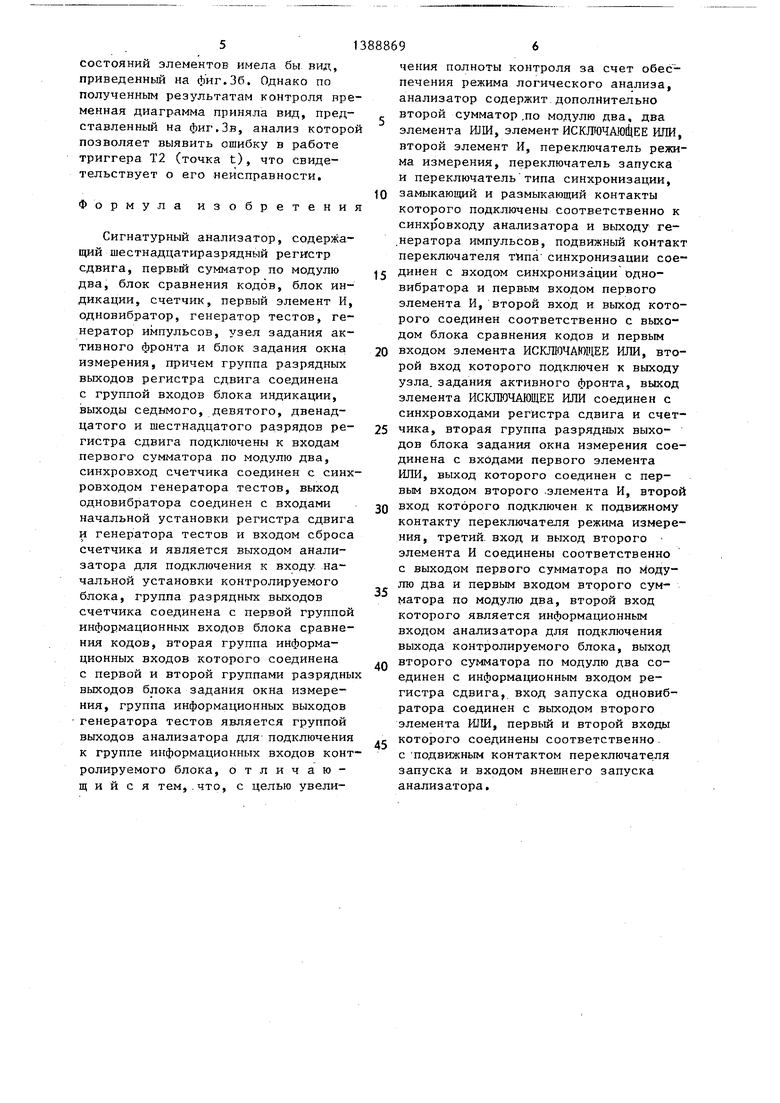

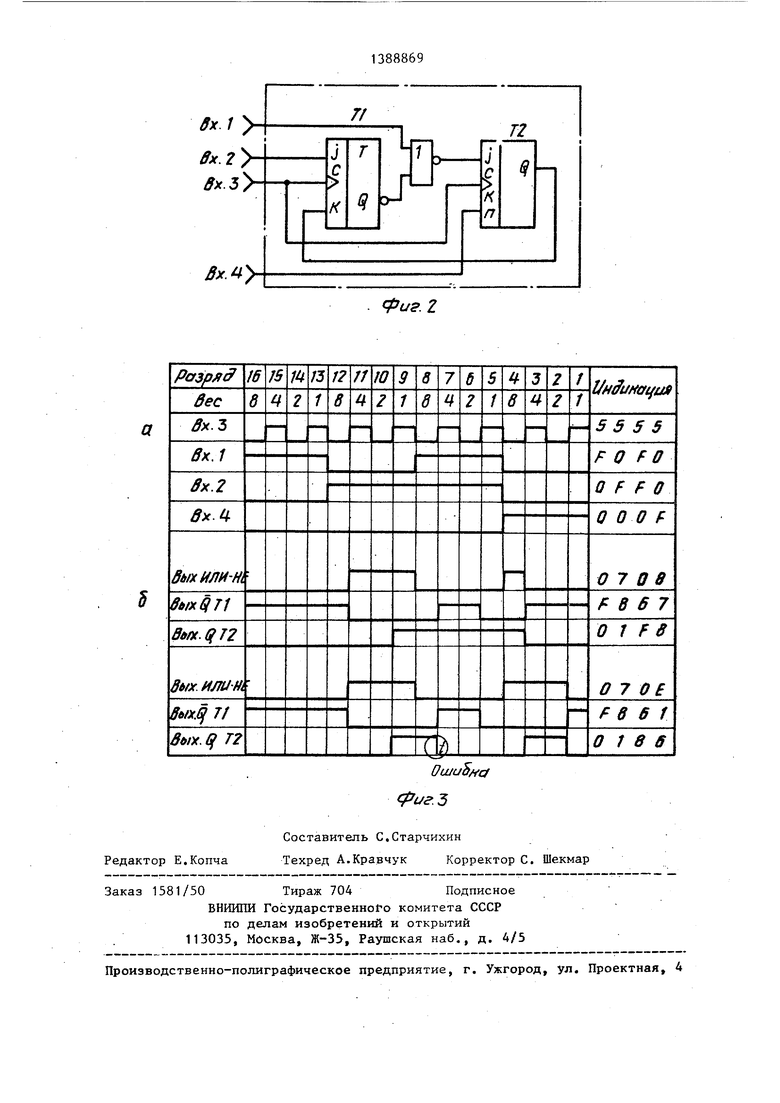

На фиг,1 изображена функциональная схема сигнатурного анализатора; ha фиг.2 - фрагмент проверяемой цифровой схемы с местной обратной связью для пояснения порядка работы с анализатором; на фиг.З - временные диаграммы стимулирующих воздействий на входах схемы, изображенной на фиг.2 (а); временные диаграммы выходных состояний элементов схемы, изображенной на фиг.2 при исправной ее работе (б); врем:енные диагра;ммы выходных состояний элементов схемы, изображенной на фиг.2 при неисправной работе триггера Т2 (в).

Сигнатурный анализатор (фиг.1) содержит шестнадцатиразрядный регистр 1 сдвига, блок 2 индикации, первый 3 и второй 4 сумматоры по модулю два узел 5 задания активного фронта, узел 6 задания режимов измерения, переключатель 7 типа синхронизации, блок 8 задания окна измерения, счетчик 9, блок 10 сравнения кодов, первый 11 и второй 12 элементы ИЛИ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 13, первый 14 и второй 15 элементы И, узел 16 запуска, одновибратор 17, генераторы тестов 18 и импульсов 19, информационный вход 20, группу выходов 21 для подключения входов контролируемого блока, выход 22 начальной установки, синхровход 23 и вход 24 Пуск внешний.

Анализатор работает следующим образом.

Перед началом контрольных измерений с помощью узла 5 выбирается активный фронт импульсов синхронизации по которому производится запись и обработка двоичной информации, поступающей на информационный вход регистра 1 сдвига. При этом сигнал О, устанавливаемый с выхода узла 5, на первом входе элемента ИСКШНАЮЩЕЕ ИЛ 13 обуславливает передачу неизмененных а сигнал 1 - инвертированных синхроимпульсов, поступающих на синхровход регистра 1..

При исследовании цифровых схем, у которых отсутствуют собственные

средства активизации функционирования , их входы подключаются к группе выходов 21 тестовых воздействий, а переключатель 7 типа синхронизации устанавливается в положение, соответствующее внутренней синхронизации. Вход 24 Пуск внешний в данном случае остается свободным.

Блоком 8 задания окна измерения

выбирается двоичное число, соответствующее числу тактов в цикле контрольного измерения и характеризующее длину m исследуемой цифровой последовательности.

Узлом 6 задания режима измерения устанавливается сигнатурное (Сигн.) или логическое (Лог) измерение цифровой последовательности, поступающей на информационньй вход 20.

В режиме Сигн на второй вход элемента И 15 поступает сигнал 1. Если блоком 8 выбрана величина ( - разрядность регистра 1), то

на одном из входов, а следовательно, и выходе элемента ИЛИ 11 появляется сигнал 1, обуславливающий сигнал 1 и на первом входе элемента И 15. При этом выход первого сумматора 3

по модулю два посредством элемента И 1 5 подключается к первому входу второго сумматора 4 и схема подготовлена к выполнению функции сигнатурного сжатия входной двоичной последовательности сигналов на информационном входе 20.

В режиме Лог узла 6 при задании блоком 8 значения на втором или первом входах соответственно устанавливается сигнал О, блокирующий элемент И 15 и отключаюпдай обратные связи регистра. 1 через сумматор 3 по модулю два. При сигнале О на первом входе сумматора 4 по модулю два с выхода 20 на информационный вход регистра 1 поступает неискаженная цифровая последовательность, Сигнал с выхода узла 16 через элемент ИЛИ 12 поступает на запускающий вход синхронного одновибрато- ра 17 и вызывает появление на его выходе одиночного синхронного импульса, который устанавливает в начальное состояние генератор 18 тестов и устанавливает в О регистр 1 и

счетчик 9.

При обнулении счетчика 9 на входах всех разрядов первой группы входов блока 10 сравнения кодов уста

навливаются сигналы О и при на выходе блока 10 появляется сигнал 1, разрешающий прохождение синхроимпульсов с второго входа элемента И 14 на второй вход элемента ИСКЛЮЧАЮЩЕЕ ШШ 13 и синхровходы регистра 1, счетчика 9 и генератора 18 тестов

По фронту каждого, син-хроимпульса в регистр 1 сдвига заносится текущий бит информационной последовательности, присутствующий на его информационном входе. По срезу каждого синхроимпульса к содержимому счетчика 9 прибавляется единица, кроме того, в генераторе 18 тестов вырабатываетс очередной тестовый набор. По приходу т-го синхроимпульса на первой и второй группах входов блока 10 сравнения присутствуют идентичные коды, в результате чего на его выходе появляется сигнал О, блокирующий элемент И 14 и останавливаюи:(ий измерительный процесс. После очередного сигнала с выхода узла 16 запуска процесс повторяется.

Стимулирующие воздействия, вырабатываемые генератором 18 тестов, посредством выходов 21 поступают на входы исследуемой цифровой схемы и вызывают переключение логических состояний ее элементов. Двоичная информационная последовательность сигналов в выбранной контролируемой точке исследуемой схемы (реакция контролируемой точки) поступает на информационный вход 20 анализатора и в конце измерительного периода фиксируется в регистре 1 в виде шестнадцатиразрядного двоичного кода который, поступая на входы блока 2 индикации, преобразуется им в четырехразрядную группу символов шестнадцатиричного кода, высвечиваемую индикатором,

В режиме Сиги в регистре 1 фиксируется кодовый остаток, полученньй в результате сигнатурного сжатия двоичной последовательности, который индицируется блоком 2 индикации в виде сигнатуры.

В режиме Лог в конце измерительного периода в регистре.1 хранятся последние шестнадцать битов логической последовательности, поступившей на вход 20, которые блоком 2 индицируются в виде четырехразрядного шестнадцатиричного числа.

0

5

0

5

0

5

0

5

0

Изменением с помощью узла 8 величины ш окна измерения можно в данном режиме осуществлять логический контроль различных участков двоичной последовательности. В режиме Сигн при значениях m п в связи с тем, что измеренная реальная двоичная последовательность обладает большей наглядностью и достоверностью контроля, чем последовательность, преобразованная в сигнатуру, анализатор автоматически переводится на логический контроль и блок 2 отображает действительную двоичную последовательность.

Если исследуемая цифровая схема функционирует под воздействием собственных средств активизации работы, то выходы 21 анализатора остаются свободными, переключатель 7 устанавливается в положение Вне, а синхровход 23 и вход 24 Пуск внешний подключаются к соответствующим выходным точкам исследуемой цифровой схемы. Запуск измерительного процесса осуществляется органами управления исследуемого обьекта.

В случае диагностирования неисправностей цифровых схем, содержапщх узлы с местными обратными связями, в режиме Сигн по методу сигнатурного анализа локализуются цифровые узлы с обратными связями, на входах которых сигнатуры совпадают с эталонными, а на выходах - нет. После этого анализатор переводится в режим Лог и измеряются неискаженные двоичные последовательности сигналов на входах и выходах элементов, входящих в состав цифровых узлов с неисправностями. Затем воспроизводятся и анализируются диаграммы логических состояний сигналов, по которым выявляются неисправные элементы.

Предположим, что фрагмент цифровой схемы (фиг,2) содержит неисправный триггер Т2, в котором К - вход оборван внутри элемента. Эта неисправность искажает выходную информацию триггера Т2, которая по цепи обратной связи распространяется на входы триггера Т1 и элемента ИЛИ-НЕ, ,и не позволяет по полученным сигнатурам обнаружить неисправный элемент.

Для измеренных в режиме Лог стимулирующих воздействий на входах 1 - 4 (фиг.За) при исправной работе схемы временная диаграмма выходных

5138886

состояний элементов имела бы вид, приведенньш на фиг.36. Однако по полученным результатам контроля временная диаграмма приняла вид, представленный на фиг.Зв, анализ которой позволяет выявить ошибку в работе триггера Т2 (точка t), что свидетельствует о его неисправности.

Формула изобретения

Сигнатурный анализатор, содержащий шестнадцатиразрядный регистр сдвига, первый сумматор по модулю два, блок сравнения кодов, блок индикации, счетчик, первый элемент И, одновибратор, генератор тестов, генератор импульсов, узел задания активного фронта и блок задания окна измерения, причем группа разрядных выходов регистра сдвига соединена с группой входов блока индикации, выходы седьмого, девятого, двенадцатого и шестнадцатого разрядов регистра сдвига подключены к входам первого сумматора по модулю два, синхровход счетчика соединен с синх ровходом генератора тестов, выход одновибратора соединен с входами начальной установки регистра сдвига и генератора тестов и входом сброса счетчика и является выходом анализатора для подключения к входу чальной установки контролируемого блока, группа разрядных выходов счетчика соединена с первой группой информационных входов блока сравнения кодов, вторая группа информационных входов которого соединена с первой и второй группами разрядны выходов блока задания окна измерения, группа информационных выходов генератора тестов является группой выходов анализатора для подключения к группе информационных входов контролируемого блока, отличающийся тем,.что, с целью увеличения полноты контроля за счет обеспечения режима логического анализа, анализатор содержит дополнительно второй сумматор,по модулю два, два элемента ШШ, элемент HCKJTO4AJOdiEE ИЛИ, второй элемент И, переключатель режима измерения, переключатель запуска и переключатель типа синхронизации,

замыкающий и размыкающий контакты которого подключены соответственно к синхровходу анализатора и выходу генератора импульсов, подвижный контакт переключателя типа синхронизации соединен с входом синхронизации одно- вибратора и первым входом первого элемента И, второй вход и выход которого соединен соответственно с выходом блока сравнения кодов и первым

входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого подключен к выходу узла, задания активного фронта, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с синхровходами регистра сдвига и счетчика, вторая группа разрядных выходов блока задания окна измерения соединена с входами первого элемента ИЛИ, выход которого соединен с первым входом второго .элемента И, второй

вход которого подключен к подвижному контакту переключателя режима измерения, третий, вход и выход второго элемента И соединены соответственно с выходом первого сумматора по лю два и первым входом второго сумматора по модулю два, второй вход которого является информационным входом анализатора для подключения выхода контролируемого блока, выход второго сумматора по модулю два соединен с информационным входом регистра сдвига, вход запуска одновибратора соединен с выходом второго элемента ЮШ, первый и второй входы которого соединены соответственно с ПОДВИЖНЫМ контактом переключателя запуска и входом внешнего запуска анализатора.

ffx.i

ffx.2 x5

7/

72

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для локализации неисправностей | 1980 |

|

SU903888A1 |

| Многовходовый сигнатурный анализатор | 1986 |

|

SU1383362A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для контроля многовыходных цифровых узлов | 1982 |

|

SU1019454A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU978154A1 |

| Сигнатурный анализатор | 1984 |

|

SU1242957A1 |

| Устройство для контроля и диагностики цифровых блоков | 1986 |

|

SU1388871A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1343417A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1180902A1 |

Изобретение относится к вь мис- лительной технике и может быть использовано для контроля и локализации неисправностей в цифровых схемах. Целью изобретения является -увеличение полноты контроля за счет обеспечения режима логического анализа. Сигнатурный анализатор содержит шестнадцатиразрядный регистр сдвига 1, блок 2 индикации, первый 3 и второй 4 сумматоры по модулю два, узел 5 задания активного фронта, узел 6 задания режима измерения, переключатель 7 типа синхронизации, блок 8 задания окна измерения, счетчик 9, блок 10 сравнения кодов, первый 11 и второй 12 элементы ИЛИ, элемент ИСЮЮЧАРЗЩЕЕ ИЛИ 13, первый 14 и второй 15 элементы И, узел 16 запуска, одновибратор 17, генераторы тестов 18 и импульсов 19. В зависимости от величины заданного окна измерения анализатор автоматически перек- лючается из режима сигнатурного анализа в режим логического анализа, что позволяет, в частности, обеспечивать локализацию неисправностей в цифровых схемах с обратными связями. 3 ил. Ш СЛ

ffx.

фи. 2

| Электроника, 1977, № 5, с.23-33 | |||

| Устройство для локализации неисправностей | 1980 |

|

SU903888A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-04-15—Публикация

1986-09-17—Подача