. 1

(21)4486809/24-24

(22)20.06.88

(46) 30.08.90. Бюл. № 32 (70 Институт проблем моделирования в энергетике АН УССР и Специальное конструкторско-технологическое бюро средств моделирования с опытным производством Института проблем моделирования в энергетике АН УССР (72) В.П.Романцов, С.Я.Гильгурт, А.Ф.Новицкий и Л.П.Добрыдина (53) 681.335 (088.8) (56) Авторское свидетельство СССР 423132, кл. G 06 G 7/14, 1971. ; Авторское свидетельство СССР № 423133, кл. G 06 G 7/14, 1971.

(54) РАЗРЯДНО-АНАЛОГОЙЫЙ СУММАТОР (57) Изобретение относится к вычислительной технике, например к разрядно- аналоговым сумматорам и может быть использовано в качестве базового бло- .ка для синтеза матричных умножителей, функциональных преобразователей и других разрядно-аналоговых устройств. Целью изобретения является расширение функциональных возможностей раз- рядно-аналоговых сумматоров за счет умножения входных величин на дробные масштабные коэффициенты, что достигается введением аналого-разрядных преобразователей и организацией как переносов .из младших разрядов в стар

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой сумматор | 1986 |

|

SU1316006A1 |

| Разрядно-аналоговый сумматор | 1987 |

|

SU1548797A1 |

| Аналоговый интегратор | 1986 |

|

SU1339592A1 |

| Преобразователь координат | 1986 |

|

SU1328827A1 |

| Устройство для контроля экспоненциальных процессов | 1990 |

|

SU1732331A1 |

| Устройство для возведения в квадрат @ -разрядных чисел | 1984 |

|

SU1236469A2 |

| Устройство для моделирования случайных блужданий | 1981 |

|

SU999063A1 |

| Функциональный преобразователь | 1982 |

|

SU1049929A1 |

| Устройство для умножения | 1984 |

|

SU1256016A1 |

| Устройство для вычисления квадратного корня | 1988 |

|

SU1494004A1 |

Изобретение относится к вычислительной технике, например к разрядно- аналоговым сумматорам и может быть использовано в качестве базового блока для синтеза матыричных умножителей, функциональных преобразователей и другихы разрядно-аналоговых устройств. Целью изобретения является расширение функциональныых возможностей разрядно- аналоговых сумматоров за счет умножения входных величин на дробные масштабные коэффициенты, что достигается введением аналого- разрядных преобразователей и организаций как переносов из младших разрядов в старшие, так и заемов из старших разрядов в младшие. Устройство содержит N аналоговых сумматоров 1 (где N - количество разрядов), N аналого-разрядных преобразователей 2, M (где M - количество слагаемых) входных N-разрядных шин 3 и 4, вход 5 приема переноса младшего разряда, вход 6 заема старшего разряда, шину 7 положительного опорного напряжения, выходную N-разрядную шину 8, выход 9 заема младшего разряда, выход 10 переноса старшего разряда. Аналого-разрядный преобразователь содержит аналоговый инвертор 11, два аналого-цифровых преобразователя, два цифроаналоговых преобразователя, два усилителя разностного сигнала. 2 ил.

(Л

Л./

шие, так и заемов иэ старших разрядов в млад1аие. Устройство содержит п аналоговых сумматоров 1 (где п - количество разрядов),п гшалого-раз- рядных преобразователей 2, га (где m - количество слагаемых) входных п разрядных шин -3 и 4, вход 5 приема переноса мпадшего разряда, вход 6 заема старшего разряда, шину 7 полоИзобретение относится к вычислительной технике, в частности к гибридной вычислительной технике,, и может быть использовано в качестве базового блока для синтеза матричных умножителей, функциональных преобра- зователей и других разрядно-аналоговых устройств,

Цель изобретения - расширение функциональных возможностей устрой- ств-а за счет умножения входных вели- чин на дробные масштабные коэффициенты ,

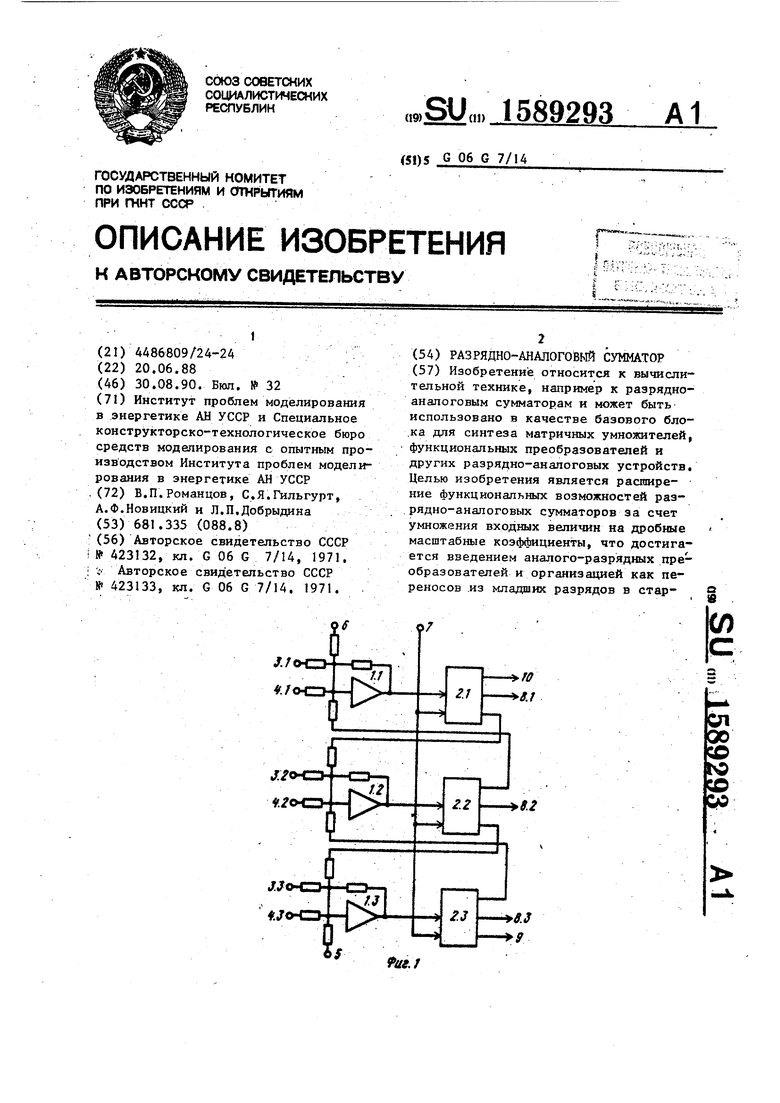

На фиг.1 приведена схема разрядно- аналогового сумматора для частного случая, когда количество разрядов

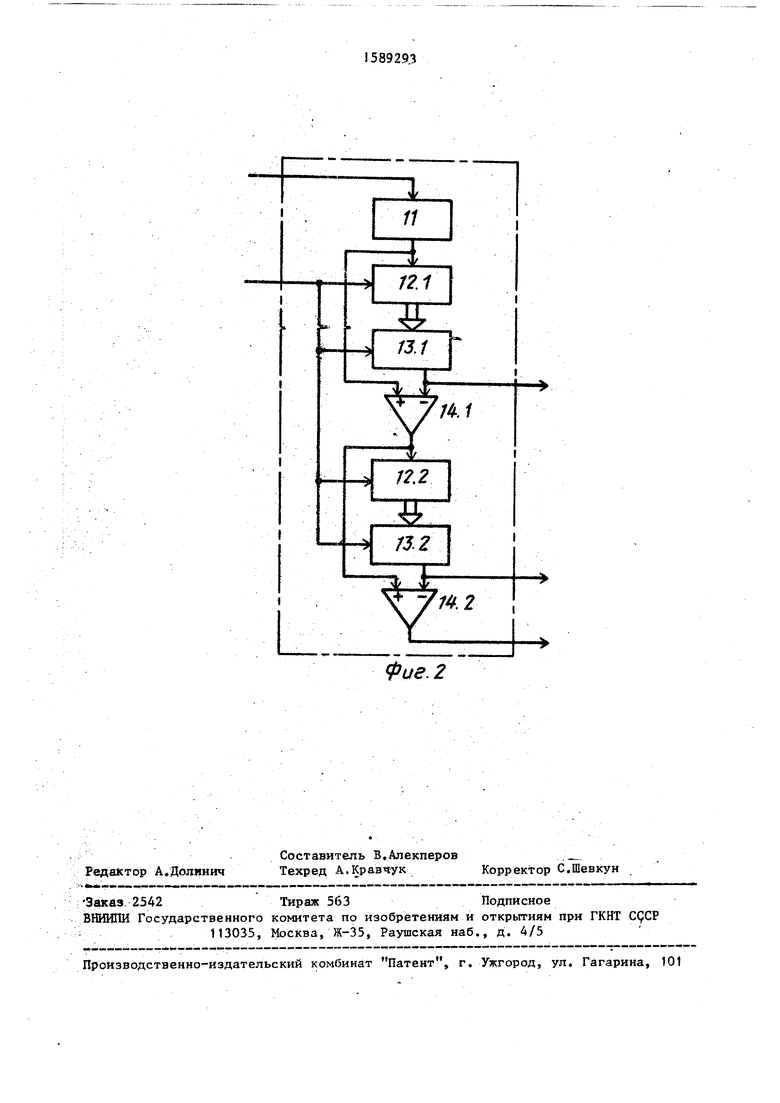

п 3, количество слагаемых та 2; на фиг, 2 вари ант выполнения анало- го-разрядного преобразователя.

Разрядно-аналоговый сумматор (фиг,1) содержит п ана-поговых сум- матороз 1.1, 1.2, 1.3 с (т+2) входами, п аналого-разрядных преобразователей 2,1, 2.2, 2,3,. га входных п-раз- рядных шин 3,1, 3.2, 3.3, 4.1, 4.2, 4.3, вход 5 приема переноса младшего разряда, вход 6 заема старшего разряда, шину 7 положительного опорного напряжения, выходную п разрядную шину 8, выход 9 заема младшего разряда, выход 10 переноса старшего разря- да.

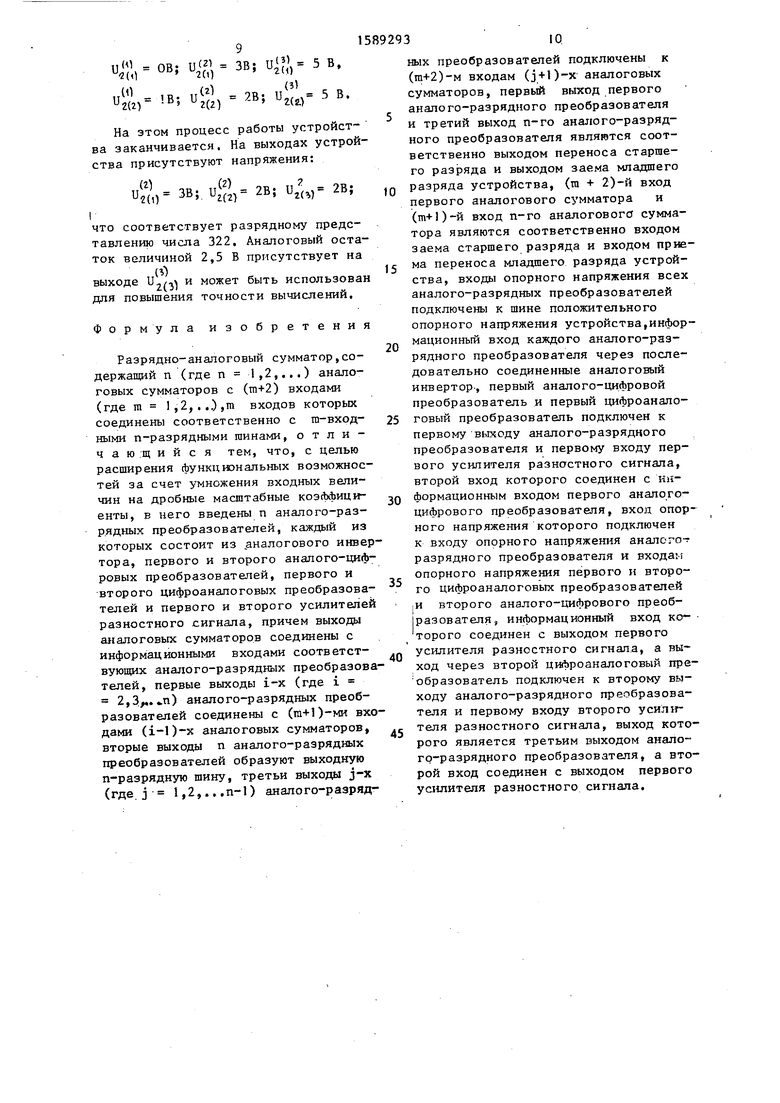

Аналого-разрядный преобразователь (фиг.2) содержит аналоговый инвертор 11, два аналого-1Щфровы(х преобразователя 12,1, 12.2, два цифроаналоговых преобразователя 13.1, 13,2, два усилителя 14.1 и 14.2 разностного сигнала,

Разрядность аналого-цифровых и ци роаналоговых преобразователей зависи от используемой системы счисле шя слдующим образом.

L ,

жительного опорного напряжения, выходную п-разрядную шину 8, выход 9 заема мпадшего разряда, выход 10 переноса старшего разряда, Анапого- разрядный преобразователь содержит аналоговый инвертор, два аналого-цифровых преобразоватепя, два цифроанало- говых преобразователя, два усилителя

разностного сигнала, 2 ил.

где L - разрядность преобразователей К - основание системы счисления;

оператор ближайшего целого, большего или равного исходному значению.

Устройство работает следуюшим образом.

При работе устройства в системе счисления с основанием, равным десяти, разрядность L преобразователей, входящих в состав аналого-разрядных преобразователей 2, равна четырем. Для удобства описания работы устройства предположим, что единице входного сигнала соответствует напряжение величиной 1В.

Тогда величина напряжения П,,подаваемо го на шину 7 положительного опорного напряжения устройства, должна быть равной 10В.

Разрядно-аналоговый сумматор выполняет операцию вида:

У

(1)

Представим (1) в разрядной форме

П

где у, X,, х, - разрядные векторы, формируемые следующем обр.

У у, x,i:K - x;,

.; . . ., п ,,(30

Ч

i-

где К - основание системы счисления

Рассмотрим изложенное на примере, когда , п 3, g, 3/4, g 1/4, X , 268, хг 485. Тогда в соответствии с О) результат операции должен быть

4

322,25.

Устройство работает по оледующе- му алгоритму:

а)операция округления М заклю - чающаяся в выделении в каждом разряде дробной части, умножении ее на величину К 10 и передаче результата

в соседний младший разряд;

б)операция переноса П аналогичная обычному переносу в цифровых сумматорах.

ким образом, имеем результат: 3

210

10 3

у 2- 10

.10

При необходимости дробная часть младшего разряда может сохраняться и использоваться в качестве дополнительного аналогового разряда. Ее значение лежит в непрерывном отрезке (О,...,К).

Величины сопротивлений резисторов во входных ветвях аналоговых сумматоров 1, ведущих ко входным шинам 3 и 4, выбираются обратно пропорциональными масштабным коэффициентам, на которые должны умножаться переменные X, и Xj. В данном примере они равны соответственно R/9 . 4R/3 и R/92. 4R. Величина сопро- тивления резисторов в цепях обратной связи сумматоров Г выбирается обратно пропорциональной основанию системы счисления К (R/IO).

Величина сопротивления резисторов во входных (т+1) - X и (т+2)-х ветвях аналоговых сумматоров 1,ведущих к выходам аналого-разрядных преобразователей 2, выбирается единич ной.

Тогда Ki) (

2(;-л

гДе и

и

2Ci + i)

),

(5)

5

0

и

Ui)

ъ()

(11

(г

и

i(iHV

,0) 2(140

нап1 яжение на выходе аналогового сумматора

11;

напряжение на i-ом разряде входной п-разряд- ной шины 31; напряжение на i-ом разряде входной п-разряд- ной шины 41; напряжение на третьем выходе (i-l)-ro аналого- разрядного преобразователя Й-);

напряжение на первом выходе (i+l)-ro аналого- разрядного преобразователя .

25

Из (5) следует

uui) -0.1 C-rU,() )С (О + U(-,+ и(,Ч,).

(6)

в начальный момент времени на п-разрядные шины 3 и 4 подаются входные сигналы, а именно: на вход 3.1 - напряжение 2Б; на вход 3,2- напряжение 6 В; на вход 3.3 - напряжение , 8 В; на вход 4.1 - напряжение 4 В; на вход 4.2 - напряжегше 8 В; на вход 4.3 - напряжение 5В.

На выходах аналоговых сумматоров появляются напряжения:

-0.1(-f- 2 + -0,25 В;

U(U) -о.И-|-б + -f

-h

+ 0+0)

+ с + 0) -0,65 В; 3

) -о,1(-

+ 0+0) -0,725 В.

1

4

8 + -7- 5 +

Эти напряжений подаются на входы аналого-разрядных преобразователей 2,

Рассмотрим подробнее работу аналого-разрядных преобразователей на примере второго разряда. Напряжение и -0,65 В инвертируется аналоговым инвертором 11 в напряжение:

U ) 0.65 В,

которое преобразубтся аналого-цифровым преобразователем 12,1 в код 0000(2), Этот код поступает на роаналоговый преобразователь 13.1 и преобразуется в напряжение Uj,« . О В. Это напряжение усипителем 14.1 разностного сигнала вычитается из выходного напряжения инвертора Цц и результат умножается на коэффициент К:

и

У

K(UU- ии,о„,)

10(0,65-0) 6,5 В.

(8)

Это напряжение преобразуется аналого-цифровым преобразователем 12,2 в код 0110(2), который подается на цифроаналоговый преобразователь 13.2 и преобразуется в напряжение Uugi,2 бВ. На выходе усилителя 14.2 разностного сигнала напряжение становится равным

K(Uy,- ицапг) 10(6,5-6) 5 В.

(9)

Таким образом, аналого-разрядный преобразователь 2,1 преобразует аналоговое напряжегтае и (, 1 -0,65 В в три разрядных напряжения:

4an, ltl ОВ;

(г) ицап гсг) 6BJ

и

га.)

5В,

Подставляя (8) в (9), получаем

киц К - Ui q +кицд„2+ ц

Используя (7) и (6) для , приходим к следующему соотношению:

Ч4Т 8 + «4(2)84 + %.) 2)

-ки,„„,+ 10 + ufi., + 0,1 ujj,) ,

(11)50

Согласно (II) сумма входных величин аналогового сумматора К2 раек-

ладывается на целую часть щюб- Л) лГ)

ную часть и

2(4)

и велюшну и

2(2)

ха

рактеризующую превышение основания системы счисления, Эти величины являются соответственно выходным напряжением данного разряда, напряжением заема и напряжением переноса.

Анало го-р.азрядные пр еобразователи 2.1 и 2.3 работают аналогичным образом. На их выходах появляются напряжения

и

W 2(iy

op; .-2В; и Д, 5В;

, OB; ujf,, 7В; U2% 2,5 В.

Напряжение заема Ujfil 5 Б поступает на (га+2)-й вход аналогового сумматора 1,2, напряжение заема )

5В поступает на (in+2)-ft вход аналогового сумматора 1.3. В результате на выходах этих сумматоров появляются напряжения

) -0,1 (-|-.6 4 -.. 8+5+

30

+ 0) -1,15 В;

. Т

5+5+0)

-1,225 В.

Эти напряжения преобразуются анало- го-разрядными преобразователями 2.2 35 и 2.3 в следующие сигналы:

и

(О 2(г1

(О 2(3)

1В| и(Л

(3)

1В; Ujtj)

0

1В; 2В; U.,,, ,(),

5В; 2,5В.

Напряжение переноса U2(2) 1 В поступает на (т+1)-й вход аналогового сумматора 1.1, напряжение переноса

2(9) поступает на (т+)-й вход аналогового сумматора 1.2. В результате на выходах этих сумматоров появляются напряжения:

-o,K-J-0,35 В,

2 -1- 4

4 + О +

-0,1(-|-.6 + , + 5+1)

- -1,25 В,

Эти напряжения преобразуются аналс- го-разрядными преобразователями 2,1 и 2,2 в следующие сигналы:

ОВ; U,

и

(3)

В; и

(г)

2(2)

2(1)

(

2В; и,(

5 В,

5 В,

На этом процесс работы устройства заканчивается. На выходах устройства присутствуют напряжения:

,(2)

ЗВ;. и ;, 2В; и,(,, 2В;

1

что соответствует разрядному представлению числа 322. Аналоговый остаток величиной 2,5 В присутствует на

выходе и может быть использован для повышения точности вычислений.

Формула изобретения

Разрядно-аналоговый сумматор,содержащий п (где п 1,2,...) аналоговых сумматоров с (т+2) входами (где га 1,2, ...),га входов которых соединены соответственно с га-входными п-разрядными шинами, о т л и - ч а ю.щ и и с я тем, что, с целью расширения функциональных возможностей за счет умножения входных величин на дробные масштабные коэффициенты, в него введены п аналого-раз- рядных преобразователей, каждый из которых состоит из аналогового инвертора, первого и второго аналого-цифровых преобразователей, первого и второго цифроанапоговых преобразователей и первого и второго усилителей разностного сигнала, причем выходы аналоговых сумматоров соединены с информационными входами соответствующих аналого-разрядных преобразователей, первые выходы i-x (где i 2,3/.. п) аналого-разрядных преобразователей соединены с (т+1)-ми входами (i-l)-x аналоговых сумматоров, вторые выходы п аналого-разрядных преобразователей образуют выходную п-разрядную шину, третьи выходы j-x (где j 1,2,...п-1) аналого-разряд10

15

йао8929310

ных преобразователей подключены к (т+2)-м входам (j+1)-x аналоговых сумматоров, первьА выход первого аналого-разрядного преобразователя и третий выход п-го аналого-разряд- ного преобразователя являются соответственно выходом переноса старшего разряда и выходом заема младшего разряда устройства, (та 2)-й вход первого аналогового сумматора и (т+)-й вход п-го аналогового сумматора являются соответственно входом заема старшего разряда и входом приема переноса младшего разряда устройства, входы опорного напряжения всех аналого-разрядных преобразователей подключены к шине положительного опорного напряжения устройства,информационный вход каждого аналого-раз- рядного преобразователя через последовательно соединенные аналоговый инвертор., первый аналого-цифровой преобразователь и первый цифроанало- 25 говый преобразователь подключен к первому выходу аналого-разрядного преобразователя и первому входу первого усилителя разнсгстного сигнала, второй вход которого соединен с OQ формационным входом первого аналого- цифрового преобразователя, вход опорного напряжения которого подключен к входу опорного напряжения аналогот разрядного преобразователя и входа опорного напряжения первого и второго цифроаналоговых преобразователей и второго аналого-цифрового преобразователя, информационный вход которого соединен с выходом первого усилителя разностного сигнала, а выход через второй цифроаналоговый преобразователь подключен к второму выходу аналого-разрядного преобразователя и первому входу второго усилителя разностного сигнала, выход которого является третьим выходом аналого-разрядного преобразователя, а второй вход соединен с выходом первого усилителя разностного сигнала.

35

40

45

фиг. 2

Авторы

Даты

1990-08-30—Публикация

1988-06-20—Подача