1

Изобретение относится к вычислительной технике и может быть применено в спецпроцессорах или в комплексе с цифровой вычислительной машиной для решения системы линейных и нелинейных дифференциальных уравнений функциональных зависимостей, например, в системах автоматического управления динамическими объектами или технологическими процессаьш.

Цель изобретения. повышение точности и расширение диапазона интегрируемого сигнала.

На фиг. 1 приведена схема интегратора для случая, когда количество разрядов на фиг. 2 - схема бло приема переносов; на фиг, 3 схема блока формирования переносов; на фиг. 4 - временные диаграммы, поясн Ющие работу интегратора.

Интегратор (фиг. 1) состоит из п цепей, где п - количество разрядов., каждая из которых содержит интегриру ющий усилитель 1 с входом обнуления 2, сумматор 4 приема переноса, блок 5 формирования переноса, вход 6 интегратора, выход 7 интегратора, шину 8 эталонного напряжения переноса, шину 9 эталонного напряжения, вход 10 переноса младшего разряда и выход 11 переноса старшего разряда.

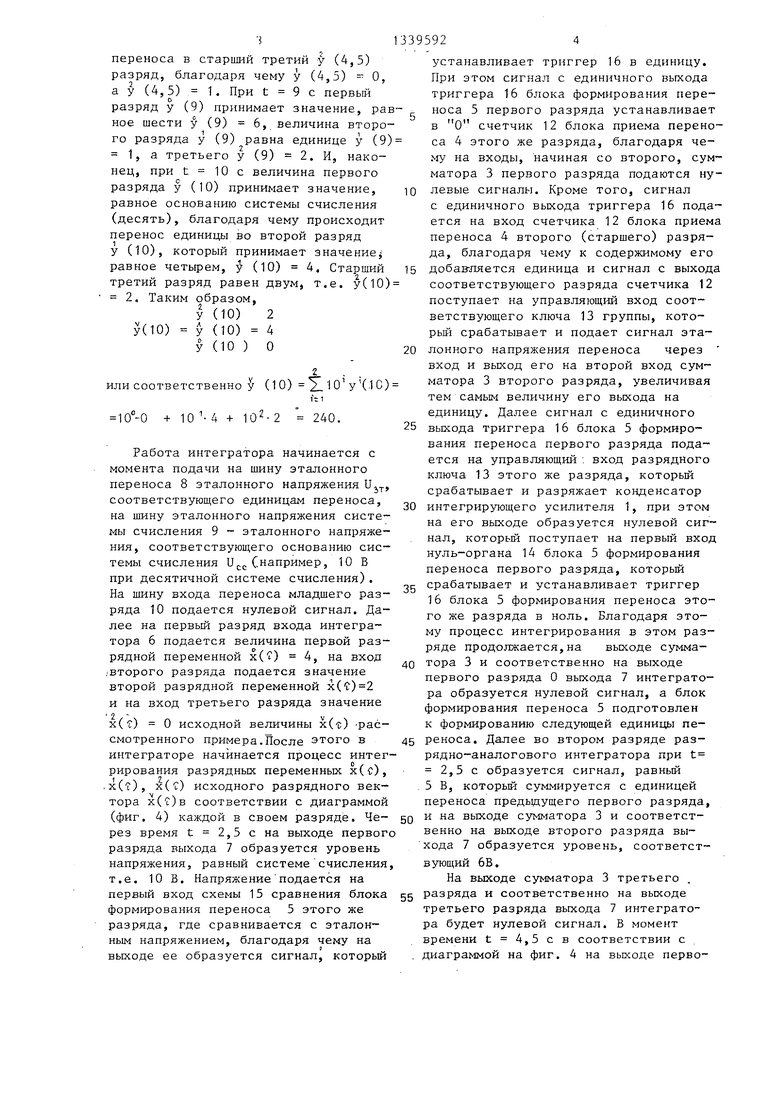

Блок 4 приема переноса (фиг. 2) содержит счетчик 12 и группу ключей 13.

Блок 5 формирования переноса (фиг. 3) содержит нуль-орган 14, схму 15 сравнения и триггер 16.

Работа интегратора поясняется на

примере реализации вьгражения вида

t

y(t) у(0) + J x(t) d1

(1)

Представим: выражение (1) в разрядной форме:

y(t)

y(-0)

x(€)

Ht)

y(0)

i()

y(o)

y(0)

x(rt

X(C)

(2)

где y(t), y(0), x( t) - разрядные векторы, формируемые как

(3)

г - логические системы счисления.

Рассмотрим изложенное на примере, когда г 10.

Исходная функция х( и) 24 const, время интегрирования t 10 с, начальные условия у(0) 0. В соответствии с выражением (1)

у(10) у(0) +J х(О dC

о 10

О + 24t j 240. о

Запишем исходные данные x(t), у(0) и результат у (10) в разрядной форме, полагая, что информация представляется тремя десятичными разрядами, т.е.

х(«) О у(0) О х(О х(г)2; (0) у(0)0;

х() 4

У (10)

У(10) (10). У(10)

У(0) О

(4)

0

5

0

5

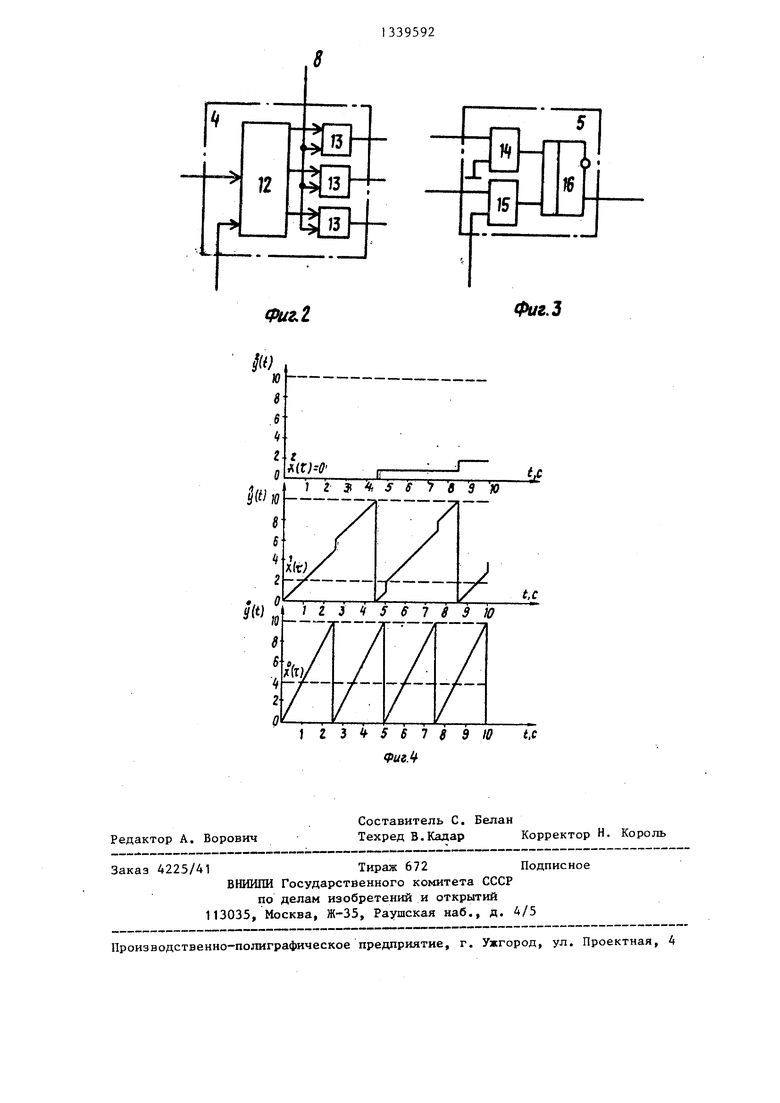

Процесс интегрирования представлен на фиг. 4. В исходном состоянии при t О разрядная переменная перво- го разряда x(-t) равна четырем, второ- го разряда хСС) равна двум и третье- го разряда х( С) равна нулю и соответственно у(0) О, у(0) О и у(0) -0.

Через 2,5 с, т.е. t 2,5, значение разрядной переменной у (2,5) первого разряда равно основанию системы, поэтому происходит перенос единицы в старший (второй) разряд,значение у (2,5) О, а к значению второго разряда у (2,5)., равному пяти, дббавляется единица и, в результате у (2,5) 6. Величина старшего разряда равна нулю у (2,5) 0. При t 4,5 величина первого разряда равна восьми у (4,5) 8, величина второго разряда у (4,5) достигает значения основания системы счисления (т.е. десяти), при этом передается единица

31

переноса в старший третий у (4,5) разряд, благодаря чему у (4,5) О, а у (4,5) 1. При t 9 с первый разряд у (9) принимает значение, равное шести у (9) 6, величина второго разряда у (9) равна единице у (9) 1, а третьего у (9) 2. И, наконец, при t 10 с величина первого разряда у (10) принимает значение, равное основанию системы счисления (десять), благодаря чему происходит перенос единицы во второй разряд у (10), который принимает значение равное четьфем, (10) 4. Старший третий разряд равен двум, т.е. у(10) 2. Таким образом,

У (10) 2 у(10) (10) 4

У (10 ) О

или соответственно у (10) уЧ-1С)

f-1

10°-0 ° 240.

Работа интегратора начинается с момента подачи на шину эталонного переноса 8 эталонного напряжения Uj, соответствующего единицам переноса, на шину эталонного напряжения системы счисления 9 - эталонного напряжения, соответствующего основанию системы счисления и,(, (.например, 10 В при десятичной системе счисления). На шину входа переноса младшего разряда 10 подается нулевой сигнал. Далее на первый разряд входа интегратора 6 подается величина первой разрядной переменной x( t) 4, на вход /второго разряда подается значение второй разрядной переменной х(С )2 и на вход третьего разряда значение

х(т) 0 исходной величины X( D) -рассмотренного примера.После этого в

интеграторе начинается процесс интегч / рирования разрядных переменных х(,с),

.х(т), х(С) исходного разрядного вектора х(С)в соответствии с диаграммой (фиг. 4) каждой в своем разряде. Через время t 2,5 с на выходе первог разряда выхода 7 образуется уровень напряжения, равный системе счисления т.е. 10 В. Напряжение подается на первый вход схемы 15 сравнения блока формирования переноса 5 этого же разряда, где сравнивается с эталонным напряжением, благодаря чему на выходе ее образуется сигнал, который

5924

устанавливает триггер 16 в единицу. При этом сигнал с единичного выхода триггера 16 блока формирования пере- носа 5 первого разряда устанавливает в О счетчик 12 блока приема переноса 4 этого же разряда, благодаря чему на входы, начиная со второго, сумматора 3 первого разряда подаются ну- левые сигналы. Кроме того, сигнал

с единичного выхода триггера 16 подается на вход счетчика 12 блока приема переноса 4 второго (старшего) разряда, благодаря чему к содержимому его добавляется единица и сигнал с выхода соответствующего разряда счетчика 12 поступает на управляющий вход соответствующего ключа 13 группы, кото- рьш срабатывает и подает сигнал эта- лонного напряжения переноса через вход и выход его на второй вход сумматора 3 второго разряда, увеличивая тем самым величину его выхода на единицу. Далее сигнал с единичного выхода триггера 16 блока 5 формирования переноса первого разряда подается на управляющий ; вход разрядного ключа 13 этого же разряда, который срабатывает и разряжает конденсатор интегрирующего усилителя 1, при этом на его выходе образуется нулевой сигнал, который поступает на первый вход нуль-органа 14 блока 5 формирования переноса первого разряда, который срабатывает и устанавливает триггер 16 блока 5 формирования переноса этого же разряда в ноль. Благодаря этому процесс интегрирования в этом разряде продолжается,на выходе сумма- тора 3 и соответственно на выходе

первого разряда О выхода 7 интегратора образуется нулевой сигнал, а блок формирования переноса 5 подготовлен к фор;у ированию следующей единицы пе- реноса. Далее во втором разряде раз- рядно-аналогового интегратора при t 2,5 с образуется сигнал, равный 5 В, которьй суммируется с единицей переноса предьщущего первого разряда, и на выходе сумматора 3 и соответственно на выходе второго разряда выхода 7 образуется уровень, соответствующий 6В.

На выходе сумматора 3 третьего разряда и соответственно на выходе третьего разряда выхода 7 интегратора будет нулевой сигнал. В момент времени t 4,5 с в соответствии с диаграммой на фиг. 4 на выходе первото разряда выхода 7 образуется уровень, соответствующий 8В. На выходе второго разряда выхода 7 образуется сигнал, соответствующий системе счисления (т.е. 10 в), которьй поступает на первый вход схемы 15 сравнения блока 5 формирования переноса второго разряда, которая срабатывает и устанавливает триггер 16 этого блока ю в единицу. Сигнал с единичного выхода триггера 16 устанавливает счетчик 12 блока 4 приема переноса второго разряда в ноль, тем самым обнуляет, начиная со второго, все входы сумма- 15 тора 3 этого же разряда Далее этот сигнал поступает на вход счетчика 12 блока приема переноса 4 старшего разряда, подавая тем самым на один

веяно равные у (10) 0, у (10) 4, у (10) 2, а результат вычислений в соответствии с (3) равен

у (10) 10°-О + 10 4 +

240. Формула изобретения

Аналоговый интегратор, содержащий п цепей, каждая из которых состоит из интегрирующего усилителя и сумматора, один из входов которого соединен с выходом интегрирующего усилителя, отличающийся тем, что, с целью повышения точности и расширения диапазона интегрируемог о сигнала, в каждую цепь введены блок из входов сумматора его уровень еди- 20 формирования переноса, содержащий ничного сигнала. И, наконец, сигнал триггер, нуль-орган и схему сравне- с единичного выхода триггера 16 пос- ния, и блок приема переноса, вклю- тупает на вход обнуления интегрирую- чающий счетчик и группу ключей, при- щего усилителя 1 второго разряда, разряжая тем самым конденсатор интег- 25 рирующего усилителя 1, благодаря чему на его выходе образуется нулевой сигнал. При этом срабатывает нуль- орган 14, устанавливающий триггер 16 в единицу, а на выходе второго раз- 30

чем в каждой цепи выход интегрирующего усилителя соединен с первьм входом нуль-органа блока формирования переноса,второй вход которого подключен к шине нулевого потенциала, а выход связан с R-входом триггера, единичньй выход которого подключен к входу обнуления интегрирующего усилителя, к входу установки в О счетчика блока приема переноса этой же цепи и счетному входу счетчика блоряда образуется нулевой сигнал. Таким образом, на выходе третьего разряда сформируется сигнал у (4,5) 1, на выходе второго разряда - у (,5) О

и на выходе первого разряда - у (4,5)35 ка приема переноса следующей цепи, 8.

В момент времени t 9 на выходах 7 образуются сигналы у (9) 6, у (9) 1 и у (9) 2. В конце интервала интегрирования при t 10 на выходе первого разряда образуется уровень, соответствующий системе счисления (т.е. 10 В). При этом срабатывает блок 5 формирования переноса первого разряда, которьй добавляет единицу во второй старший разряд и обнуляет первый разряд благодаря

разрядные выходы счетчика блока приема переноса подключены к управл ющим входам ключей группы, выходами связанных с соответствующими входам

40 сумматора, выход которого является разрядным выходом интегратора и под ключен к первому входу схемы сравне ния блока формирования переноса, вт рой вход которой соединен с шиной

45 эталонноого напряжения, а выход под ключен к S-входу триггера блока фор мирования переноса-, информационные входы ключей группы всех блоков при

чему на выходе первого разряда образуется нулевой сигнал у (10) 0.

45 эталонноого напряжения, а выход подключен к S-входу триггера блока формирования переноса-, информационные входы ключей группы всех блоков приема переноса подключены к шине эта- На втором выходе 7 образуется сигнал, 50 лонного напряжения переноса, причем

которьй в сумме с единицей переноса И51 младшего разряда будет равен (10) 4. На выходе третьего старшего разряда формируется сигнал у (10) 2. Таким образом, на выходах 7 образуются сигналы, соответствеяно равные у (10) 0, у (10) 4, у (10) 2, а результат вычислений в соответствии с (3) равен

у (10) 10°-О + 10 4 +

240. Формула изобретения

Аналоговый интегратор, содержащий п цепей, каждая из которых состоит из интегрирующего усилителя и сумматора, один из входов которого соединен с выходом интегрирующего усилителя, отличающийся тем, что, с целью повышения точности и расширения диапазона интегрируемог о сигнала, в каждую цепь введены блок формирования переноса, содержащий триггер, нуль-орган и схему сравне- ния, и блок приема переноса, вклю- чающий счетчик и группу ключей, при-

чем в каждой цепи выход интегрирующего усилителя соединен с первьм входом нуль-органа блока формирования переноса,второй вход которого подключен к шине нулевого потенциала, а выход связан с R-входом триггера, единичньй выход которого подключен к входу обнуления интегрирующего усилителя, к входу установки в О счетчика блока приема переноса этой же цепи и счетному входу счетчика блока приема переноса следующей цепи,

разрядные выходы счетчика блока приема переноса подключены к управляющим входам ключей группы, выходами связанных с соответствующими входами

сумматора, выход которого является разрядным выходом интегратора и подключен к первому входу схемы сравнения блока формирования переноса, второй вход которой соединен с шиной

эталонноого напряжения, а выход подключен к S-входу триггера блока формирования переноса-, информационные входы ключей группы всех блоков приБход переноса блока приема переноса первой цепи является входом переноса младшего разряда, а выход триггера блока приема переноса последней gg цепи является выходом переноса старшего разряда.

Г

W

О

15

1риг.2

Фиг.З

(г;--(7

I г $ S f7 в 3 JO

iZ5456789W

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ФОРМИРОВАНИЯ ЛИНЕАРИЗИРОВАННОГО СИГНАЛА НА ВРАЩАЮЩЕЙСЯ ПО УГЛУ КРЕНА РАКЕТЕ. ЛИНЕАРИЗАТОР СИГНАЛА. ПЕРЕКЛЮЧАЕМЫЙ ЛИНЕАРИЗАТОР СИГНАЛА. СПОСОБ ИНТЕГРИРОВАНИЯ ДЛЯ ФОРМИРОВАНИЯ ЛИНЕАРИЗИРОВАННОГО СИГНАЛА И ЦИФРОВОЙ ИНТЕГРАТОР ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2014 |

|

RU2549231C1 |

| Функциональный генератор | 1980 |

|

SU896637A1 |

| Разрядно-аналоговый сумматор | 1987 |

|

SU1548797A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Преобразователь @ -ичного позиционного кода в двоичный код | 1983 |

|

SU1115045A1 |

| Дискретно-аналоговый интегратор | 1986 |

|

SU1372337A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ ОТ ЧИСЛА | 1991 |

|

RU2023346C1 |

| Функциональный аналого-цифровой преобразователь | 1983 |

|

SU1113813A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ ОТ ЧИСЛА | 1991 |

|

RU2020759C1 |

Изобретение относится к,области вычислительной техники и может быть использовано в качестве спецпроцессора в комплексе с цифровой вычислительной машиной для оперативного решения систем линейных и нелинейных дифференциальных уравнений. Целью изобретения является повышение точности и расширение диапазона интегрируемого сигнала. Цель достигается благодаря поразрядному представлению исходных данных и организации процесса интегрирования в разрядно-аналого- вой форме. Интегратор содержит п цепей по числу разрядов, каждая из которых состоит из интегрирующего усилителя 1, аналогового сумматора 3, блока приема переноса 4 и блока формирования переноса 5. 4 ил. а СО со СО сд со ю

Редактор А. Ворович

Заказ 4225/41Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно

i-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Составитель С. Белан

Техред В.Кадар Корректор Н. Король

| Аналого-дискретное интегрирующее устройство | 1979 |

|

SU875407A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Усредняющее устройство | 1985 |

|

SU1300503A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-09-23—Публикация

1986-02-12—Подача