f

(21)4301703/24-24

(22)08.09.87

(46) 07.03.90. Бюл. Н 9

(71)Институт проблем моделирования в энергетике АН УССР и Специальное конструкторско-технологическое бюро средств моделирования Института проблем моделирования в энергетике АН УССР

(72)Г.Е.Пухов, В.П.Романцов,- А.Ф.Новицкий и С.Я.Гильгурт (53) 681.335 (088.8)

(56) Авторское свидетельство СССР № 423133, кл. G 06 G 7/14, 1974. Авторское свидетельство СССР № 423132, кл. G 06 G 7/14, 1874.

(54) РАЗРЯДНО-АНАЛОГОВЫЙ СУММАТОР (57) Изобретение относится к области вычислительной техники в частности к гибридной вычислительной технике, и может быть использовано для построения арифметических устройств параллельного действия. Цель изобретения - расширение функциональных возможностей устройства в части перестройки его в процессе работы на любую позиционную систему счисления. Устройство содержит первую и вторую группы аналоговых сумматоров 1.1, 1.2, 1,3, и 2.1, 2.2 2,3, блоки 3 формирования переноса, блоки 4 приема переноса, нуль-органы 5, входные , выходную шину 7,

| название | год | авторы | номер документа |

|---|---|---|---|

| Разрядно-аналоговый сумматор | 1988 |

|

SU1589293A1 |

| Аналоговый интегратор | 1986 |

|

SU1339592A1 |

| Аналого-цифровой сумматор | 1986 |

|

SU1316006A1 |

| Устройство для вычисления функций | 1986 |

|

SU1388848A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Устройство для контроля экспоненциальных процессов | 1987 |

|

SU1500997A1 |

| Устройство для контроля экспоненциальных процессов | 1990 |

|

SU1732331A1 |

| Устройство для решения дифференциальных уравнений | 1984 |

|

SU1257671A1 |

| Устройство для вычисления квадратного корня | 1986 |

|

SU1359778A1 |

| Преобразователь последовательного знакоразрядного кода в дополнительный двоичный код | 1983 |

|

SU1113796A1 |

Изобретение относится к области вычислительной техники, в частности к гибридной вычислительной технике, и может быть использовано для построения арифметических устройств параллельного действия. Цель изобретения - расширение функциональных возможностей устройства в части перестройки его в процессе работы на любую позиционную систему счисления. Устройство содержит первую и вторую группы аналоговых сумматоров 1.1, 1.2, 1.3 и 2.1, 2.2, 2.3, блоки 3 формирования переноса, блоки 4 приема переноса, нуль-органы 5, входные шины 6, выходную шину 7, шину 8 эталонного инвертированного напряжения основания системы счисления, шину 9 эталонного напряжения основания системы счисления, шину 10 эталонного инвертированного напряжения единицы системы счисления, шину 11 входа переноса младшего разряда, шину 12 выхода переноса старшего разряда. Перестройка на любую позиционную систему счисления достигается путем установки на шинах 8 - 10 соответствующих напряжений. 1 з.п. ф-лы, 3 ил.

(Л

/

Ы

Јь 00 4

СО

fflw/

315

шину 8 эталонного инвертированного напряжения основания системы счисления, шину 9 эталонного напряжения основания системы счисления, шину 10 эталонного инвертированного напряжения единицы системы счисления, шину

Изобретение относится к вычислительной технике, в частности к гибридной вычислительной технике, и может быть использовано для построения арифмети- | ческих устройств параллельного дейст- вия, а также в специализированных раз- рядно-аналоговых устройствах в качестве основного блока для синтеза матричных умножений, функциональных преоба- зований и иных матричных устройств,

Целью изобретения является расширение функциональных возможностей устройства в части перестройки его в процессе работы на любую позиционную 2 систему счисления.

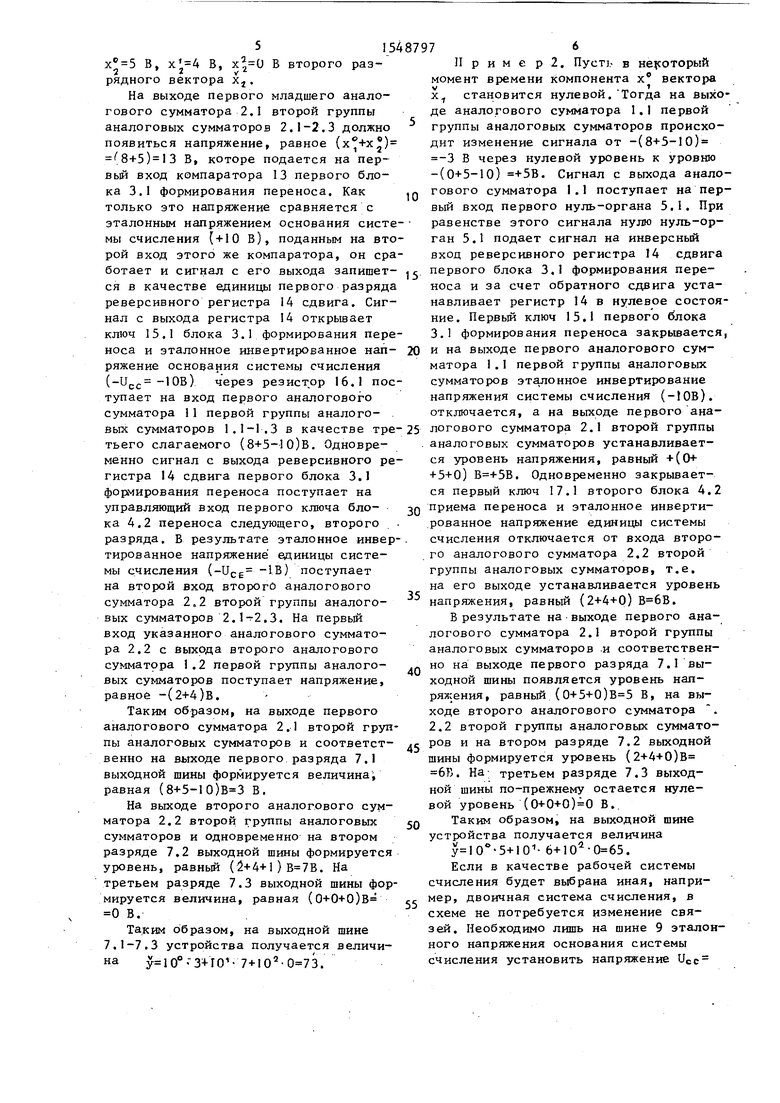

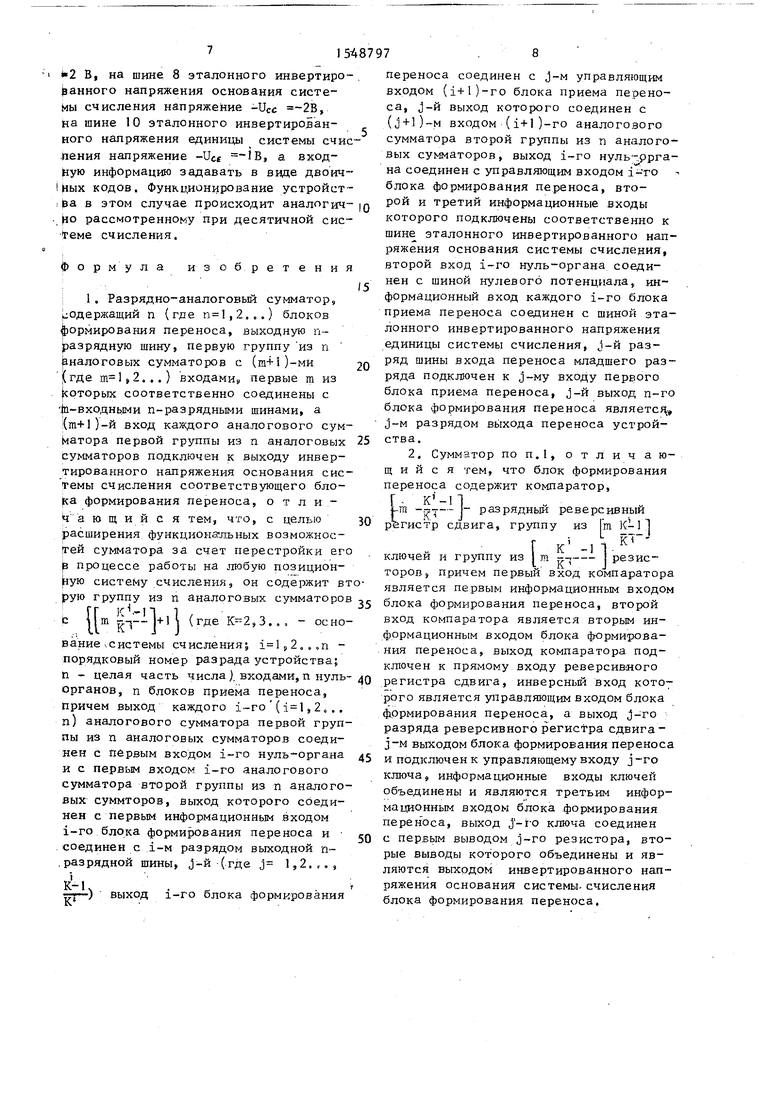

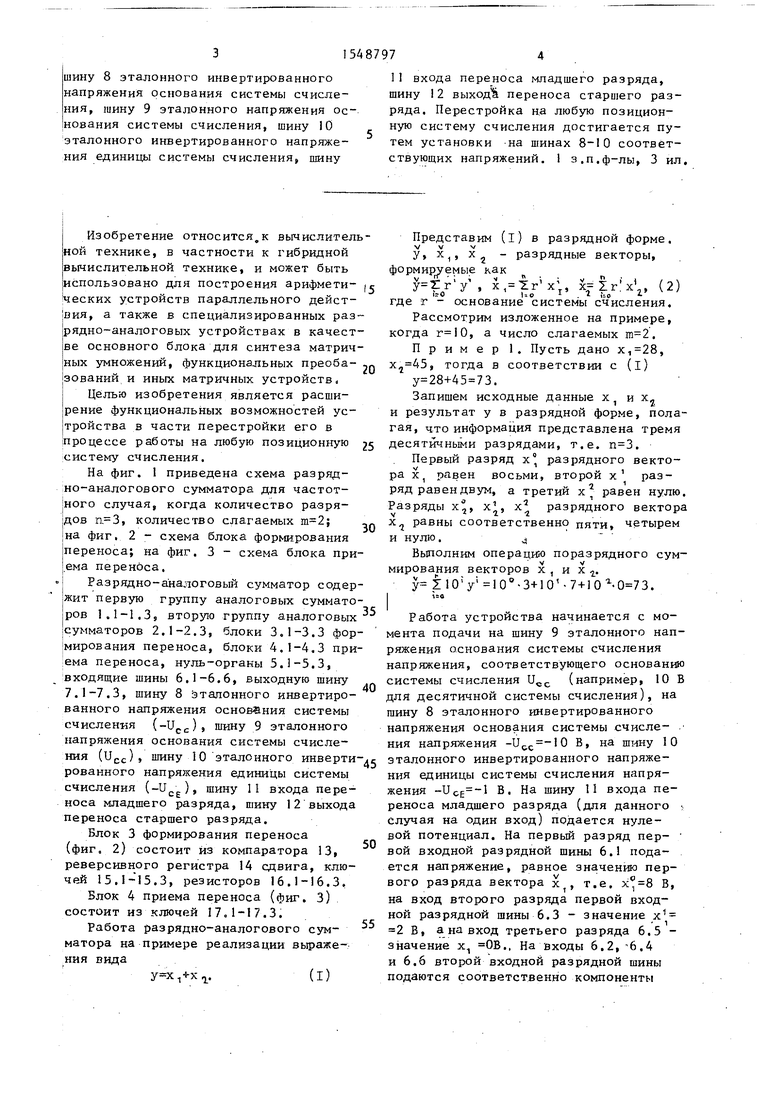

На фиг. 1 приведена схема разряд- но-аналогового сумматора для частот- ого случая, когда количество разрядов , количество слагаемых . на фиг, 2 - схема блока формирования переноса; на фиг. 3 - схема блока при- t&MB переноса,

Разрядно-аналоговый сумматор содержит первую группу аналоговых сумматоров 1.1-1.3, вторую группу аналоговых сумматоров 2.1-2.3, блоки 3.1-3.3 формирования переноса, блоки 4.1-4.3 приема переноса, нуль-органы 5.1-5.3, входящие шины 6,1-6.6, выходную шину 7.1-7.3, шину 8 эталонного инвертированного напряжения основания системы счисления (-Ucc), шину 9 эталонного напряжения основания системы счисления (Ucc), шину 10 эталонного инвертированного напряжения единицы системы счисления (-U ), шину И входа переноса младшего разряда, шину 12 выхода переноса старшего разряда.

Блок 3 формирования переноса (фиг. 2) состоит из компаратора 13, реверсивного регистра 14 сдвига, ключей 15.1-15.3, резисторов 16,1-16.3.

Блок 4 приема переноса (фиг. 3) состоит из ключей 17.1-17.3.

Работа разрядно-аналогового сум- матора на примере реализации выражения вида

.л+хг.(I)

11

входа переноса младшего разряда, шину 12 выхода переноса старшего разряда. Перестройка на любую позиционную систему счисления достигается путем установки на шинах 8-10 соответствующих напряжений. 1 з.п.ф-лы, 3 ил.

.

1 х 2 - разрядные векторы,

0

Представим (l) в разрядной форме.

V

У формируемые как

, i, tr x;, хГЈог х г, (2)

где г - основание °системы с числения.

Рассмотрим изложенное на примере, когда , а число слагаемых т-2.

Пример 1. Пусть дано , , тогда в соответствии с (l)

у 28+45 73.

Запишем исходные данные хf и х и результат у в разрядной форме, полагая, что информация представлена тремя десятичными разрядами, т.е. .

Первый разряд х° разрядного вектора х1 равен восьми, второй х разряд равен двум, а третий х равен нулю. Разряды х, х , х1 разрядного вектора х равны соответственно пяти, четырем и нулю. j

Выполним операцию поразрядного суммирования векторов х , и х г.

у Z10;y 100-3+10 -7 + 10a..

I1 0

Работа устройства начинается с момента подачи на шину 9 эталонного напряжения основания системы счисления напряжения, соответствующего основанию системы счисления Ucc (например, 10 В для десятичной системы счисления), на шину 8 эталонного инвертированного напряжения основания системы счисления напряжения В, на шину 10 эталонного инвертированного напряжения единицы системы счисления напряжения В. На шину 11 входа переноса младшего разряда (для данного . Случая на один вход) подается нулевой потенциал. На первый разряд первой входной разрядной шины 6.1 подается напряжение, равное значению первого разряда вектора х , т.е. В, на вход второго разряда первой входной разрядной шины 6.3 - значение х1 2 В, а на вход третьего разряда 6.5 - значение х, ОВ., На входы 6.2, 6.4 и 6.6 второй входной разрядной шины подаются соответственно компоненты

В, В, В второго разрядного вектора хг.

вектора становится нулевой.Тогда на выхо

V. 1

10

На выходе первого младшего аналогового сумматора 2.1 второй группы аналоговых сумматоров 2.1-2.3 должно появиться напряжение, равное () 8+5)13 В, которе подается на первый вход компаратора 13 первого блока 3.1 формирования переноса. Как только это напряжение сравняется с эталонным напряжением основания систе- мы счисления (+10 В), поданным на второй вход этого же компаратора, он сработает и сигнал с его выхода запишет- с первого блока 3.1 формирования пере- ся в качестве единицы первого разряда носа и за счет обратного сдвига уста- реверсивного регистра 14 сдвига. Сигнал с выхода регистра 14 открывает ключ 15.1 блока 3.1 формирования переноса и эталонное инвертированное нал- 20 и на выходе первого аналогового сум- ряжение основания системы счисления матора 1.1 первой группы аналоговых () через резистор 16.1 поступает на вход первого аналогового сумматора 11 первой группы аналоговых сумматоров 1.1-1.3 в качестве тре-25 лотового сумматора 2.1 второй группы тьего слагаемого (8+5-10)В. Одновре- аналоговых сумматоров устанавливает- менно сигнал с выхода реверсивного регистра 14 сдвига первого блока 3.1 формирования переноса поступает на управляющий вход первого ключа блока 4.2 переноса следующего, второго

де аналогового сумматора 1.1 первой группы аналоговых сумматоров происходит изменение сигнала от -(8+5-10) -3 В через нулевой уровень к уровню -(0+5-10) +5В. Сигнал с выхода анало гового сумматора 1.1 поступает на пер вый вход первого нуль-органа 5.1. При равенстве этого сигнала нулю нуль-орган 5.1 подает сигнал на инверсный вход реверсивного регистра 14 сдвига

навливает регистр 14 в нулевое состоя ние. Первый ключ 15.1 первого блока 3.1 формирования переноса закрывается

сумматоров эталонное инвертирование напряжения системы счисления (-IOB). отключается, а на выходе первого анася уровень напряжения, равный + (0+ +5+0) . Одновременно закрывается первый ключ 17.1 второго блока 4.2 3Q приема переноса и эталонное инвертированное напряжение единицы системы

разряда. В результате эталонное инвертированное напряжение единицы системы счисления (-UCЈ -IB) поступает на второй вход второго аналогового

счисления отключается от входа в го аналогового сумматора 2.2 вто группы аналоговых сумматоров, т. на его выходе устанавливается ур

сумматора 2,2 второй группы аналого- напряжения, равный (2+4+0) .

вых сумматоров 2.1-2.3. На первый вход указанного аналогового сумматора 2.2 с выхода второго аналогового сумматора 1.2 первой группы аналоговых сумматоров поступает напряжение, равное -(2+4)В.

Таким образом, на выходе первого аналогового сумматора 2.1 второй группы аналоговых сумматоров и соответст- ,с ров и на втором разряде 7.2 выходной венно на выходе первого разряда 7.1 шины формируется уровень (2+4+0)В выходной шины формируется величина, 6В. На третьем разряде 7.3 выходравная (8+5-10) В.

На выходе второго аналогового сумматора 2.2 второй группы аналоговых сумматоров и одновременно на втором разряде 7.2 выходной шины формируется уровень, равный (2+4+1 ). На третьем разряде 7.3 выходной шины формируется величина, равная (0+0+0)В 0 В.

Таким образом, на выходной шине 7.1-7.3 устройства получается величина у Ю°--3+ГОл- 7+Ю2-0 73.

50

55

ной шины по-прежнему остается нулевой уровень (0+0+0)0 В.

Таким образом, на выходной шине устройства получается величина

у 10°-5+Ю1- Ь+Ю2 0 65.

Если в качестве рабочей системы счисления будет выбрана иная, например, двоичная система счисления, в схеме не потребуется изменение связей. Необходимо лишь на шине 9 эталон ного напряжения основания системы счисления установить напряжение Ucc

Пример. в некоторый

вектора становится нулевой.Тогда на выхомомент времени компонента х

V. 1

первого блока 3.1 формирования пере- носа и за счет обратного сдвига уста- и на выходе первого аналогового сум- матора 1.1 первой группы аналоговых лотового сумматора 2.1 второй группы аналоговых сумматоров устанавливает-

первого блока 3.1 формирования пере- носа и за счет обратного сдвига уста- и на выходе первого аналогового сум- матора 1.1 первой группы аналоговых лотового сумматора 2.1 второй группы аналоговых сумматоров устанавливает-

де аналогового сумматора 1.1 первой группы аналоговых сумматоров происходит изменение сигнала от -(8+5-10) -3 В через нулевой уровень к уровню -(0+5-10) +5В. Сигнал с выхода аналогового сумматора 1.1 поступает на первый вход первого нуль-органа 5.1. При равенстве этого сигнала нулю нуль-орган 5.1 подает сигнал на инверсный вход реверсивного регистра 14 сдвига

первого блока 3.1 формирования пере- носа и за счет обратного сдвига уста- и на выходе первого аналогового сум- матора 1.1 первой группы аналоговых лотового сумматора 2.1 второй группы аналоговых сумматоров устанавливает-

навливает регистр 14 в нулевое состояние. Первый ключ 15.1 первого блока 3.1 формирования переноса закрывается,

первого блока 3.1 формирования пере- носа и за счет обратного сдвига уста- и на выходе первого аналогового сум- матора 1.1 первой группы аналоговых лотового сумматора 2.1 второй группы аналоговых сумматоров устанавливает-

сумматоров эталонное инвертирование напряжения системы счисления (-IOB). отключается, а на выходе первого анапервого блока 3.1 формирования пере- носа и за счет обратного сдвига уста- и на выходе первого аналогового сум- матора 1.1 первой группы аналоговых лотового сумматора 2.1 второй группы аналоговых сумматоров устанавливает-

ся уровень напряжения, равный + (0+ +5+0) . Одновременно закрывается первый ключ 17.1 второго блока 4.2 приема переноса и эталонное инвертированное напряжение единицы системы

счисления отключается от входа второго аналогового сумматора 2.2 второй группы аналоговых сумматоров, т.е. на его выходе устанавливается уровень

В результате на выходе первого аналогового сумматора 2.1 второй группы аналоговых сумматоров и соответственно на выходе первого разряда 7.1 выходной шины появляется уровень напряжения, равный (0+5+0) В, на выходе второго аналогового сумматора . 2.2 второй группы аналоговых суммато

ной шины по-прежнему остается нулевой уровень (0+0+0)0 В.

Таким образом, на выходной шине устройства получается величина

у 10°-5+Ю1- Ь+Ю2 0 65.

Если в качестве рабочей системы счисления будет выбрана иная, например, двоичная система счисления, в схеме не потребуется изменение связей. Необходимо лишь на шине 9 эталонного напряжения основания системы счисления установить напряжение Ucc

2 В, на шине 8 эталонного инвертиро- Јанного напряжения основания системы счисления напряжение -Ucc 2B, да шине 10 эталонного инвертированного напряжения единицы системы счис- пения напряжение -UCЈ 1B, а входную информацию задавать в виде двоич- IНых кодов. Функционирование устройства в этом случае происходит аналогич- IQ |ио рассмотренному при десятичной системе счисления.

Формула изобретения

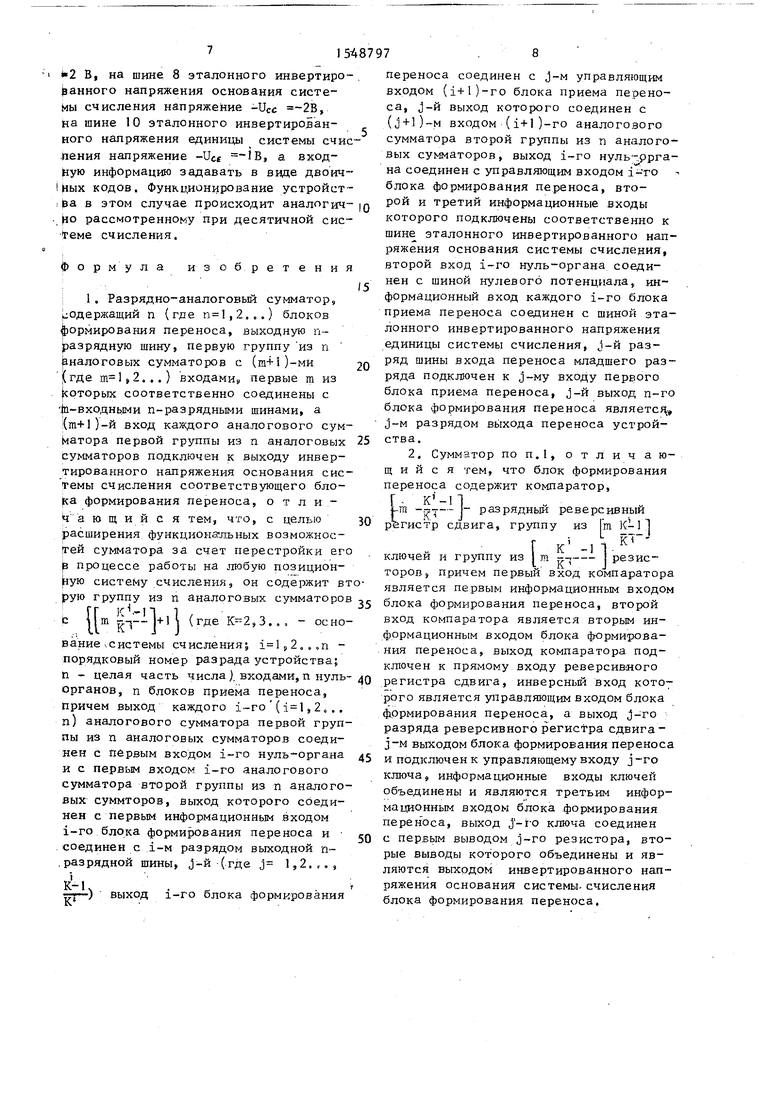

/5 1 . Разрядно-аналоговый сумматор,

содержащий п (где ,2...) блоков формирования переноса, выходную п- разрядную шину, первую группу из п аналоговых сумматоров с (га-Н)-ми20

(где т-1,2...) входами первые т из Которых соответственно соединены с jn-входными п-раз рядными шинами, а (т+)-й вход каждого аналогового сум йатора первой группы из п аналоговых 25 сумматоров подключен к выходу инвертированного напряжения основания системы счисления соответствующего блока формирования переноса, отличающийся тем, что, с целью30 расширения функциональных возможностей сумматора за счет перестройки его р процессе работы на любую позицион- Ную систейу счисления9 он содержит вторую группу из п аналоговых сумматоров ,,гг Н.-П 1 /

с tlm --}- +1 (где ,3... - основание ..системы счисления-, i l9200,n - порядковый номер разрада устройства; П - целая часть числа) входами,п нуль- д органов, п блоков приема переноса, причем выход каждого 1-го (,2. .. п) аналогового сумматора первой группы из п аналоговых сумматоров соединен с первым входом 1-го нуль-органа д5 и с первым входсм 1-го аналогового сумматора второй группы из п аналоговых суммторов, выход которого соединен с первым информационным входом 1-го блока формирования переноса и JQ соединен с i-м разрядом выходной п- разрядной шины, j-й (где j 1,2,..,

Јl К

) выход 1-го блока формирования

переноса соединен с j-м управляющим входом (i+l)-ro блока приема переноса, j-й выход которого соединен с (j + l)-M входом (i+0-го аналогового сумматора второй группы из п аналоговых сумматоров, выход 1-го нуль-ррга- на соединен с управляющим входом 1-го блока формирования переноса, второй и третий информационные входы которого подключены соответственно к шине эталонного инвертированного напряжения основания системы счисления, второй вход 1-го нуль-органа соединен с шиной нулевого потенциала, информационный вход каждого 1-го блока приема переноса соединен с шиной эталонного инвертированного напряжения единицы системы счисления, j-й разряд шины входа переноса младшего разряда подключен к j-му входу первого блока приема переноса, j-й выход п-го блока формирования переноса являетс% j-м разрядом выхода переноса устройства.

Г К - 1 1

j-m --7--- Г разрядньй реверсивный

регистр сдвига, группу из

Г к -1 1 I™ RT- J

I m К-11 L-,

ключей и группу из j га j резисторов, причем первый вход компаратора является первым информационным входом блока формирования переноса, второй вход компаратора является вторым информационным входом блока формирования переноса, выход компаратора подключен к прямому входу реверсивного регистра сдвига, инверсный вход которого является управляющим входом блока формирования переноса, а выход j-ro разряда реверсивного регистра сдвига- j-м выходом блока формирования переноса и подключен к управляющему входу j -го ключа, информационные входы ключей объединены и являются третьим информационным входом блока формирования переноса, выход j -ro ключа соединен с первым выводом j-ro резистора, вторые выводы которого объединены и являются выходом инвертированного напряжения основания системы- счисления блока формирования переноса.

Г

71

TU

L.±U jo

Фиг.з

Авторы

Даты

1990-03-07—Публикация

1987-09-08—Подача