Изобретение относится к цифровой вычислительной технике и может при- меняться в цифровых вычислительных машинах как арифметический расширитель и, кроме того, может использоваться в специализированных вычислительных устройствах.

Цель изобретения - увеличение быстродействия и расширение функциональных возможностей за счет обеспечения возможности работы с дополнительными кодами.

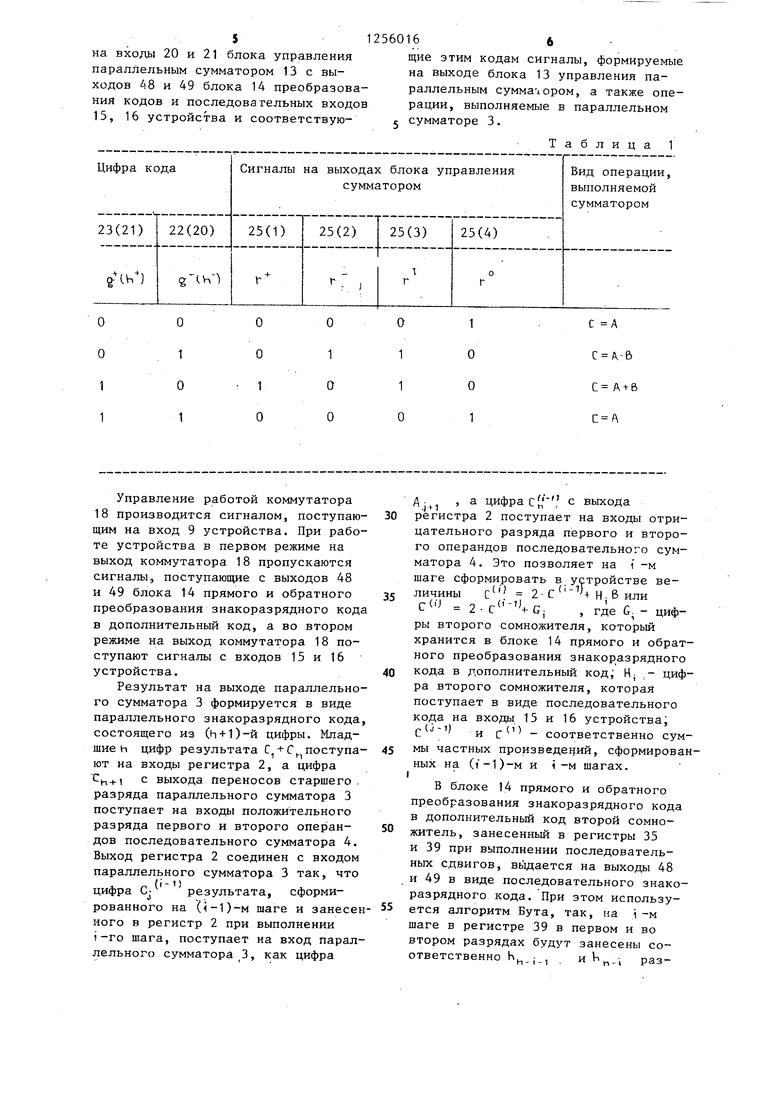

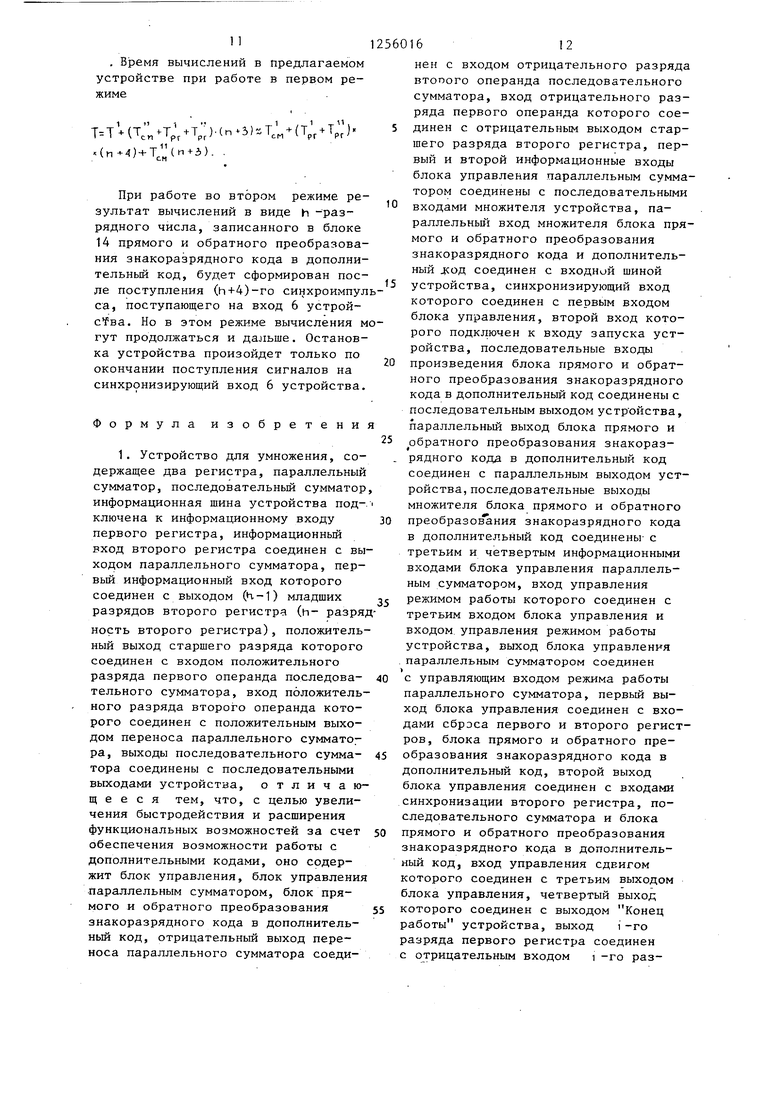

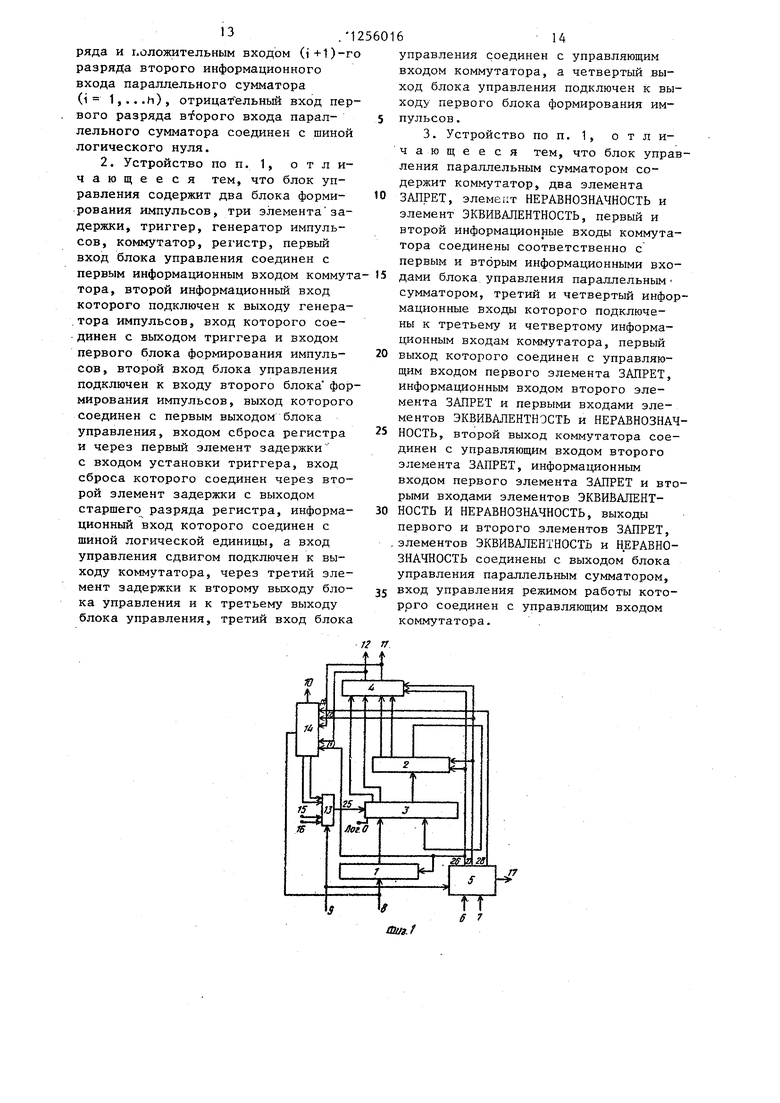

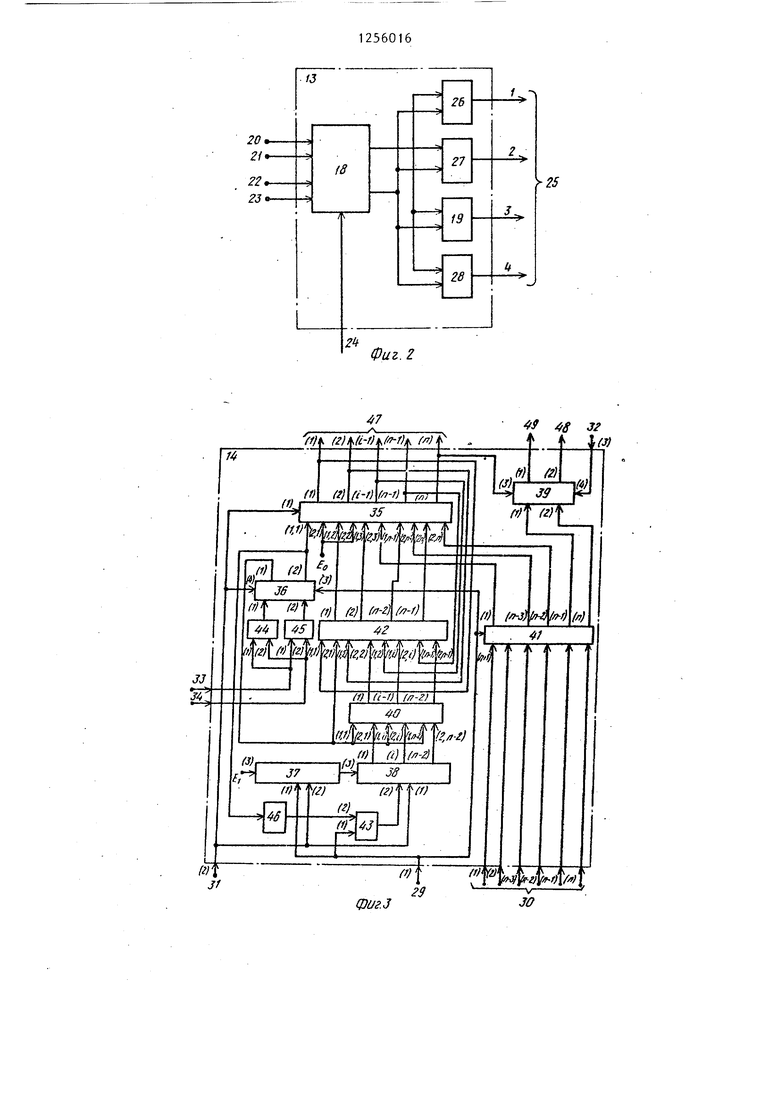

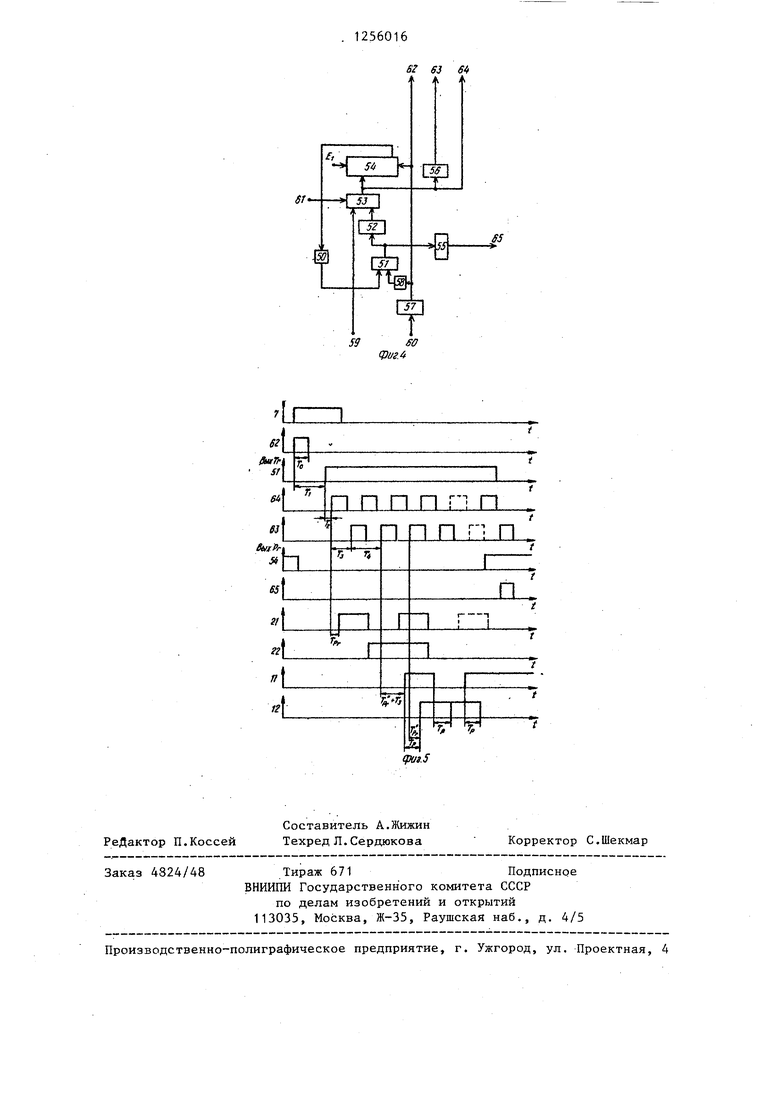

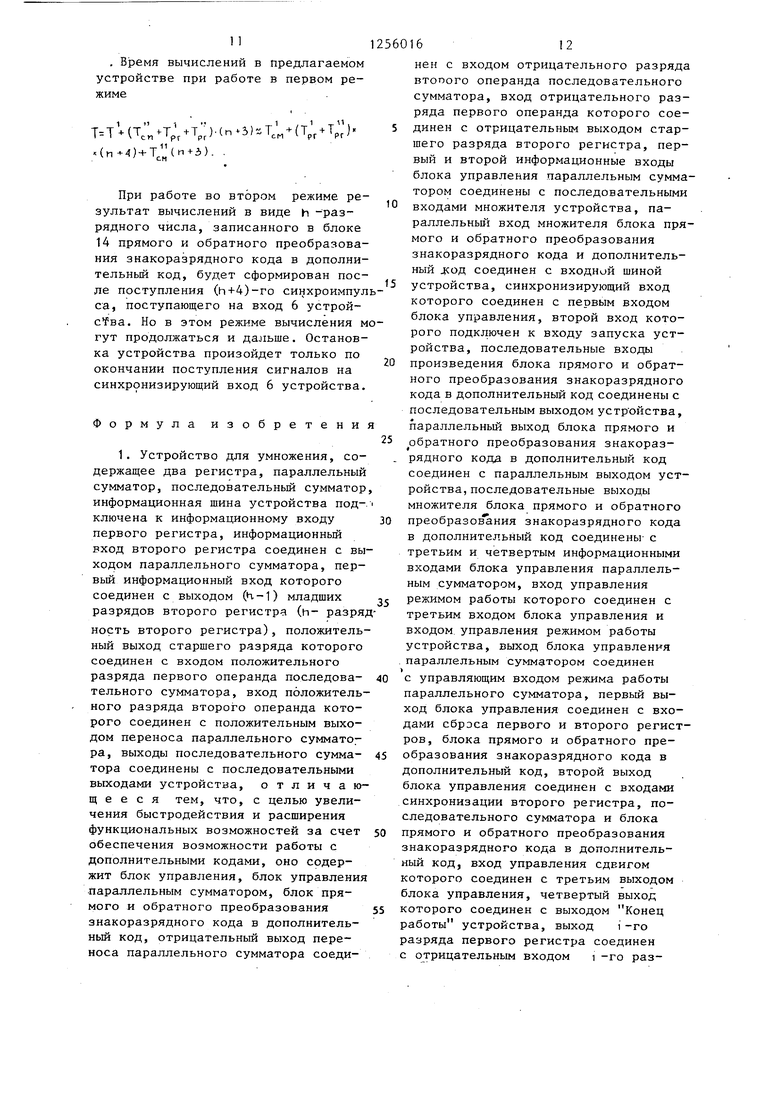

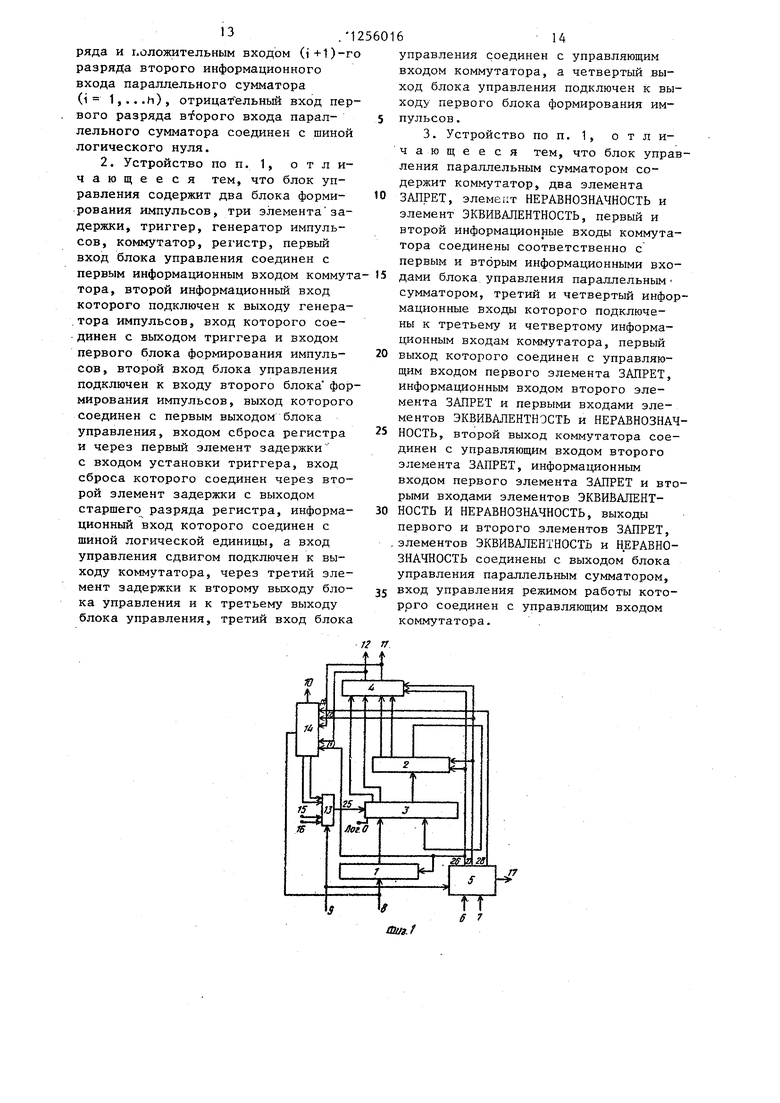

На фиг. 1 изображена блок-схема предлагаемого устройства для умножения; на фиг. 2 - блок-схема управления параллельным сумматором, на фиг. 3 - блок-схема блока прямого и обратного преобразования знакораз- рядного кода в дополнительный код, на фиг. 4 - блок-схема блока управления; на фиг. 5 - временные диаграммы работы устройства.

Устройство для умножения (фиг. 1) содержит два регистра 1 и 2, параллельный сумматор 3, последовательный сумматор 4 и блок 5 управления, синхронизирующий вход 6 устройства, запускающий вход 7 устройства, информационную шину 8 устройства, вход 9 управления режимом работы устройства, параллельный выход 10 устройства, последовательные выходы 11 и 12 усройства, блок 13 управления параллельным сумматором, блок

14прямого и обратного преобразования знакоразрядного кода в дополнительный код, последовательные входы

15и 16 множителя устройства, выход 17 Конец работы устройства,блок

13 управления параллельным сумматором (фиг. 2) содержит коммутатор 18 элемент НЕРАВНОЗНАЧНОСТЬ 19, четыре информационных входа 20-23, вход 24 управления режимом работы, выход 25, два элемента ЗАПРЕТ 26 и 27, элемент ЭКВИВАЛЕНТНОСТЬ 28., Блок 14 йрямого преобразования знакоразрядного кода в дополнительный код (фиг. 3) содержит вход 29 сброса параллельный вход 30 множителя, вхо 31 синхронизации, вход 32 управления, сдвигом, последовательные входы произведения 33 и 34, пять регистров 35-39, две группы элементов И 40 и 41, группу элементов НЕРАВНОЗНАЧНОСТЬ 42, элемент ИЛИ 43, элемент ЗАПРЕТ 44, элемент НЕРАВНОЗНАЧНОСТЬ 45, блок 46 формирования им

5

0

5

0

5

0

5

50

55

пульсов, параллельный вход 47, последовательные выходы множителя 48 и 49.

Блок управления 5 (фиг. 4) содержит элемент 50 задержки, триггер 51, генератор 52 импульсов, коммутатор 53, регистр 54, блок 55 формирования импульсов, элемент 56 задержки, блок 57 формирования импульсов, элемент 58 задержки, входы 59-61, выходы 62-65.

Устройство для умножения работает следующим образом.

Устройство работает в двух режимах. При работе в первом режиме производится умножение двух сомножителей, которые поступают в устройство по информационной шине 8 в дополнительных двоичных кодах.

При работе во втором режиме производится умножение сомножителей, один из которых поступает на информационную шину 8 устройства в дополнительном двоичном коде, а второй поступает на входы -13 -и 16 в

последовательном знакоразрядном коде. 1 .

Для задания режима работы устройства используется управляющий вход 9 устройства. Если на этот вход поступает единичньш потенциал, устройство работает в первом режиме, если же нулевой, то устройство работает во втором режиме. Работа устройства, как в первом, так и во втором режиме начинается с того, что на запускающий вход 7 устройства поступает единичньш импульс произвольной длительности, при этом в схеме 57 формирования импульса вырабатывается единичный импульс с длительностью TO , по которому производится установка в О регистра 2, последовательного сумматора 4, регистров 36-38 в блоке 14 прямого и обратного преобразования знакоразрядного кода в дополнительный код, регистра 54 в блоке 5 управления, . и производится прием в регистр 1 первого сомножителя и занесение в блок 14 прямого и обратного преобразования знакоразрядного кода в дополнительный код второго сомножителя. В блоке 14 прямого и обратного преобразования знакоразрядного кода в дополнительный код и -раз- рядньй сомножитель через группу элементов И 41 поступает на входы регистра 35 и регистра 39. В двухряда второго сомножителя и на выходах 48 и 49 будет сформирована

/U.

цифра в знакоразрядном h.

h-i

h

h-1 -1

При появлении на i-м шаге син хроимпульсов на выходе блока 5 управления в блоке 14 прямого и об ратного преобразования энакоразряд ного кода в дополнительный код про

изводится сдвиг разрядов h, - h ,j

второго сомножителя, хранящихся в регистре 36, кроме того производит ся прием 3 блок 14 прямого и обрат ного преобразования знакоразрядно- го кода в дополнительный кодцифр

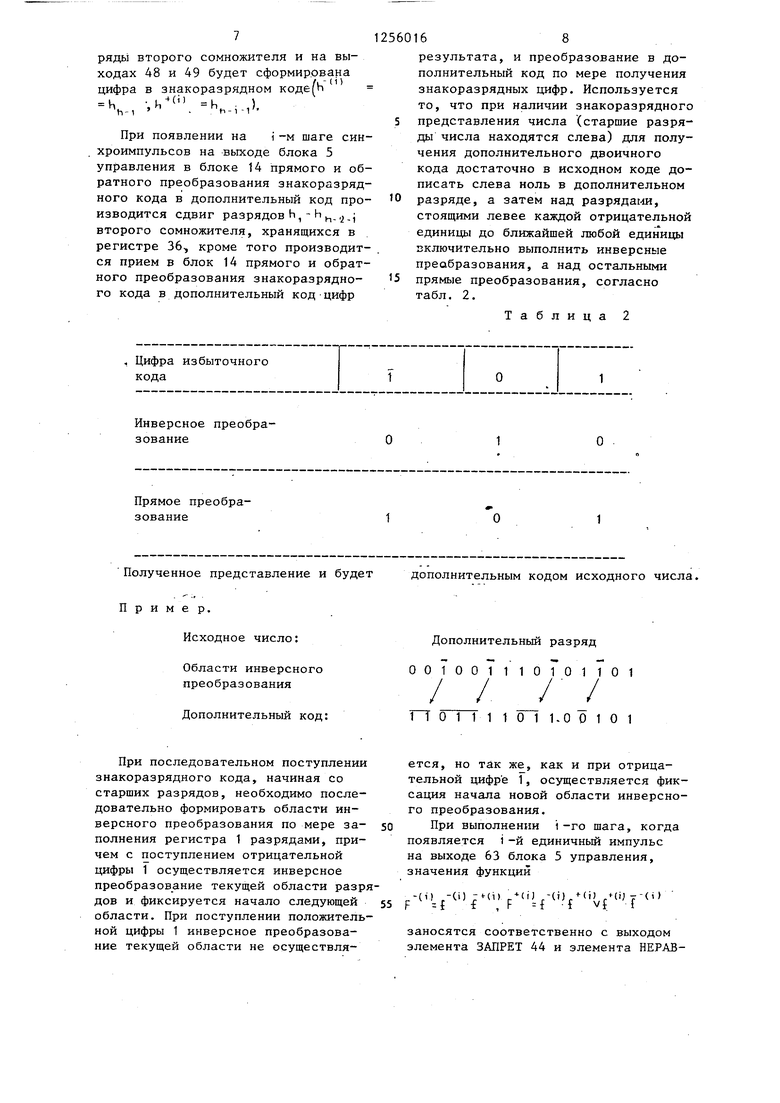

Инверсное преобразование

Прямое преобразование

Полученное представление и будет

ример.

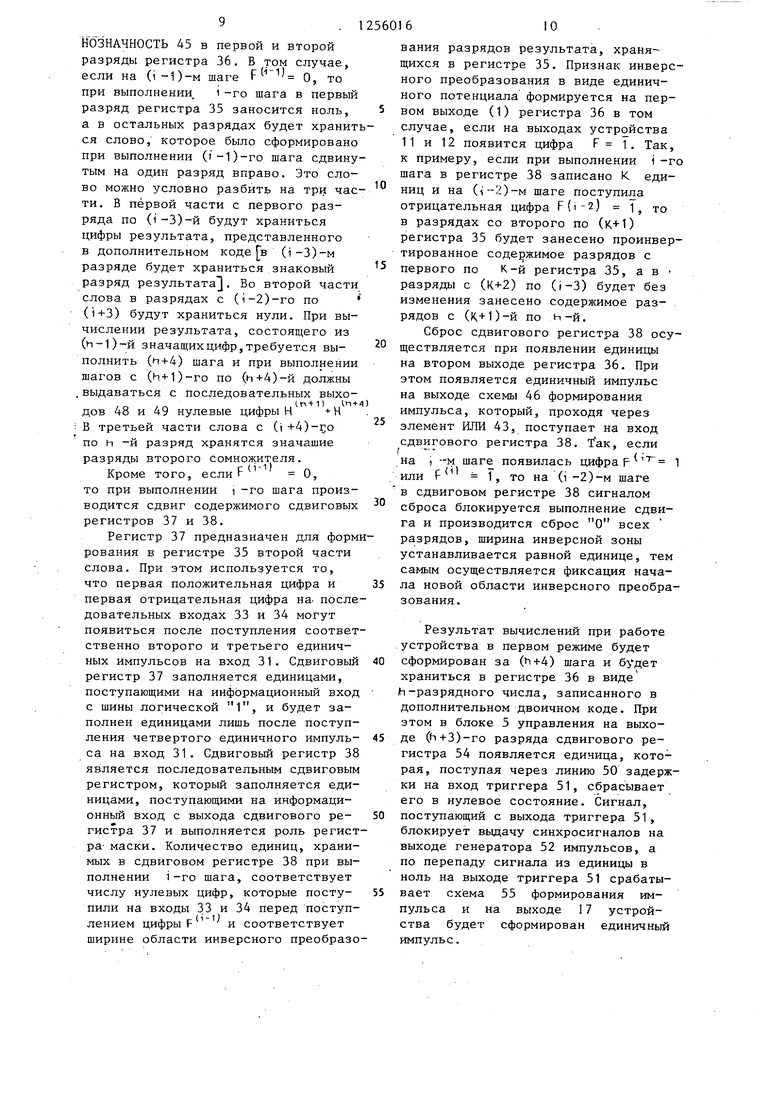

Исходное число:

Области инверсного преобразования

Дополнительный код:

При последовательном поступлении знакоразрядного кода, начиная со старших разрядов, необходимо последовательно формировать области инверсного преобразования по мере за- полнения регистра 1 разрядами, причем с поступлением отрицательной цифры Г осуществляется инверсное преобразование текущей области разрядов и фиксируется начало следующей области. При поступлении положительной цифры 1 инверсное преобразование текущей области не осуществля2560168

результата, и преобразование в дополнительный код по мере получения знакоразрядных цифр. Используется то, что при наличии знакоразрядного 5 представления числа (старшие разряды числа находятся слева) для получения дополнительного двоичного кода достаточно в исходном коде дописать слева ноль в дополнительном

разряде, а затем над разрядами,

стоящими левее каждой отрицательной единицы до ближайщей любой единицы включительно выполнить инверсные преобразования, а над остальными

прямые преобразования, согласно табл. 2.

Таблица 2

О

дополнительным кодом исходного числа.

Дополнительный разряд OoToOl 1 1о7о1 101

/ /

П О 1 11 101 1.00101

ется, но же, как и при отрицательной цифре 1, осуществляется фиксация начала новой области инверсного преобразования.

При выполнении i-го шага, когда появляется i-и единичный импульс на выходе 63 блока 5 управления, значения функций

p-(.,-0)-(Up

(f) -(i)f(

заносятся соответственно с выходом элемента ЗАПРЕТ 44 и элемента НЕРАВбЗНАЧНОСТЬ 45 в первой и второй азряды регистра 36. В том случае, сли на (i-1)-м шаге 0 то ри выполнении, i -го шага в первый азряд регистра 35 заносится ноль, а в остальных разрядах будет храниться слово, которое было сформировано при выполнении (i-l)-ro шага сдвинутым на один разряд вправо. Это слово можно условно разбить на три части. В первой части с первого разряда по (1-3)-й будут храниться цифры результата, представленного в дополнительном коде в (i-3)-M разряде будет храниться знаковый разряд результата. Во второй части слова в разрядах с (i-2)-ro по (i+3) будут храниться нули. При вычислении результата, состоящего из (и-1)-й значаш;ихцифр,требуется выполнить (и+4) шага и при выполнении шагов с (h+1)-ro по (и+4)-и должны выдаваться с последовательных выхоltT -1) l.n + l)

дов 48 и 49 нулевые цифры Н +Н в третьей части слова с (i +4)-г;о по h -и разряд хранятся значашие разряды второго сомножителя.

Кроме того, еслиF О, то при выполнении i -го шага производится сдвиг содержимого сдвиговых регистров 37 и 38.

Регистр 37 предназначен для формирования в регистре 35 второй части слова. При этом используется то, что первая положительная цифра и первая отрицательная цифра на- последовательных входах 33 и 34 могут появиться после поступления соответственно второго и третьего единичных импульсов на вход 31. Сдвиговый регистр 37 заполняется единицами, поступаюш;ими на информационный вход с шины логической 1, и будет заполнен единицами лишь после поступления четвертого единичного импульса на вход 31. Сдвиговый регистр 38 является последовательным сдвиговым регистром, который заполняется единицами, поступающими на информационный вход с выхода сдвигового регистра 37 и выполняется роль регистра- маски. Количество единиц, хранимых в сдвиговом регистре 38 при выполнении i-го шага, соответствует числу нулевых цифр, которые поступили на входы 33 и 34 перед поступлением цифры и соответствует ширине области инверсного преобразо

вания разрядов результата, хранящихся в регистре 35. Признак инверсного преобразования в виде единичного потенциала формируется на первом выходе (1) регистра 36 в том случае, если на выходах устройства 11 и 12 появится цифра F 1. Так, к примеру, если при выполнении i -го шага в регистре 38 записано К единиц и на (2)-м шаге поступила отрицательная цифра F(i-2) то в разрядах со второго по (к+1) регистра 35 будет занесено проинвер- тированное соде1:1жимое разрядов с первого по К-и регистра 35, а в разряды с (К+2) по (i-3) будет без изменения занесено содержимое разрядов с (К+1)-й по h-й.

Сброс сдвигового регистра 38 осуществляется при появлении единицы на втором выходе регистра 36. При этом появляется единичный импульс на выходе схемы 46 формирования импульса, который, проходя через элемент ИЛИ 43, поступает на вход сдвигового регистра 38. , если на i -м шаге появилась цифра F 1 или f Т, то на (i -2)-м шаге в сдвиговом регистре 38 сигналом сброса блокируется выполнение сдвига и производится сброс О всех разрядов, ширина инверсной зоны устанавливается равной единице, тем самым осуществляется фиксация начала новой области инверсного преобразования.

Результат вычислений при работе .устройства Б первом режиме будет

сформирован за (h+4) шага и будет храниться в регистре 36 в виде h-разрядного числа, записанного в дополнительном двоичном коде. При этом в блоке 5 управления на выходе (h+3)-ro разряда сдвигового регистра 54 появляется единица, которая, поступая через линию 50 задержки на вход триггера 51, сбрасывает его в нулевое состояние. Сигнал,

поступающий с выхода триггера 51, блокирует выдачу синхросигналов на выходе генератора 52 импульсов, а по перепаду сигнала из единицы в ноль на выходе триггера 51 срабатывает схема 55 формирования импульса и на выходе I7 устройства будет сформирован единичный импульс.

3

разрядный сдвиговый регистр 39 во второй и первьш разряды, соответственно, заносятся знаковый и старший значащий разряды второго сомножителя, а остальные (h-2) разряда заносятся в регистр 35, где h- старший разряд. В младшие 2 и 1 разряды регистра 35 с шины логического О заносятся нули..

Время Тд соответствует времени переходного процесса при установке регистров и триггеров устройства.

Далее при работе в первом режиме в блоке 5 управления через время Т + Tj, обусловленное срабатыванием линии 58 задержки и триггера 51, производится запуск генератора импульсов 52. Синхроимпульсы с выхода генератора импульсов 52 через коммутатор 53, который управляется сигналом, поступающим на вход 9 устройства, начинают поступать на вход регистра 54, выход 64 и через линию 56 задержки, время задержки которой Т - на выход 63. Период следования синхроимпульсов на выходе генератора импульсов 52 равен Т,

В течение времени Т Т + Т +Т выполняется первый шаг вычисления, при котором производится умножение первого сомножителя на старшую цифру второго сомножителя и сложение этой величины с удвоенным значением числа, хранящегося в регистре 2, которое первоначально равно нулю. При этом выполняются следующие условия: Т, +TpV , Тз Ту,. , где Т - время срабатывания параллельного сумматора 3 для случая когда изменяется число, поступающее в параллельный сумматор 3 по первому информационному входу ;Т,- время срабатывания блока 13 управления параллельным сумматором;Тр - время, в течение которого сигнал на информационном входе регистра (триггера) не должен изменяться; это необходимо для устойчивой работы регистров (триггеров).

При работе устройства во втором режиме на выходы коммутатора 53 пропускаются синхроимпульсы, поступающие на вход 6 устройства. Это позволяет проводить внешнюю синхронизацию работы устройства для случая, когда предложенное устройство работает совместно с другими устройствами, в которых производится обработка

560164

информации, поступающей старшими разрядами вперед. Значащие цифры второго сомножителя во втором режиме поступают на входы 15 и 16 задер- 5 жанными по отношению синхроимпульсов, появляющихся на выходе 64, на время срабатывания регистров Тр .На -м шаге, который начинается при поступлении 1-го синхроимпульса

на выходы 63 и 64 блока 5 управления,- результат, полученный на (i-l)-M шаге, заносится в регистр 2, последовательный сумматор 4 и блок 14 прямого и обратного преобразования г

5 знакоразрядного кода в дополнительный код, производится умножение первого сомножителя на (д+О-ю цифру второго сомножителя и сложение полученной величины с удвоенньм

20 значением результата ((-1)-го шага, занесенного в регистр 2, последовательный сумматор 4 и блок 14 прямого и обратного преобразования знакоразрядного кода в дополнительный

25

код.

Для обеспечения функционирования параллельного сумматора 3 в устройстве производится преобразование первого сомножителя, поступающего в регистр 1 дополнительном двоичном коде, в параллельный знакораз- рядный код, который поступает на второй информационный вход параллельного сумматора 3.

Формирование цифр знакоразрядного кода, поступающих на второй информационный вход параллельного сумматора 3, производится по алго- ритму Бута, так ь ь ,bj-bj, где bj и bj J- значения соответственно J-го и (j-l)-ro разрядов регистра 1 (Ь - значение знакового разряда, Ь, значение старшего значащего разряда).

К примеру, число 1,01JO1001 преобразуется к виду 1,10f11011. Управление работой параллельного сумматора 3 осуществляется сигналами, поступающими с выходов блока управ- ления параллельным сумматором 13, в котором происходит преобразование сигналов, поступающих с выходов 48 и 49 блок прямого и обратного преобразования знакоразрядного кода в дополнительный код, или с входов 15 и 16 устройства.

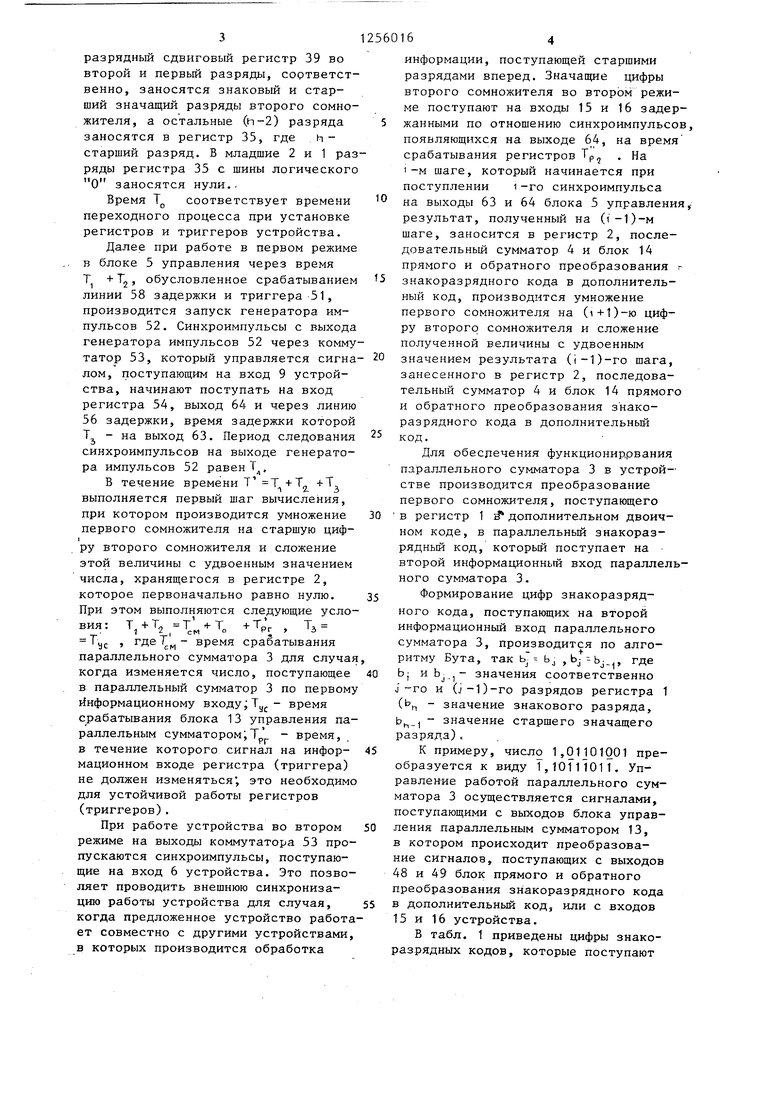

В табл. 1 приведены цифры знако- разрядных кодов, которые поступают

на входы 20 и 21 блока управления параллельным сумматором 13 с выходов 48 и 49 блока 14 преобразования кодов и последовательных входов 15, 16 устройства и соответствую

О 1 О

1

о о 1 о

о 1 о о

Управление работой коммутатора 18 производится сигналом, поступаю- щим на вход 9 устройства. При работе устройства в первом режиме на выход коммутатора 18 пропускаются сигналы, поступающие с выходов 48 и 49 блока 14 прямого и обратного преобразования знакоразрядного кода в дополнительный код, а во втором режиме на выход коммутатора 18 поступают сигналы с входов 15 и 16 устройства,

Результат на выходе параллельного сумматора 3 формируется в виде параллельного знакоразрядного кода состоящего из (и+1)-й цифры. Младшие и цифр результата С + С|.поступа- ют на входы регистра 2, а цифра С,., с выхода переносов старшего, разряда параллельного сумматора 3 поступает на входы положительного разряда первого и второго onepiaH- дов последовательного сумматора 4, Выход регистра 2 соединен с входом

параллельного сумматора 3 так, что (.--1)

цифра С- результата, сформированного на (i-l)-M шаге и занесенного в регистр 2 при выполнении i-го шага, поступает на вход параллельного сумматора 3, как цифра

щие этим кодам сигналы, формируемые на выходе блока 13 управления параллельным сумматором, а также операции, выполняемые в параллельном 5 сумматоре 3.

Таблица 1

1

о о

1

с А С Л-В С А + В

д. , а цифра С f, , с выхода регистра 2 поступает на входы отрицательного разряда первого и второго операндов последовательного сумматора 4, Это позволяет на t -м шаге сформировать в устройстве величины н. 6 или ,. , где G, - циф- ры второго сомножителя, который хранится в блоке 14 прямого и обратного преобразования знакоразрядного кода в дополнительный кoдj Н- .- цифра второго сомножителя, которая поступает в виде последовательного кода на входы 15 и 16 устройства С и - соответственно суммы частных произведений, сформирован ных на (i-l)-M и i -м шагах.

В блоке 14 прямого и обратного преобразования знакоразрядного кода в дополнительный код второй сомножитель, занесенный в регистры 35 и 39 при выполнении последовательных сдвигов, выдается на выходы 48 и 49 в виде последовательного знакоразрядного кода. При этом используется алгоритм Бута, так, на i-м шаге в регистре 39 в первом и во втором разрядах будут занесены соответственно К., .

гг - 1 1

„,, раз11

. время вычислений в предлагаемом устройстве при работе в первом режиме

(т;„.).(п.з).т,

«(h-4) + (+3). .

().

pr

При работе во втором режиме результат вычислений в виде h -разрядного числа, записанного в блоке 14 прямого и обратного преобразования знакоразрядного кода в дополнительный код, будет сформирован после поступления (h+4)-ro синхроимпулса поступающего на вход 6 устрой- . Но в этом режиме вычисления мгут продолжаться и дальше. Остановка устройства произойдет только по окончании поступления сигналов на синхронизирующий вход 6 устройства.

Формула изобретени

1. Устройство для умножения, содержащее два регистра, параллельный сумматор, последовательньш сумматор информационная шина устройства подключена к информационному входу первого регистра, информационный вход второго регистра соединен с выходом параллельного сумматора, первый информационный вход которого соединен с выходом (-1) младших разрядов второго регистра (h- разряность второго регистра), положительный выход старшего разряда которого соединен с входом положительного разряда первого операнда последова- тельного сумматора, вход положительного разряда второго операнда которого соединен с положительным выходом переноса параллельного сумматора, выходы последовательного сумма- тора соединены с последовательными выходами устройства, о т л и ч а ю щ е е с я тем, что, с целью увеличения быстродействия и расширения функциональных возможностей за счет обеспечения возможности работы с дополнительными кодами, оно содержит блок управления, блок управления Параллельным сумматором, блок прямого и обратного преобразования знакоразрядного кода в дополнительный код, отрицательный выход переноса параллельного сумматора соеди1256016

12

0

5

0

нен с входом отрицательного разряда втопого операнда последовательного сумматора, вход отрицательного разряда первого операнда которого соединен с отрицательным выходом старшего разряда второго регистра, первый и второй информационные входы блока управления параллельным сумматором соединены с последовательными входами множителя устройства, параллельный вход множителя блока прямого и обратного преобразования знакоразрядного кода и дополнительный соединен с входной шиной устройства, синхронизирующий вход которого соединен с первым входом блока управления, второй вход которого подключен к входу запуска устройства, последовательные входы произведения блока прямого и обратного преобразования знакоразрядного кода в дополнительный код соединены с последовательным выходом устройства, параллельный выход блока прямого и обратного преобразования знакоразрядного кодд в дополнительный код соединен с параллельным выходом устройства, последовательные выходы множителя блока прямого и обратного преобразования знакоразрядного кода в дополнительный код соединены- с третьим и четвертым информационными входами блока управления параллельным сумматором, вход управления режимом работы которого соединен с третьим входом блока управления и входом управления режимом работы устройства, выход блока управления

параллельным сумматором соединен с управляющим входом режима работы

параллельного сумматора, первый выход блока управления соединен с входами сброса первого и второго регистров, блока прямого и обратного преобразования знакоразрядного кода в дополнительный код, второй выход блока управления соединен с входами синхронизации второго регистра, последовательного сумматора и блока прямого и обратного преобразования знакоразрядного кода в дополнительный код, вход управления сдвигом которого соединен с третьим выходом блока управления, четвертый выход которого соединен с выходом Конец работы устройства, выход i-го разряда первого регистра соединен с отрицательным входом i -го раз13. 1

ряда и положительным входом (i+1)-ro разряда второго информационного входа параллельного сумматора (i - 1,...h), отрицат ельньй вход первого разряда B-foporo входа парал- лельного сумматора соединен с шиной логического нуля.

2. Устройство по п. 1, отличающееся тем, что блок управления содержит два блока форми- рования импульсов, три элемента задержки, триггер, генератор импульсов, коммутатор, регистр, первый вход блока управления соединен с первым информационным входом коммут тора, второй информационньй вход которого подключен к выходу генера- .тора импульсов, вход которого сое- динен с выходом триггера и входом первого блока формирования импуль- сов, второй вход блока управления подключен к входу второго блока формирования импульсов, выход которого соединен с первым выходом блока управления, входом сброса регистра и через первый элемент задержки с входом установки триггера, вход сброса которого соединен через второй элемент задержки с выходом старшего разряда регистра, информа- ционный вход которого соединен с шиной логической единицы, а вход управления сдвигом подключен к выходу коммутатора, через третий элемент задержки к второму выходу бло- ка управления и к третьему выходу блока управления, третий вход блока

6 14

управления соединен с управляющим входом коммутатора, а четвертый выход блока управления подключен к выходу первого блока формирования импульсов.

3. Устройство по п. 1, о т л и чающееся тем, что блок управления параллельным сумматором содержит коммутатор, два элемента ЗАПРЕТ, элемент НЕРАВНОЗНАЧНОСТЬ и элемент ЭКВИВАЛЕНТНОСТЬ, первый и второй информационные входы коммутатора соединены соответственно с первым и вторым информационными входами блока управления параллельным- сумматором, третий и четвертый информационные входы которого подключены к третьему и четвертому информационным входам коммутатора, первый выход которого соединен с управляющим входом первого элемента ЗАПРЕТ, информационным входом второго элемента ЗАПРЕТ и первыми входами элементов ЭКВИВАЛЕНТНОСТЬ и НЕРАВНОЗНАЧНОСТЬ, второй выход коммутатора соединен с управляющим входом второго элемента ЗАПРЕТ, информационным входом первого элемента ЗАПРЕТ и вторыми входами элементов ЭКВИВАЛЕНТНОСТЬ И НЕРАВНОЗНАЧНОСТЬ, выходы первого и второго элементов ЗАПРЕТ,

. элементов ЭКВИВАЛЕНТНОСТЬ и НЕРАВНОЗНАЧНОСТЬ соединены с выходом блока управления параллельным сумматором, вход управления режимом работы кото- ррго соединен с управляющим входом коммутатора.

фиг.З

Jff

SZ S3 64

59SO

Pl/l.4

РеДактор П.Коссей

Составитель А.Жижин Техред Л. Сердюкова

Заказ 4824/48

Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор С.Шекмар

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1987 |

|

SU1472899A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Преобразователь последовательного знакоразрядного кода в дополнительный двоичный код | 1983 |

|

SU1113796A1 |

| Арифметический расширитель | 1988 |

|

SU1566341A1 |

| Устройство для умножения | 1989 |

|

SU1612295A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1988 |

|

SU1640709A1 |

| Арифметический расширитель | 1989 |

|

SU1661758A1 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| Устройство для умножения | 1979 |

|

SU868751A1 |

| Интегрирующее устройство | 1990 |

|

SU1727122A1 |

Изобретение относится к вычислительной технике и может применяться в ЦВМ как арифметический расширитель. Цель изобретения - увеличение быстродействия и расширение функциональных возможностей за счет работы с дополнительными кодами. Поставленная цель достигается тем, что в устройство для умножения, содержащее два регистраj параллельный сумматор, последовательный сумматор с соответствующими связями, введены блок управления, блок управления параллельным сумматором, блок прямо- То и обратного преобразования знако- разрядного кода в дополнительный код с соответствующими связями, 2 з.п. ф-лы, 5 ил. с СЛ % Од

| Карцев М.А., Брик В.А | |||

| Вычислительные системы .и синхронная арифметика | |||

| М.: Радио и связь, 1981 | |||

| Устройство для умножения | 1981 |

|

SU1005035A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-07—Публикация

1984-12-05—Подача