| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивная система передачи дискретных сообщений | 1986 |

|

SU1497755A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Устройство контроля дискретных каналов | 1989 |

|

SU1626406A1 |

| АППАРАТУРА ДИСТАНЦИОННОГО ВВОДА ДЛЯ ПРОГРАММИРОВАНИЯ ДИСТАНЦИОННЫХ ВЗРЫВАТЕЛЬНЫХ УСТРОЙСТВ СНАРЯДОВ РЕАКТИВНЫХ СИСТЕМ ЗАЛПОВОГО ОГНЯ | 2003 |

|

RU2219488C1 |

| Устройство передачи и приема шумоподобных сигналов | 1989 |

|

SU1707771A1 |

| Устройство контроля дискретных каналов | 1989 |

|

SU1707770A1 |

| УСТРОЙСТВО КОНТРОЛЯ ДИСКРЕТНЫХ КАНАЛОВ | 1991 |

|

RU2017334C1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1695372A1 |

| Видеоконтрольное устройство для дефектоскопии сварных соединений | 1985 |

|

SU1506476A1 |

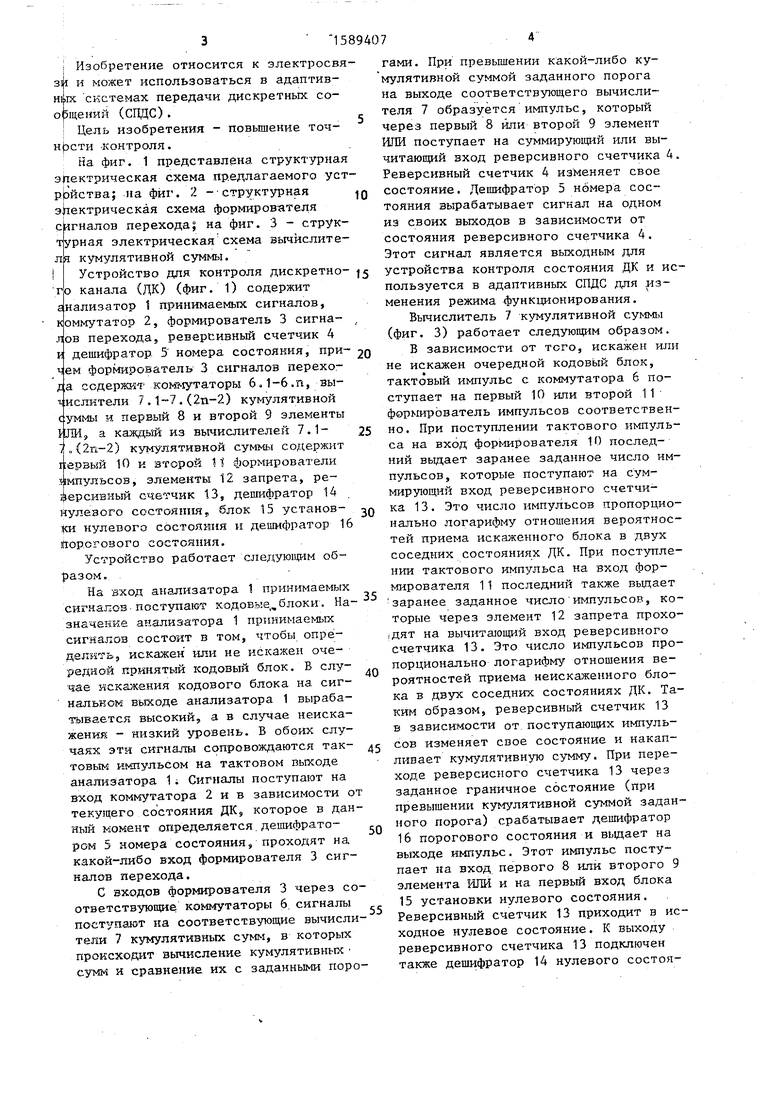

Изобретение относится к электросвязи. Цель изобретения - повышение точности контроля. Устройство содержит анализатор 1 принимаемых сигналов, коммутатор 2, формирователь 3 сигналов перехода, реверсивный счетчик 4 и дешифратор 5 номера состояния. По оценке входного сигнала в анализаторе 1 формирователь 3 вычисляет кумулятивные суммы, влияющие на содержимое реверсивного счетчика 4, отражающее состояние дискретного канала и дешифрируемое дешифратором 5. Устройство отличается выполнением формирователя 3 и входящих в него вычислителей кумулятивных сумм. 2 з.п. ф-лы, 3 ил.

Фиг.1

3 1589407

I Изобретение относится к электросвя- зф и может использоваться в адаптив- Hifix системах передачи дискретных со- о щений (СПДС).5

I Цель изобретения - повышение точ- HJDCTH -контроля.

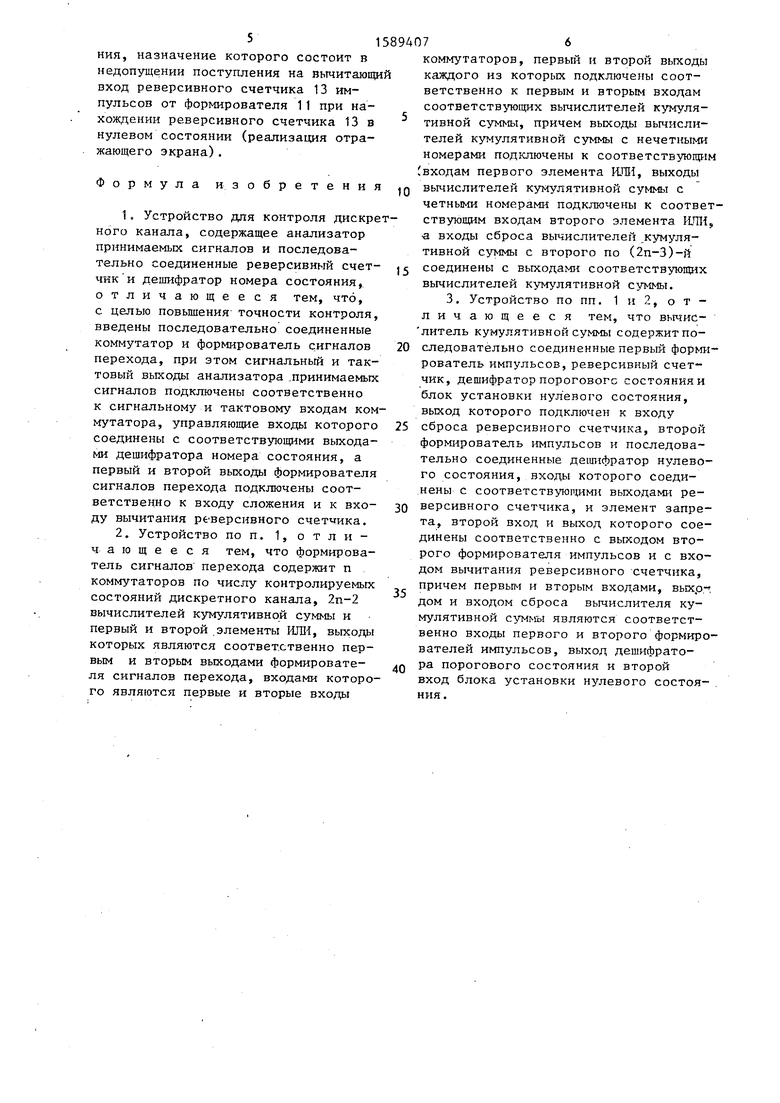

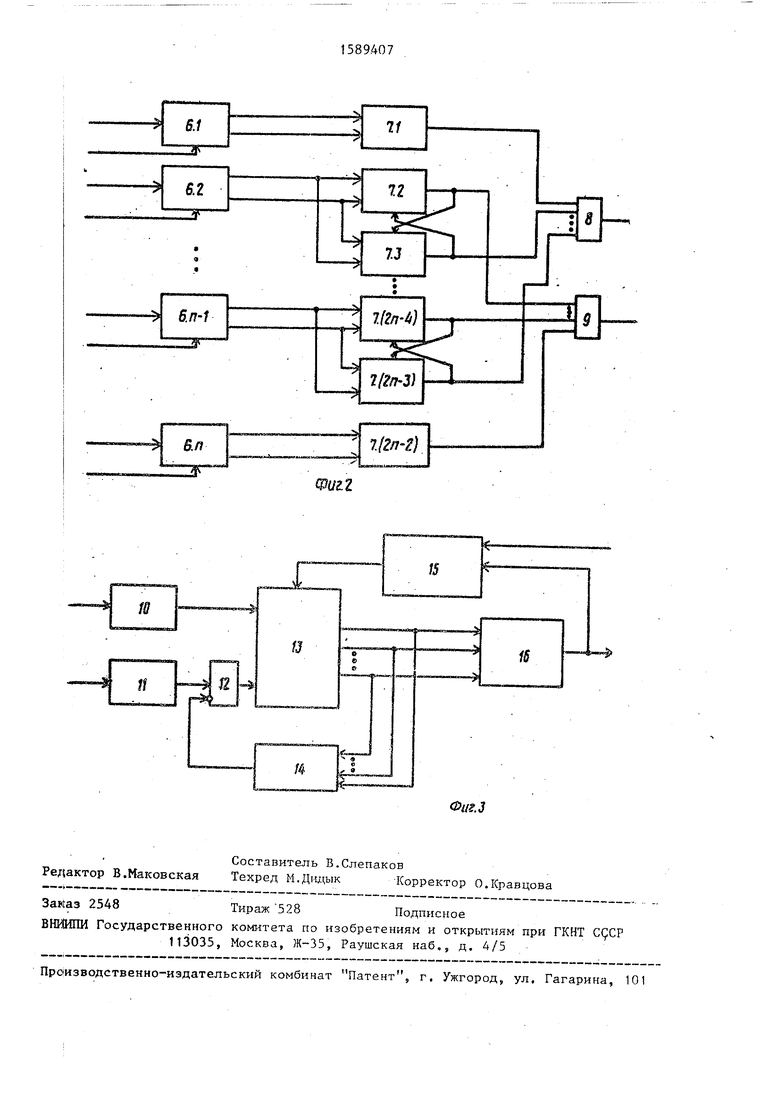

На фиг. 1 представлена структурная электрическая схема предлагаемого уст- р|ойства; на фиг. 2 - структурная ц эЬектрическая схема формирователя сигналов перехода; на фиг. 3 структКгрная электрическая схема вычислителя кумулятивной суммы.

гами. При превышении какой-либо ку- мулятивной суммой заданного порога на выходе соответствующего вычислителя 7 образуется импульс, который через первый 8 или второй 9 элемент ИЛИ поступает на суммируюищй или вычитающий вход реверсивного счетчика 4, Реверсивный счетчик 4 изменяет свое состояние. Дешифратор 5 номера состояния вырабатывает сигнал на одном из своих выходов в зависимости от состояния реверсивного счетчика 4. Этот сигнал является выходным для

Л кумулятивной суммы.JTOT СИГПШ MbJineiun м-

I Устройство для контроля дискретно- 15устройства контроля состояния ДК и исгр канала (ДК) (фиг. 1) содержитпользуется в адаптивных СПДС для из .(-т т у-4млт х о Лч-чгч 1ГТТТ;ГГ Н М П ТИЯ ИМЯ .

нализатор 1 принимаемых сигналов, коммутатор 2, формирователь 3 сигна- , лов перехода, реверсивный счетчик 4 и дешифратор 5 номера состояния, при- 20 чем формирователь 3 сигналов перехода содержит коммутаторь5 6.1-б.п, вы- г ислители 7.1-7.(2п-2) кумулятивной суммы и первый 8 и второй 9 элементы YJM, а каждый из вычислителей 7.1- 25 io(2n-2) кумулятивной суммы содержит г ервый 10 и второй 11, формирователи 4мпульсов, элементы 12 запрета, реверсивный счетчик 13, дешифратор 14 . нулевого состояшш, блок 15 установ- 0 ки нулевого состояния и дешифратор 16 йор.огового состояния.

Устройство работает следую1цим образом..

На вход анализатора t принимаемых

менения режима функционирования.

Вычислитель 7 кумулятивной сумм1л1 (фиг. 3) работает следующим образом.

В зависимости от того, искажен или не искажен очередной кодовый блок, тактовый импульс с коммутатора 6 поступает на первый Ю или второй 11 формирователь импульсов соответственно. При поступлении тактового импульса на вход формирователя 10 последний вьщает заранее заданное число импульсов, которые поступают на суммирующий вход реверсивного счетчика 13. Это число импульсов пропорционально логарифму отношения вероятностей приема искаженного блока в двух соседних состояниях ДК. При поступлении тактового импульса на вход формирователя 11 последний также вьщает

па вход ancUlilJa.1 Ufa.,iJ..-.JT

сигналов, поступают кодовые,,блоки. На- заранее заданное число импульсов, козначение анализатора 1 принимаемых сигналов состоит в том, чтобы определить, искажен или не искажен очередной принятый кодовый блок. В слу- Q чае искажения кодового блока на сигнальном выходе анализатора 1 вырабатывается высокий, а в случае неиска- женик - низкий уровень. В обоих случаях этн сигналы сопровождаются так- 45 товым импульсом на тактовом вькоде анализатора 1; Сигналы поступают на вход коммутатора 2 и в зависимости от текущего состояния ДК, которое в данный момент определяется.дешифрато- Q ром 5 номера состояния, проходят на какой-либо вход формирователя 3 сигналов перехода.

С входов формирователя 3 через соответствующие коммутаторы 6. сигналы поступэлот на соответствующие вычислители 7 кумулятивных сумм, в которых происходит вычисление кумулятивных сумм и сравнение их с заданными пороторые через элемент 12 запрета проходят на вычита ощий вход реверсивного счетчика 13. Это число импульсов пропорционально логарифму отношения вероятностей приема неискаженного блока в двух соседних состояниях ДК. Таким образом, реверсивный счетчик 13 в зависимости от поступающих импульсов изменяет свое состояние и накапливает кумулятивную сумму. При переходе реверсисного счетчика 13 через заданное граничное состояние (при превышении кумулятивной суммой заданного порога) срабатывает дешифратор 16 порогового состояния и выдает на выходе импульс. Этот импульс поступает на вход первого 8 или второго 9 элемента ИЛИ и на первый вход блока 15 установки нулевого состояния. Реверсивный счетчик 13 приходит в исходное нулевое состояние. К выходу реверсивного счетчика 13 подключен также дешифратор 14 нулевого состоягами. При превышении какой-либо ку- мулятивной суммой заданного порога на выходе соответствующего вычислителя 7 образуется импульс, который через первый 8 или второй 9 элемент ИЛИ поступает на суммируюищй или вычитающий вход реверсивного счетчика Реверсивный счетчик 4 изменяет свое состояние. Дешифратор 5 номера состояния вырабатывает сигнал на одном из своих выходов в зависимости от состояния реверсивного счетчика 4. Этот сигнал является выходным для

JTOT СИГПШ MbJineiun м-

устройства контроля состояния ДК и

пользуется в адаптивных СПДС для из.(-т т у-4млт х о Лч-чгч 1ГТТТ;ГГ Н М П ТИЯ ИМЯ .

менения режима функционирования.

Вычислитель 7 кумулятивной сумм1л1 (фиг. 3) работает следующим образом.

В зависимости от того, искажен или не искажен очередной кодовый блок, тактовый импульс с коммутатора 6 поступает на первый Ю или второй 11 формирователь импульсов соответственно. При поступлении тактового импульса на вход формирователя 10 последний вьщает заранее заданное число импульсов, которые поступают на суммирующий вход реверсивного счетчика 13. Это число импульсов пропорционально логарифму отношения вероятностей приема искаженного блока в двух соседних состояниях ДК. При поступлении тактового импульса на вход формирователя 11 последний также вьщает

JT

заранее заданное число импульсов, козаранее заданное число импульсов, которые через элемент 12 запрета проходят на вычита ощий вход реверсивного счетчика 13. Это число импульсов пропорционально логарифму отношения вероятностей приема неискаженного блока в двух соседних состояниях ДК. Таким образом, реверсивный счетчик 13 в зависимости от поступающих импульсов изменяет свое состояние и накапливает кумулятивную сумму. При переходе реверсисного счетчика 13 через заданное граничное состояние (при превышении кумулятивной суммой заданного порога) срабатывает дешифратор 16 порогового состояния и выдает на выходе импульс. Этот импульс поступает на вход первого 8 или второго 9 элемента ИЛИ и на первый вход блока 15 установки нулевого состояния. Реверсивный счетчик 13 приходит в исходное нулевое состояние. К выходу реверсивного счетчика 13 подключен также дешифратор 14 нулевого состояния, назначение которого состоит в недопущении поступления на вычитающи вход реверсивного счетчика 13 импульсов от формирователя 11 при нахождении реверсивного счетчика 13 в нулевом состоянии (реализация отражающего экрана).

Формула изобретения

коммутаторов, первый и второй выходы каждого из которых подключены соответственно к первым и вторым входам соответств:,тощих вычислителей кумулятивной суммы, причем выходы вычислителей кумулятивной суммы с нечетными номерами подключены к соответствующим (входам первого элемента ИЛИ, выходы

д вычислителей кумулятивной суммы с

четными номерами подключены к соответствующим входам второго элемента l-UTHj а входы сброса вычислителей кумулятивной суммы с второго по (2п-3)-й

J5 соединены с выходами соответствующих вычислителей кумулятивной суммы.

5 сброса реверсивного счетчика, второй формирователь импульсов и последовательно соединенные де1т1фратор нулевого состояния, входы которого соединены с соответствуюрдами выходами ре0 версивного счетчика, и элемент запрета, второй вход и выход которого соединены соответственно с выходом второго формирователя импульсов и с входом вычитания реверсивного счетчика, причем первым и вторым входами, вьоср.-г дом и входом сброса вычислителя кумулятивной суммы являются соответственно входы первого и второго формирователей импульсов, выход дешифрато- Q ра порогового состояния и второй

вход блока установки нулевого состояния.

71-,

| Устройство контроля дискретных каналов | 1983 |

|

SU1142894A1 |

Авторы

Даты

1990-08-30—Публикация

1988-11-21—Подача