1

(21)4161049/2,6-09

(22)15.12.86

(46) 30.07.89. Бюл. 28 (7f) Ленинградский электротехнический институт связи им. М.А.Воич- „ Бруевича

72) Р.И,Виноградов и А.Н.Семенюта .(53) 621.394.6(088.8)

(56) Изделия paдиoпpo пIшeннocти, Каталог. Сер. Аппаратура передачи данных, т. II; Аппаратура передачи данных Аккорд - 1200, М. 1970,

с. 14.

(54) АДАПТИВНАЯ СИСТЕМА ПЕРЕДАЧИ

ДИСКРЕТНЫХ СООБЩЕНИЙ

(57)Изобретение относится к электросвязи. Цель изобретения - увеличение пропускной способ1 ости. Адаптивная система передачи дискретных сообщений содержит передающую и приемную стороны, которые работают в следующих режимах: режиме начального фазирования, режиме передачи (приема) данных, режиме повторения блока данных, режиме промежуточного фазирования и режиме Конец передачи. Цель достигается введением на передающей стороне блока выбора длины кода, который определяет дпину кода и вид комбинации фазирования, используемой в течение передачи сообщения. Система по п. 2 ф-лы отличается выполнением блока выбора длины кода. 1 з.п. ф-лы, 3 ил.

(О

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство асинхронного сопряжения цифровых сигналов | 1979 |

|

SU860326A1 |

| Система передачи хронометрической информации | 1985 |

|

SU1249561A1 |

| Система передачи и приема дискретной информации | 1980 |

|

SU944146A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1986 |

|

SU1401629A1 |

| Устройство для кодирования и декодирования сигналов в системах передачи цифровых данных | 1980 |

|

SU1046959A1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1987 |

|

SU1552388A2 |

| Устройство асинхронного ввода-вывода синхронной информации | 1982 |

|

SU1053307A1 |

| Устройство асинхронного ввода-вывода синхронной информации | 1979 |

|

SU862373A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1982 |

|

SU1072278A1 |

Изобретение относится к электросвязи. Цель изобретения - увеличение пропускной способности. Адаптивная система передачи дискретных сообщений содержит передающую и приемную стороны, которые работают в следующих режимах: режиме начального фазирования, режиме передачи (приема) данных, режиме повторения блока данных, режиме промежуточного фазирования и режиме "Конец передачи". Цель достигается введением на передающей стороне блока выбора длины кода, который определяет длину кода и вид комбинации фазирования, используемой в течение передачи сообщения. Система по п. 2 ф-лы отличается выполнением блока выбора длины кода. 1 з.п.ф-лы, 3 ил.

Изобретение относится к электросвязи и может быть использовано для передачи данных.

Цель изобретения - увеличение пропускной способности системы.

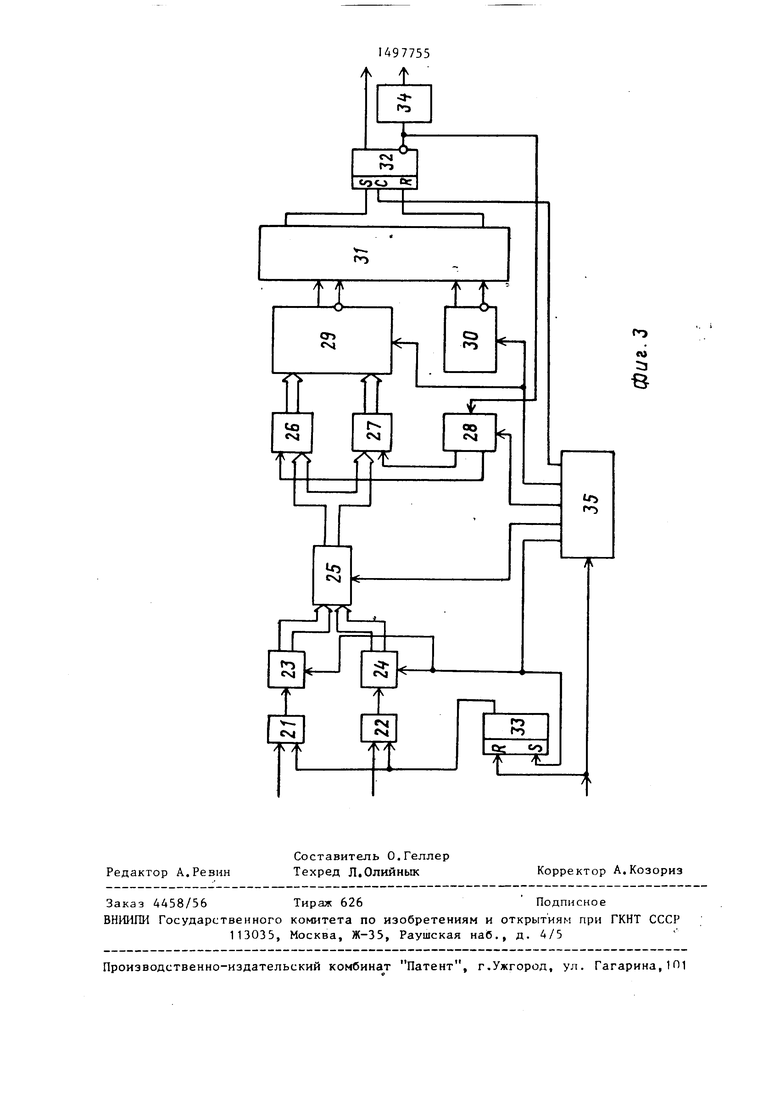

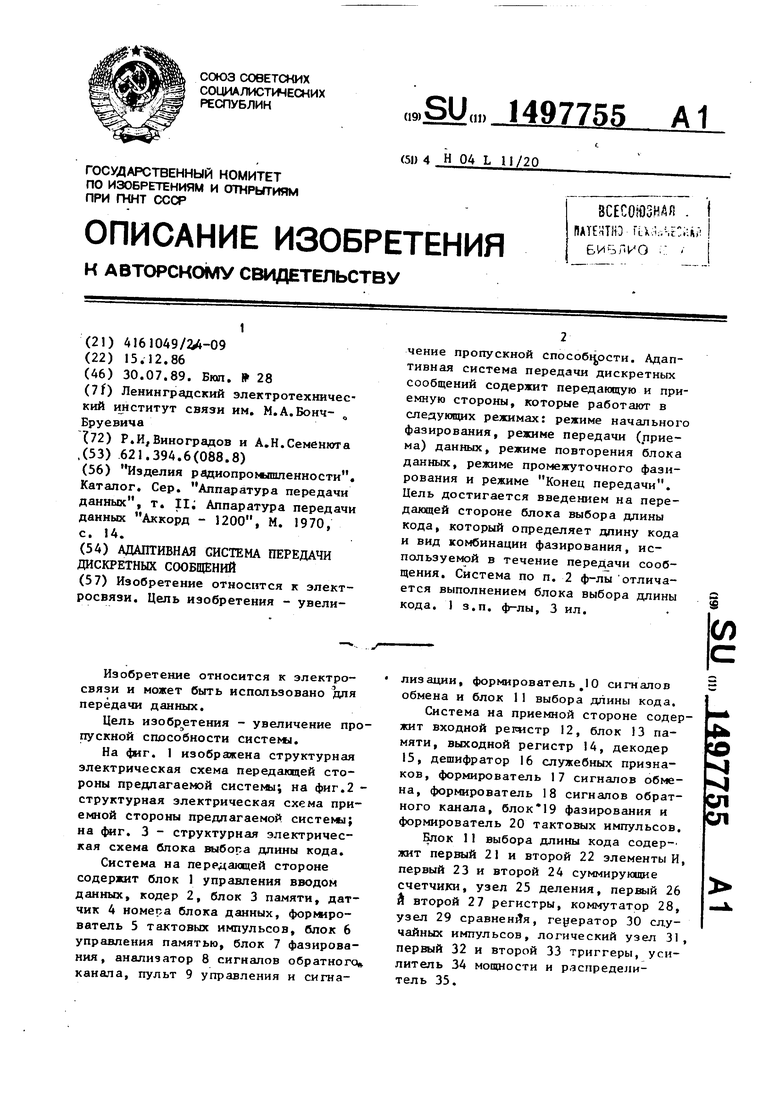

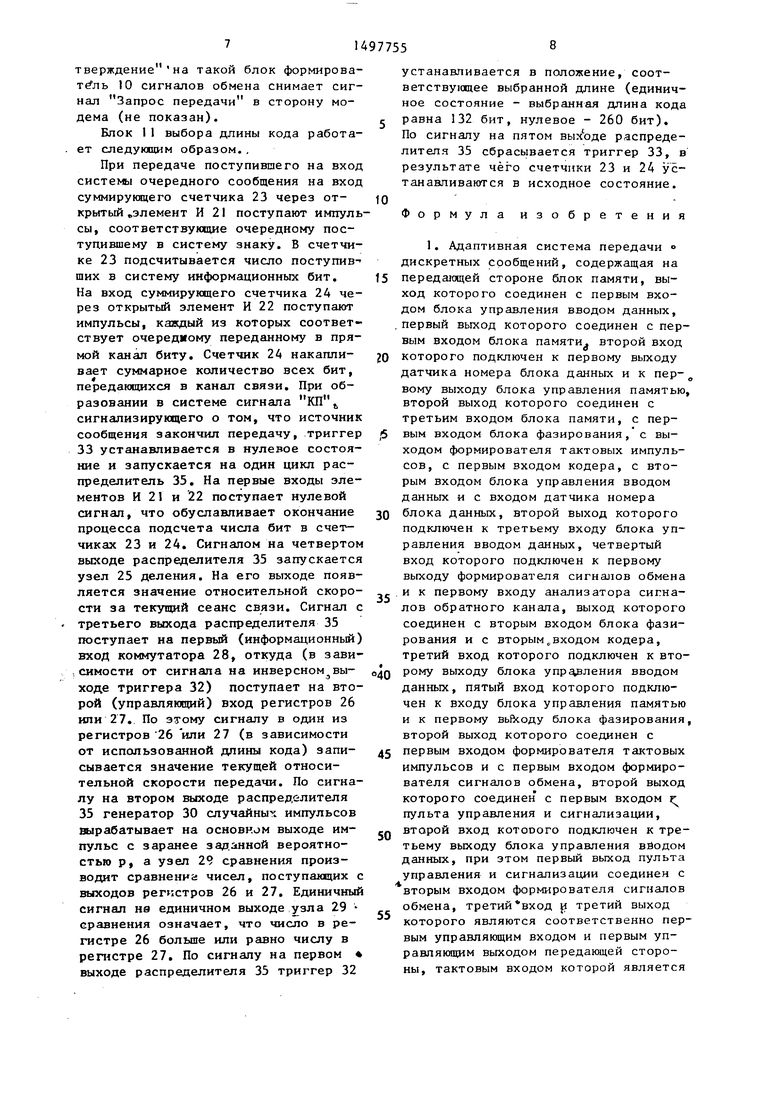

На фиг. 1 изображена структурная электрическая схема передамцей стороны предлагаемой системы; на фиг.2 - структурная электрическая схема приемной стороны предлагаемой системи; на фиг. 3 - структурная электрическая схема блока выбора длины кода.

Система на перрдакщей стороне содержит блок 1 управления вводом данных, кодер 2, блок 3 памяти, датчик 4 номера блока данных, форкмро- ватель 5 тактовых импульсов, блок 6 управления памятью, блок 7 фазирования, анализатор 8 сигналов обратного канала, пульт 9 управления и сигнализации, формирователь ,10 сигналов обмена и блок 11 выбора длины кода.

Система на приемной стороне содержит входной регистр 12, блок 13 памяти, выходной регистр 14, декодер 15, дешифратор 16 служебных признаков, формирователь 17 сигналов обмена, формирователь 18 сигналов обратного канала, фазирования и формирователь 20 тактовых импульсов.

Блок I1 выбора длины кода содер- жит первый 21 и второй 22 элементы И, первый 23 и второй 24 суммирующие счетчики, узел 25 деления, первый 26 и второй 27 регистры, коммутатор 28, узел 29 сравнения, генератор 30 случайных импульсов, логический узел 31, первый 32 и второй 33 триггеры, усилитель 34 и рсэспредели- тель 35.

4iii СО СП

ел

Система работает следующим образом.

В начале каждого сеанса связи адаптивная система передачи дискретных сообщений устанавливается в режим начального фазирования. В режиме начального фазирования передающая сторона передает приемной стороне информацию об используемой для передачи поступившего на вход системы сообщеТ|ия длине кода, устанавливается синхронность и синфазность работы приемной и передающей сторон. С этой целью в адаптивную систему передачи дискретных сообщений введено два типа фазирующих комбинаций. Фазирующая комбинация со служебным признаком 0101 означает, что в системе будет использоваться длина блока, равная 260 бит, фазирующая комбинация со служебным признаком 1111 означает, что в системе будет использоваться длина кода, равная 132 бит. Длийу кода и вид комбинации фазирования, испольэ уемой в течение передачи сообщения, определяет блок 11 выбора длины кода,

В передающей части в режиме начального фазирования из блока 7 фазирования во входной регистр (не показан) блока 1 управления вводом данных записывается соответствующий выбранной длине кода служебный признак сигнала синхронизации, который через кодер 2 поступает в прямой канал связи.

Кодирование заключается в получении остатка от деления двоичного числа (признака сигнала синхронизации) на образующий полином циюгичесKot o кода. Остаток состоит из шестнадцати символов, которые передаются вслед за делимым числом в модем (не показан) и представляет собой комби- нацию синхронизации.

В режиме начального фазирования состояние обратного канала не контролируется. После передачи сигнала синхронизации передаюш.я сторона переходит в режим передачи данных. От оконечного оборудования данных (СОД) (не пока ано) поступают два блока данньг ., которые передаются в канал связи и вводятся в блок 3 памяти.

На приемной стороне в режиме начального фазирования осуцестпляется

0

0

5

0

поиск фазирующей комбинации, определяющей длину кода для передачи поступившего на вход системы сообщения. Для этого на приемной стороне в режиме начального фазирования декодер 15 работает как сдвиговый ретистр, на вход которого поступают данные из пятого канала. К выходам триггеров (не показаны) декодера 15 подсоединены дешифраторы комбинаций фазирования (не показаны) блока 19 фазирования.

Так как приемная сторона устансРв- 5 лена в режим фазирования, то блоки данных, поступающие с передающей стороны, не принимаются, в результате чего по обратному каналу непрерывно передается сигнал Запрос. При этом осуществляется, непрерывное повторение данных с циклом повторения два блока из блока 3 памяти и производится подсчет запросов, при- ни аемых с обратного канала.

Сосчитав девять запросов., передающая сторона переходит в режим промежуточного фазирования и передает в канал сигнал синхронизации поочередно с первым блоком данных до тех пор, пока по обратному каналу с приемной стороны не поступит сигнал Подтверждение.

На приемной стороне при появлении сигнала на каком-либо одном из двух дешифраторов фазирования (не показаны) блока 19 фазирования формирователь 20 тактовых импульсов устанавливается в исходное состояние, в результате чего приемная сторона настраивается на pa6oiy с кодом, длина которого определяется сигналом на выходе сработавшего дешифратора фазирования (йе показан) блока 19 фазирования. По обратному каналу подается сигнал Подтверждение (состояние О), в результате чего приемная сторона переходит в режим при, ема данных, но цикл работы остается

равным длительности двадцати символов. Приняв с приемной стороны по обратному каналу сигнал Подтверждение, передающая сторона переходит в режим передачи данных.

После того, как принят служебный признак блока А, слодунлдий за правильно принятой комбинацией синхронизации, приемная cTopo}ia переключается на цикл работы, равный ;1лительности блока, содержащего 60 (132) символов. Если признак блока Л не будет принят в течение восьми циклов то приемная сторона возвращается в режим фазирования.

Режим передачи (приема) данных.

Блоки данных передаются непрерывно. Каждому блоку присваивается служебный признак. Первому передаваемому после выхода из начального фазирования блока присваивается признак блока А, всем последующим - признаки блоков В, С, А, В, С, А... соответственно. Такая последовательность признаков исключает потерю или двукратный прием блоков приемной стороной при возг-гущениях в канале связи во всех режимах работы системы.

При вводе данные записываются во входной регистр (не показаны) блока 1 управления вводом данных по сигналу Данные установлены от ООД. Сигнал Синхронизация ввода (длительность 830 мкс), означает, что знак данных принят передатчиком и ООД может устанавливать на выходных шинах следующий знак.

Данные из модема (не показан) поступают в декодер 15 и одновременно во входной регистр 12. В декодере 15 проверяется правильность принятого блока данных. Для этого полином данных делится на полином F(x) х +

+ х + х + 1. Если остаток от деления равен нулю, то предполагается, что данные приняты правильно, и по обратному каналу передае.тся сигнал Подтверждение (состояние О). В противном случае декодер 15 формирует сигнал Ошибка и по обратному каналу передается сигнал Запрос (состояние 1). Сигнал Ощибка запрещает вывод данных в ООД.

Режим повторения блока данных. Все данные (включая сл жебный признак блока), передаваемые в модем (не показан) записываются в блок 3 памяти и хранятся до получения сигнала Подтверждение по обратному каналу.

В случае непоступления сигнала Подтверждение на переданный блок прекращается формирование циклических признаков датчика 4 номера блока данных, в результате чего инвертируется шесть последних символов остатка блока, следующего за блоком, на которьй не поступил сигнап Под

0

5

0

5

0

5

0

5

тверждение , и блок не принимается приемной стороной, а в модем (не показан) передаются два блока данных из блока 3 памяти.

Принятый сигнал Подтверждение восстанавливает ввод данных от ООД. Датчиком 4 номера блока данных во входной регистр (не показан) управления вводом данных записывается очередной циклический признак блока.

Режим промежуточного фазирования.

Если на девять подряд переданных блоков получен сигнап Запрос, то передающая сторона переходит в режим промежуточного фазирования. Этот режим отличается от режима начального фазирования следующим. Блок данных, следующий за сигналом синхронизации, считывается из блока 3 памяти вместе с прежним циклическим признаком. Сигнал синхронизации V блок данных повторяются передающее стороной до получения сигнала Подтверждение. По сигналу Подтверждение передающая сторона возвращается в режим передачи данных, а из блока 3 памяти считывается второй блок данных.

Режим фазирования на приемной стороне устанавливается в процессе работы, если в восьми блоках подряд обнаружена ощибка или четыре раза подряд производится повторение блока данных (происходит чередование блока с ощибкой и блока без в течение восьми циклов).

Распределитель 35 перестраивается на цикл работы, равный длине блока, содержащего данные (260 или 132 символа), после того, как за правильно принятой комбинацией синхронизации принят какой-либо служебный признак блока. Если служебный признак не принят в течение восьми циклов, то приемная сторона возвращается в режим фазирования.

Режим Конец передачи.

В режим Конец передачи передающая сторона переходит при снятии сигнала Запрос передачи от ООД. При этом ввод данных прекращается. Передав последний блок данных, пос- тупивщих на ООД до снятия сигнала Запрос передачи, передающая сторона начинает формировать блоки слу- . жебных признаков Конец передачи, заполненные комбинацией синхронизации. После поступления сигнала Подтверждение на такой блок формирова- тё ль 10 сигналов обмена снимает сигнал Запрос передачи в сторону модема (не показан).

Блок 11 выбора длины кода работает следукишм образом, ,

При передаче поступившего на вход системы очередного сообщения на вход суммируклцего счетчика 23 через открытый «элемент И 21 поступают импульсы, соответствующие очередному постудившему в систему знаку. В счетчике 23 подсчитывается число поступив-- ших в систему информационных бит. На вход суммирующего счетчика 24 через открытый элемент И 22 поступают импульсы, каждый из которых соответствует очередному переданному в прямой канал биту. Счетчик 24 накапливает суммарное количество всех бит, передающихся в канал связи. При образовании в системе сигнала КП, сигнализирующего о том, что источник сообщения закончил передачу, .триггер 33 устанавливается в нулевое состояние и запускается на один цикл распределитель 35, На первые входы элементов И 21 и 22 поступает нулевой сигнал, что обуславливает окончание процесса подсчета числа бит в счетчиках 23 и 24, Сигналом на четвертом выходе распределителя 35 запускается узел 25 деления. На его выходе появляется значение относительной скорости за текущий сеанс связи. Сигнал с третьего выхода распределителя 35 поступает на первый (информационный) вход коммутатора 28, откуда (в зави- , симости от сигнала на инверсном.выходе триггера 32) поступает на второй (управляющий) вход регистров 26 ипи 27, По этому сигналу в один из регистров 26 или 27 (в зависимости от использованной длины кода) записывается значение текущей относительной скорости передачи. По сигналу на втором выходе распределителя 35 генератор 30 случайных импульсов вырабатывает на основном выходе импульс с заранее заданной вероятностью р, а узел 29 сравнения производит сравнении чисел, поступающих с выходов регистров 26 и 27. Единичный сигнал на единичном выходе узла 29 сравнения означает, что число в регистре 26 больше или равно числу в peniCTpe 27, По сигналу на первом « выходе распределителя 35 триггер 32

0

5

о

0

5

0

5

0

5

устанавливается в положение, соответствующее выбранной длине (единичное состояние - выбранная длина кода равна 132 бит, нулевое - 260 бит). По сигналу на пятом вых оде распределителя 35 сбрасывается триггер 33, в результате чего счетчики 23 и 24 устанавливаются в исходное состояние.

Формула изобретения

.первый выход которого соединен с первым входом блока памяти второй вход которого подключен к первому выходу датчика номера блока данных и к пер- вому выходу блока управления памятью, второй выход которого соединен с третьим входом блока памяти, с первым входом блока фазирования, с выходом формирователя тактовых импульсов, с первым входом кодера, с вторым входом блока управления вводом данных и с входом датчика номера блока данных, второй выход которого подключен к третьему входу блока управления вводом данных, четвертый вход которого подключен к первому выходу формирователя сигналов обмена

. и к первому входу анализатора сигналов обратного канала, выход которого соединен с вторым входом блока фазирования и с вторым„входом кодера, третий вход которого подключен к второму выходу блока упрадления вводом данных, пятый вход которого подключен к входу блока управления памятью и к первому вьйсоду блока фазирования, второй выход которого соединен с первым входом формирователя тактовых импульсов и с первым входом формирователя сигналов обмена, второй выход которого соединен с первым входом пульта управления и сигнализации, второй вход котооого подключен к третьему выходу блока управления вводом данных, при этом первый выход пульта управления и сигнализации соединен с вторым входом формирователя сигналов обмена, третий вход у. третий выход которого являются соответственно первым управляющим входом и первым управляющим выходом передающей стороны, тактовым входом которой является

второй вход формирователя тактовых импульсов, второй вход анализатора сигналов обратного канала является вторым управляющим входом передающей стороны, сигнальными входами которой являются шестой и седьмой входы блока управления вводом данных, четвертый выход которого является первым сигнальным выходом передающей стороны, вторым сигнальным выходом которой является выход кодера, второй выход пульта управления и сигнализа- является вторым управляющим выходом передающей стороны, третьим управляющим входом которой является третий вход пульта управления и сигнализации, а на приемной стороне - входной регистр, первый выход которого соединен с первым входом блока памяти, второй вход которого подключен к первому выходу формирователя тактовых импульсов, второй выход которого соединен с первым входом входного регистра, второй выход которого через дешифратор служебных признаков подключен к первому входу формирователя сигналов обмена, второй вход которого подключен к первому выходу декодера, второй выход которого соединен с входом блока фазирования, первый выход которого соединен с первым входом формирователя тактовых импульсов, третий выход которого соединен с первым входом формирователя сигналов канала, второй вход которого подключен к второму выходу блока фазирования, выходной регистр, вход которого подключен к выходу блока памяти, четвертый выход формирователя тактовых импульсов соединен с третьим входом формирователя сигналов обмена, третий вход формирователя сигналов обратного канала соединен с третьим выходом декодера, вход которого подключен к второму входу входного регистра и является сигнальным входом приемной стороны, сигнальным выходом которой является выход выходного регистра, второй вход формирователя тактовых импульсов является тактовым входом приемной стороны, управляющим входом которой является четвертый вход формирователя сигналов обмена, выход которого является первым управляющим выходом приемной стороны, вторым управляющим выходом которой является выход формирователя сигналов обратного канала, о т л и 0

5

0

5

0

5

0

5

0

5

чающаяся тем, что, с целью увеличения пропускной способности, на передающей стороне введен блок выбора длины кода, первый вход которого соединен с восьмым входом блока управления вводом данных, четвертый, пятый и шестой выходы которюго соединены соответственно с первым, вторым и третьим входами блока выборки длины кода, второй выход которого подключен к третьему входу формирователя тактовых импульсов, а на приемной стороне четвертый выход декодера соединен с третьим входом формирователя тактовых импульсов.

узла сравнения, единичный и инверсный выходы которого соединены соответственно с первым и вторым входами логического узла, первый и второй, выходы которого подключены соответственно к S-входу и R-входу первого триггера, С-вход которого соединен с первым выходом распределителя, второй выход которого соедине н с третьим входом узла сравнения и с входом генератора случайных импульсов, единичный и инверсный выходы которого соединены соответственно с третьим и четвертым входами логического узла, первые входы первого и второго элементов И подключены к выходу второго триггера, R-вход которого соединен с входом распределителя, третий выход которого подключен к первому входу коммутатора, первый и второй выходы которого соединены с вторыми входами соответственно первого и второго регистров, вторые входы пер-; вого и второго суммирующих счетчиков подключены к S-входу второго триггера и к пятому выходу распределителя,

четвертый выход которого соединен с третьим входом узла деления, второй вход коммутаторй соединен с инверсным выходом первого триггера и с входом усилителя мощности, выход которого является вторым выходом блока выбора длины кода, первым выходом

Фиг. 2

которого является единичный выход первого триггера, первым, вторым и третьим входами блока выбора длины кода являются соответственно второй вход первого элемента И, второй вход второго элемента И и R-вход второго триггера.

Фиг. f

го

(О

S

Авторы

Даты

1989-07-30—Публикация

1986-12-15—Подача