Изобретение относится к вычислительной технике и может найти применение при построении интегральных схем.

Известны логические элементы на полевом транзисторе с затвором Шотки (ПТШ) ИСПЛ-типа, истоковые повторители которых имеют нагрузку в виде резистора или ПТШ. Эти логические элементы имеют активную часть на транзисторах ПТШ и выходные усилители тока.

Логический элемент ПТШ ИСПЛ-типа представляет собой двухкаскадный усилитель. Первый каскад выполнен по схеме токового ключа. Каждое его плечо снабжено истоковым повторителем для согласования логических элементов по уровням напряжения сигнала и его мощности.

Для получения необходимого размаха напряжения на выходе логического элемента необходимо получить большую разность напряжений в схеме токового ключа. Необходимость запаса разности напряжений обусловлена потерями сигнала в истоковых повторителях. Необходимость увеличения размаха напряжений в токоповторителях снижает быстродействие логического элемента.

Целью изобретения является повышение быстродействия логического элемента на полевых транзисторах с затвором Шотки ИСПЛ-типа.

Поставленная цель достигается тем, что в логический элемент, содержащий семь транзисторов, шесть диодов, два резистора нагрузки токового ключа, входную шину, шину подачи опорного напряжения, выходные шины и отрицательную шину источника питания, причем истоки первого и второго

VI 4 N) О Ч)

со

транзисторов соединены со стоком третьего транзистора, исток и затвор которого подключены к отрицательной шине источника питания, к которой подсоединены и истоки шестого и седьмого транзисторов, стоки первого и второго транзисторов подключены к затворам четвертого, и пятого транзисторов соответственно, а через резисторы нагрузки токового ключа соответственно соединены с общей шиной, к которой подкл ючен ы стоки четвертого и пятого тран- зисторов, истоки четвертого и пятого транзисторов через первый и четвертый диоды сдвига уровня соединены с выходными шинами логического элемента и вторым и пятым диодами сдвига уровня, которые через третий и шестой диоды сдвига уровня соединены со стоками шестого и седьмого транзисторов соответственно, в логический элемент введены два резистора, причем затворы шестого и седьмого транзисторов соединены со стоками седьмого и шестого транзисторов через первый и второй резисторы соответственно.

Решения со сходной совокупностью существенных признаков не известны, значит решение обладает существенными отличиями.

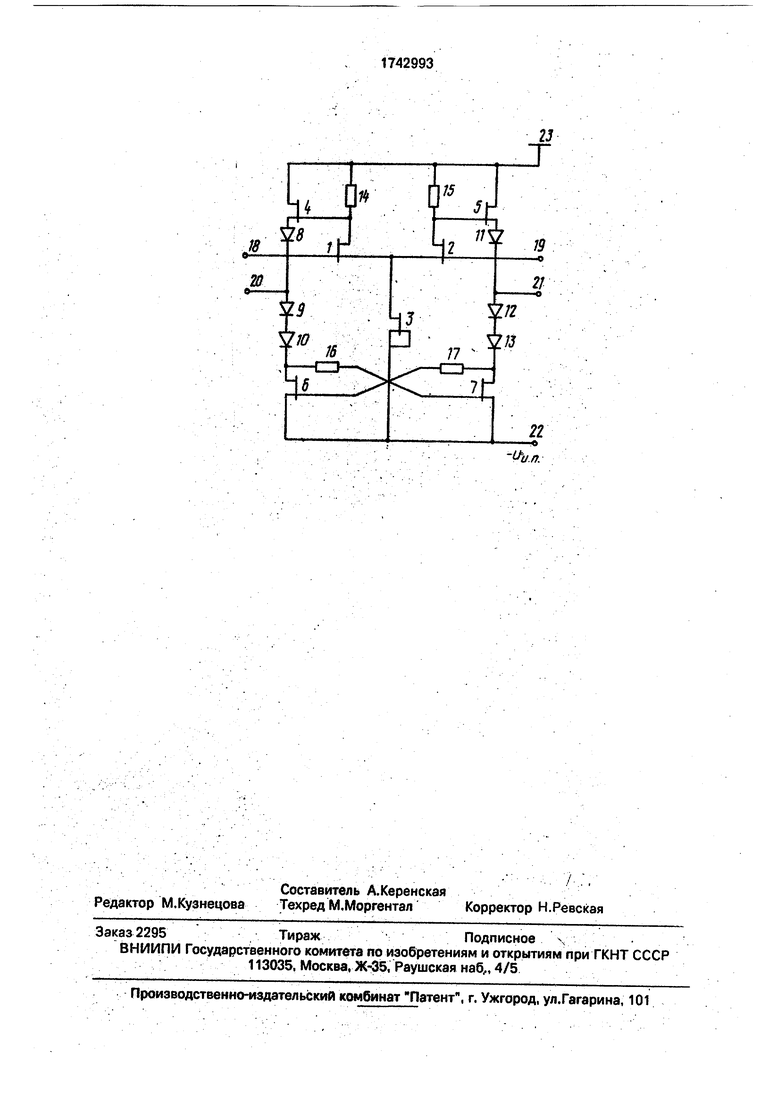

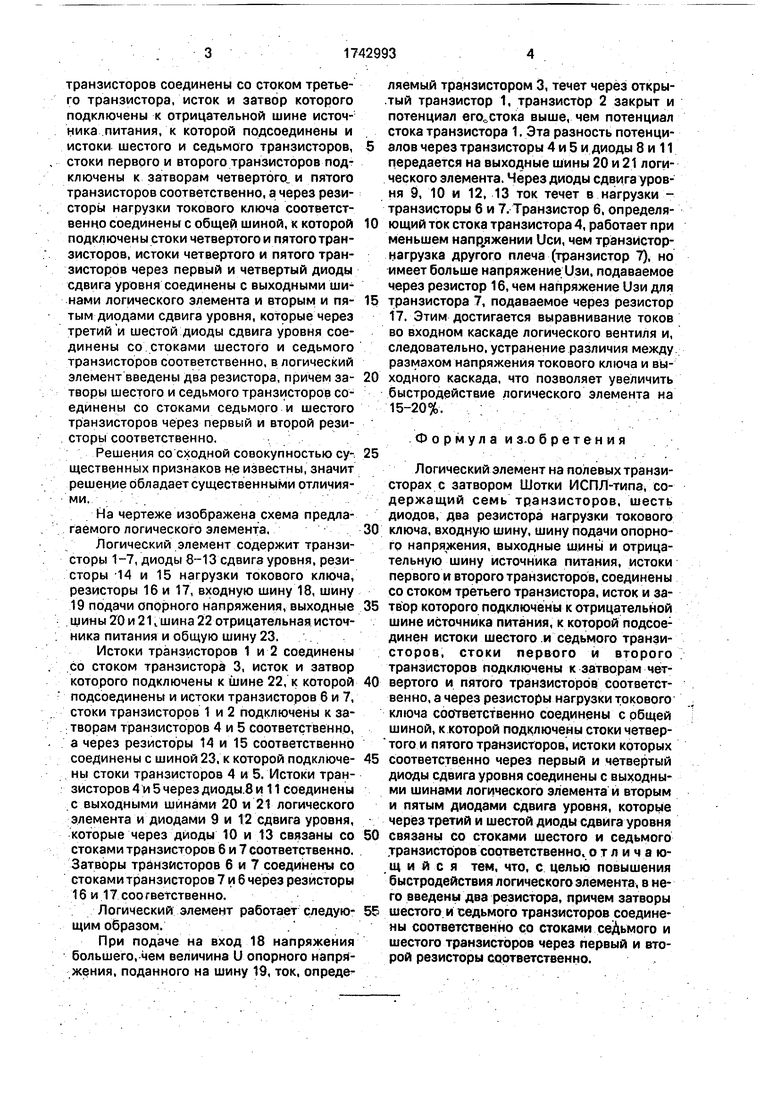

На чертеже изображена схема предлагаемого логического элемента.

Логический элемент содержит транзисторы 1-7, диоды 8-13 сдвига уровня, резисторы 14 и 15 нагрузки токового ключа, резисторы 16 и 17, входную шину 18, шину 19 подачи опорного напряжения, выходные шины 20 и 211 шина 22 отрицательная источника питания и общую шину 23.

Истоки транзисторов 1 и 2 соединены со стоком транзистора 3, исток и затвор которого подключены к шине 22, к которой подсоединены и истоки транзисторов 6 и 7, стоки транзисторов 1 и 2 подключены к затворам транзисторов 4 и 5 соответственно, а через резисторы 14 и 15 соответственно соединены с шиной 23, к которой подключены стоки транзисторов 4 и 5. Истоки транзисторов 4 и 5 через диоды.8 и 11 соединены с выходными шинами 20 и 21 логического элемента и диодами 9 и 12 сдвига уровня, которые через диоды 10 и 13 связаны со стоками транзисторов 6 и 7 соответственно. Затворы транзисторов 6 и 7 соединены со стоками транзисторов 7 и б через резисторы 16 и 17 соответственно.

Логический элемент работает следующим образом.

При подаче на вход 18 напряжения большего, чем величина U опорного напряжения, поданного на шину 19, ток, определяемый транзистором 3, течет через открытый транзистор 1, транзистор 2 закрыт и потенциал его0стока выше, чем потенциал стока транзистора 1. Эта разность потенциалов через транзисторы 4 и 5 и диоды 8 и 11 передается на выходные шины 20 и 21 логического элемента. Через диоды сдвига уровня 9, 10 и 12, 13 ток течет в нагрузки - транзисторы 6 и 7. Транзистор 6, определяющий ток стока транзистора 4, работает при меньшем напряжении 11си, чем транзистор- нагрузка другого плеча (транзистор 7), но имеет больше напряжение 1)зи, подаваемое через резистор 16, чем напряжение 1)зи для

транзистора 7, подаваемое через резистор 17. Этим достигается выравнивание токов во входном каскаде логического вентиля и, следовательно, устранение различия между размахом напряжения токового ключа и выходного каскада, что позволяет увеличить быстродействие логического элемента на 15-20%.

25

Формула изобретения

Логический элемент на полевых транзисторах с затвором Шотки ИСПЛ-типа, содержащий семь транзисторов, шесть диодов, два резистора нагрузки токового

ключа, входную шину, шину подачи опорного напряжения, выходные шины и отрицательную шину источника питания, истоки первого и второго транзисторов, соединены со стоком третьего транзистора, исток и затвор которого подключены к отрицательной шине источника питания, к которой подсоединен истоки шестого и седьмого транзисторов, стоки первого и второго транзисторов подключены к затворам четвертого и пятого транзисторов соответственно, а через резисторы нагрузки токового ключа соответственно соединены с общей шиной, к которой подключены стоки четвер- того и пятого транзисторов, истоки которых

соответственно через первый и четвертый диоды сдвига уровня соединены с выходными шинами логического элемента и вторым и пятым диодами сдвига уровня, которые через третий и шестой диоды сдвига уровня

связаны со стоками шестого и седьмого транзисторов соответственно, о т л и ч а ю- щ и и с я тем, что, с целью повышения быстродействия логического элемента, в него введены два резистора, причем затворы

шестого и седьмого транзисторов соединены соответственно со стоками седьмого и шестого транзисторов через первый и второй резисторы соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ЛОГИЧЕСКИХ УРОВНЕЙ | 1988 |

|

SU1593538A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА НОРМАЛЬНО ОТКРЫТЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 1987 |

|

SU1530059A1 |

| Операционный усилитель | 1990 |

|

SU1732427A1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2766864C1 |

| ИСТОЧНИК ПИТАНИЯ НЕЛИНЕЙНОЙ ИЛИ ЛИНЕЙНОЙ НАГРУЗКИ | 2021 |

|

RU2768272C1 |

| Устройство выборки и хранения | 1979 |

|

SU826564A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU868840A1 |

| Операционный усилитель | 1990 |

|

SU1753583A1 |

| Пьезополупроводниковый стабилизатор постоянного напряжения | 1980 |

|

SU926636A1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ «ПЕРЕГНУТОГО» КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ | 2022 |

|

RU2773907C1 |

Изобретение относится к вычислительной технике и может найти применение яри построении интегральных схем. Целью изобретения является повышение быстродействия логического элемента на полевых транзисторах с затвором Шотки ИСПЛ-типа. Логический элемент содержит входной каскад, образованный транзисторами 1-3, истоковые повторители на транзисторах 4 и 5, транзисторы 6 и 7, являющиеся генераторами тока, и диоды сдвига уровня 8-13. Введение обратных связей с- помощью резисторов 16 и 17 превращает динамическую нагрузку истоковых повторителей (транзисторы 6 и 7) в активную, сопротивление которой зависит от режима работы. Этим достигается выравнивание токов во входном каскаде логического вентиля и, сле- довательно, устранение различия между размахом напряжений токового ключа и выходного каскада, что позволяет увеличить быстродействие логического элемента. 1 ил. V w ё

| IEEE Transactions on microwave theory and techniques, Vol 14ТГ-32, 1984, № 1, p.p | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1992-06-23—Публикация

1989-11-09—Подача