Изобретение относится к радиотах- Шке и измерительной техни ке и молсет быть использовэ:но даш изг.аерения анп- литуды и фазы сигяалоЕ

Цель у;зобретенйя - повыиение точности изкаракия амплитуды сигналов, Су7дкость И5;обретекк :я :за1шючается в том, что 3 данном устройстве используется метод параллагЕьного усред HieHHHj который позволяет с),/щественно повысить точность и помекоустойчи- BJocTb измерения за счет измере- на каждом пе-оиоде входного сиг- фазового сдвига на п-м фиксиро- Б нньпг уровняк ; т,е, измерение фазово гЬ сдвига ocyHTecTBnsieTCH п раз за период. Кроме тогод па-раллельно- гЬ усреднения используется и для yiBe- лрчения точности из epeния амплитуды вводного сигнала. При этом полезную фформац гго об амплитуде и фазе на к)аждом периоде входного сигияла несу :фтерваль ; времени между моментом пе- р|есечения нарастшощим опорный сигна- лрм нулевого уровня и моментами пе р сеченип нормализованный входньм с игналом фиксированньк уровней;

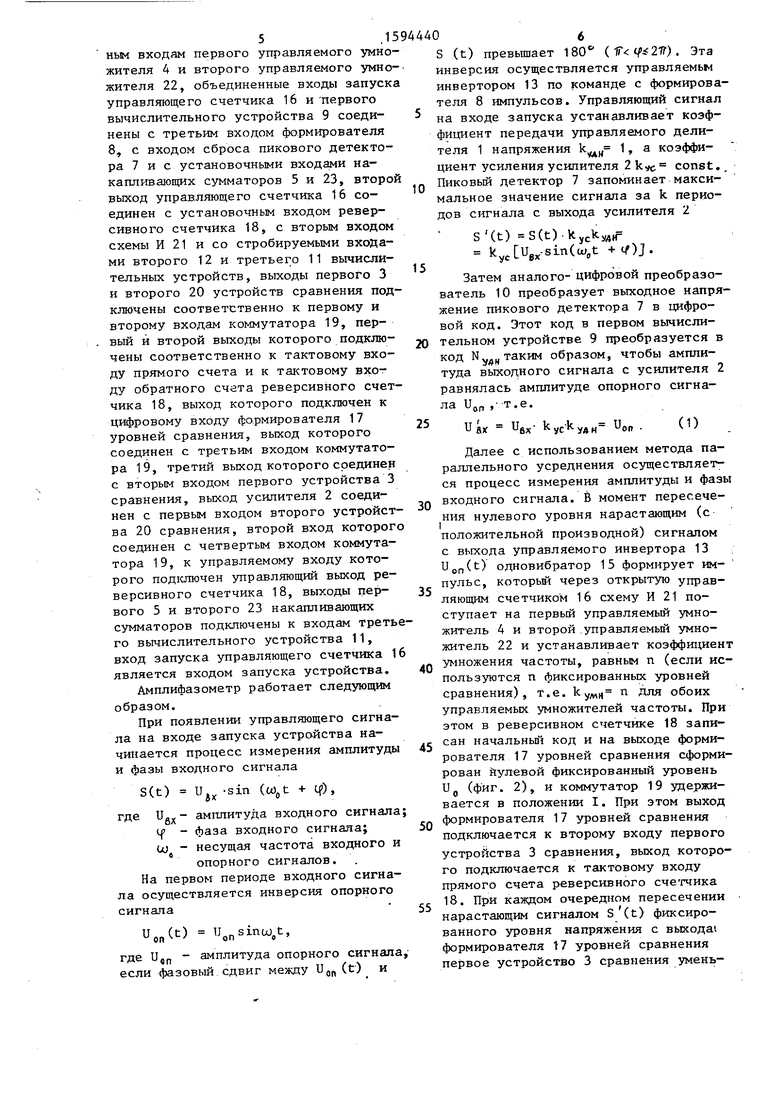

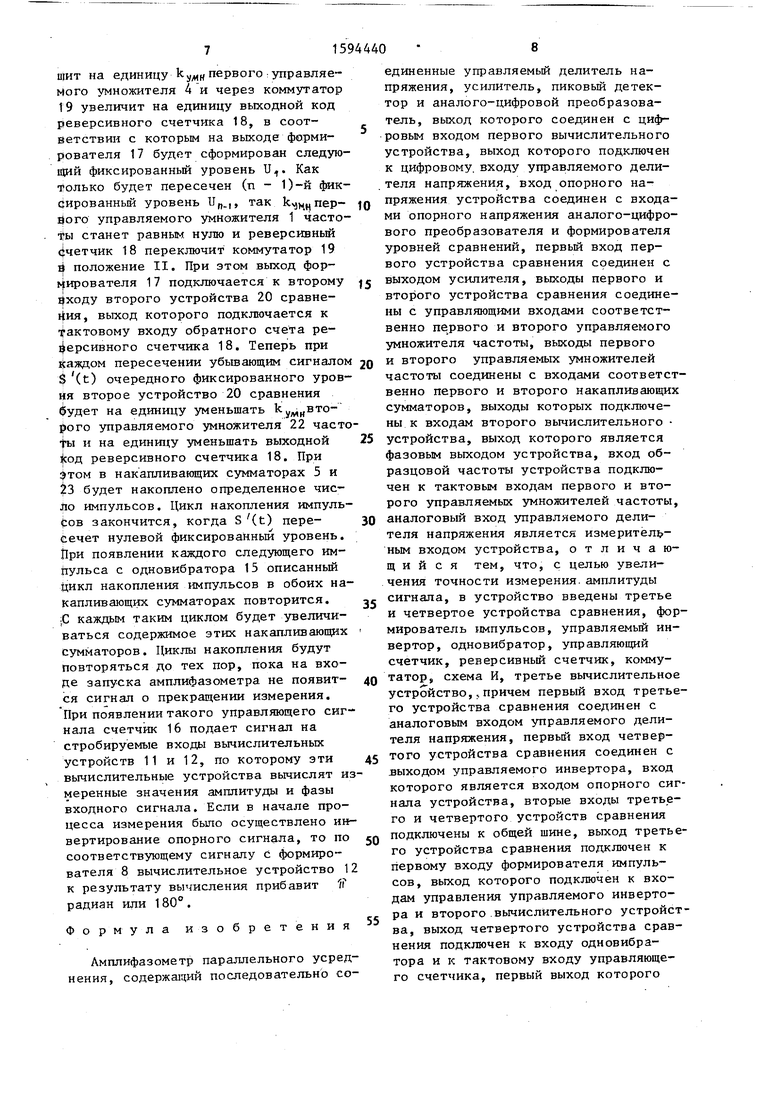

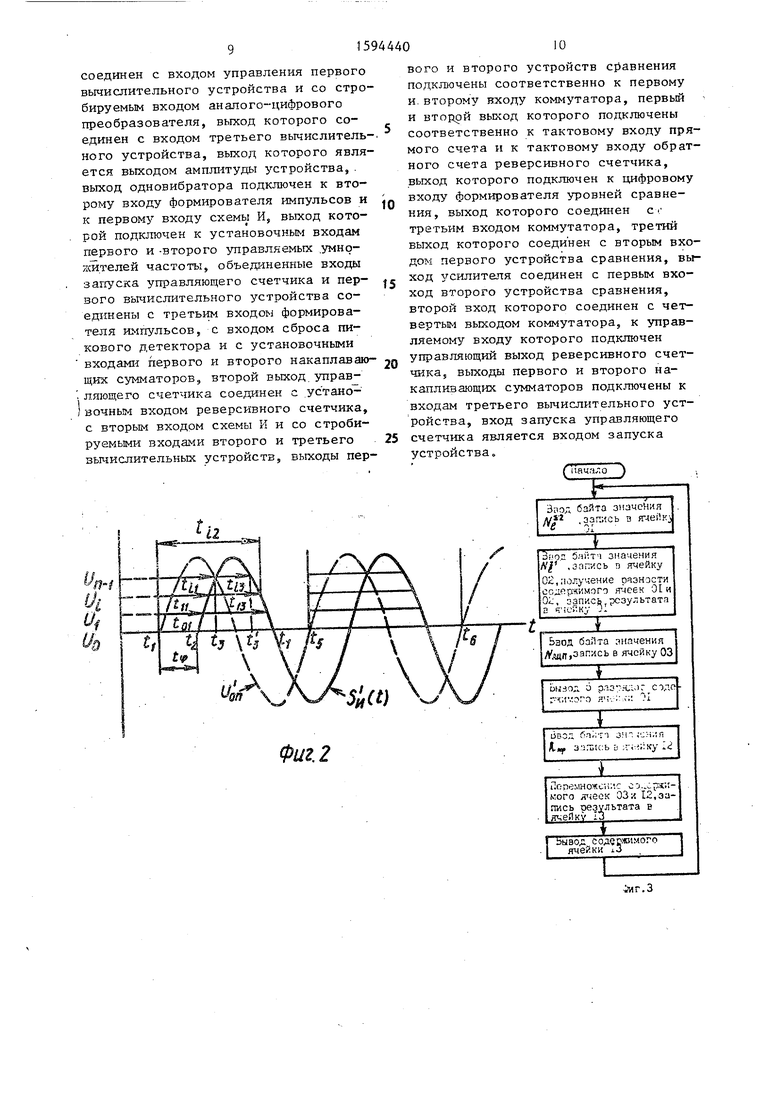

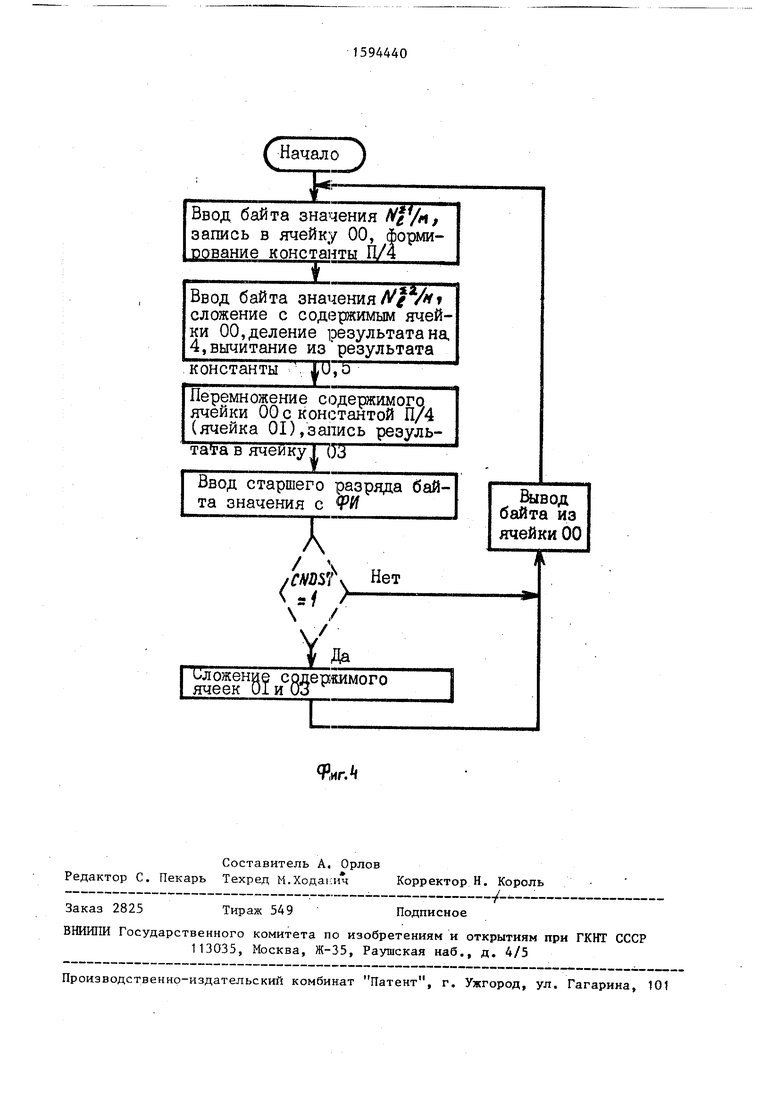

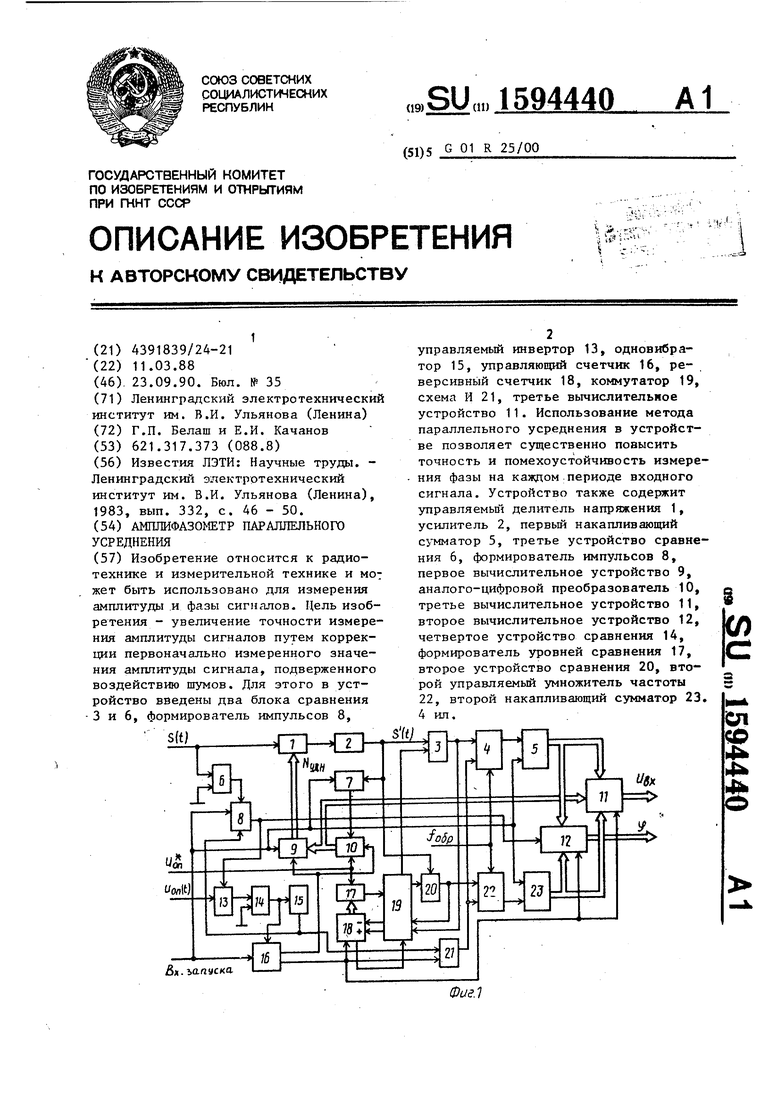

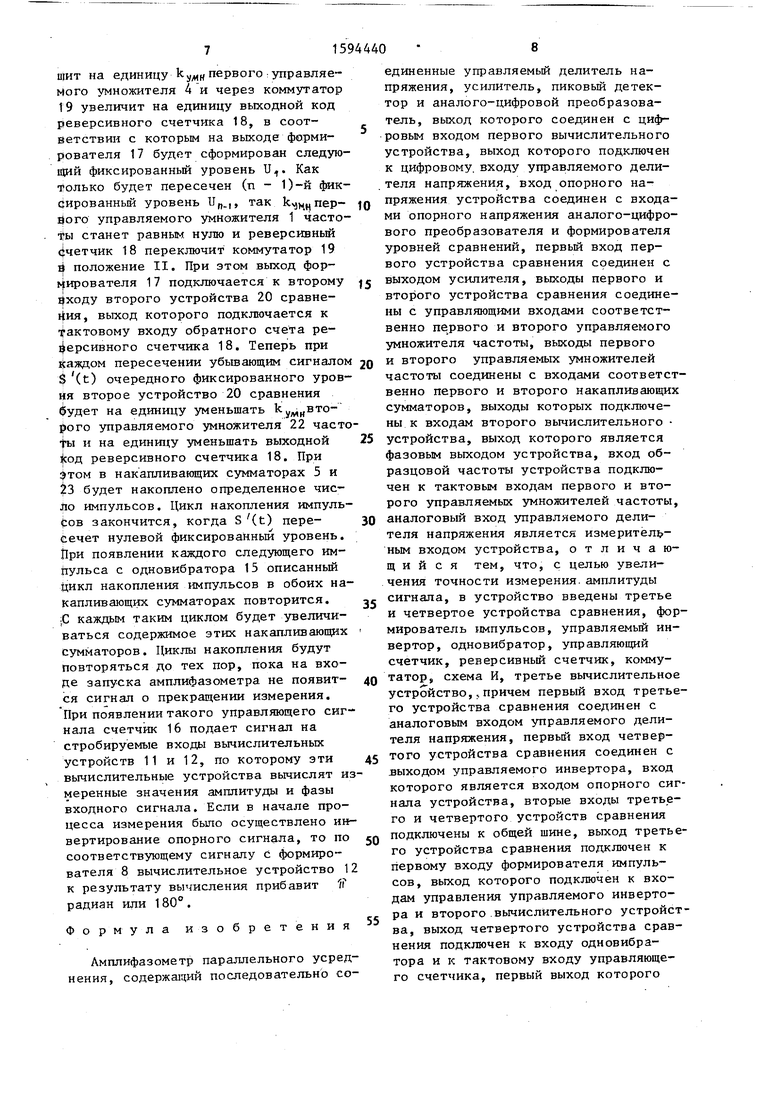

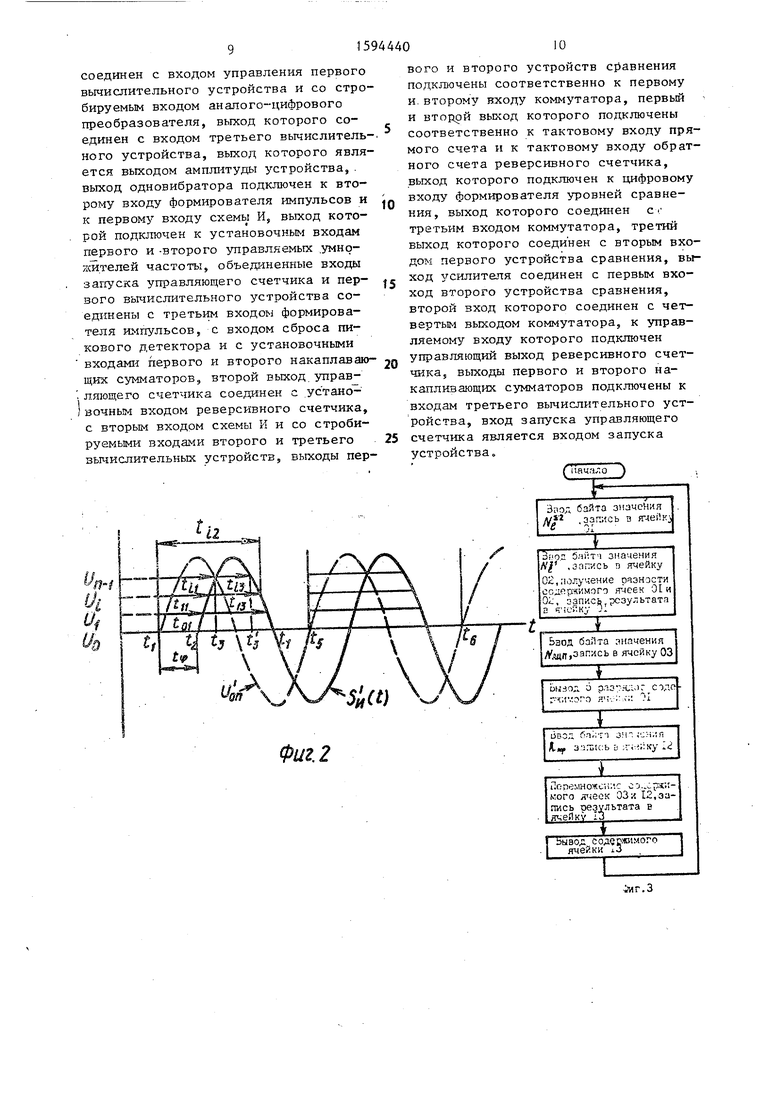

: На сриг „ 1 приведена схема аыпли- Фазометра; на фиг, 2 - временные диа daMMbig покснгаогдие его работу; на фиг. 3 - блок-схема алгоритма вьиис- jieHHH амилитул,Ыг ка фиг, 4 - блок™ ахема алгоритма вычмсленкя фазьь

: /шгшисЬазометр о параллельно го усред- Ие.ния (ёкг« 1) содержит управляемьй

1

з,пряжен:1-Ш5 усилитель /,

первое устроис.тво

сравнения;

зык управляемьй умножитель 4 частоты , первьй накапливающий сутхпматор 5, ifpeTbe устройство 6 сравнения, пиковый детектор 7, формирователь 8 т--;- пульсов, первое вычислительное уст- 1 ойство 95 аналого-цифровой преобразователь 10,, третье вычислительное устройство 11э второе вычислительное устройство 12, угфавляемый инвертор 13, четвертое устройство 14 сравнения одновибратор 15, управляющий счетчик 16,.. формирователь 17 уровне й сравнения3 реверсивный счетчик 18, коммутатор 195 второе уст-ройство 20 сравнения, скему И 21;. второй управляемьй умножитель 22 частоты второй накапливажций сумматор 23 при этом последовательно соединены управляемы делитель 1 напрякенш-з,, усилитель 2, пиковый детектор 7 и аналого-цифровой щчеобр.азователь 10., выход которо0

0

го соединен с.цифровым входом первого вычислительного устройства 9, выход нотс;рого подключен к цифрово- мз входу управляемого делителя 1 на прялсенил.;, вход опорного йапряження устройств;;; соединен с входами опорного напря жения анапого-цифрового преобразователя 10 и формирователя 17 уровней сравнения, первый вход первого з стройс -гЕаЗ сравнения соединен свы- кодом усилителя 2, вьЕсода первого Зи второго 20 устройства сравкен гя соединены с управляющи.и входами соот- ветственнс п.ер:/:эго 4 PI второго /2 управляемь; я мнолитзлей частоты, вы- ходь5 пзрЕОго 4 и второго 22 управляемых ум:но :а1телек частоты соединены с входами с(5стветствен ю первого 5 и второго нака.Шдизающих сумматоров выходр которых, подключены к входа. второго лчичислит&льпого устройства 12д ВЬЕ;ОД ;лоторрго является фазовьп - выходок ус гройстьаэ вход образцовой, частота) у::;тройс.1 Еа подклзоче -; к тактовым входам первого 4 и второго 22 управляемьж умножителей,, анапоговый вход у;-1т аЕляьмого делителя i является измеркте.пьным входом устройства5 первьп : вхо.ц } ре.тьего- устройства б сравнения соед::1нен с аналоговым входом уиравллемог О делителя 1,. первый вход чатЕс-ртого устройства (4 сравнения соединен с выходом з правляемо-- го инвертора 13, -вход которого яв- ляется входом О норного сигнала устройства., вторые входы третьего 6 и четвертог о 14 устройств сравнения подключены к сбцей п№.не, выход третье-го устройства 6 сравнения подключен к первому входу формирователя 8, выход KOTopci c подключен к вилдам управления управляемого инвертора 13 и второго Бычислительного устройства 12 э выход четвер1 ого устройст.йа 14 сравне.н;1я: псдкхзочен к входу одновибратора

1 г

тактовому входу управ0

ляющего счетчика 16,- первый выход, к,о- торого соедннен с входом управления первого вычиспительнсго устройства 9 и со стробкруемьк .п;ом аналого- цифрового преобразователя lOj вьскод которого соединен с входом третьего вычислительного устройства 1 i ., выход которого является выходом амплитудь устройства,, одновибратора 15 подключен ;s второму В ходу формирователя 8 и к первому входу схемы И 21,, выход которой подключен к устаггоаочным входям первого управляемого умножителя 4 и второго управляемого умножителя 22, объединенные входы запуска управляющего счетчика 16 и первого вычислительного устройства 9 соединены с третьим входом формирователя 8, с входом сброса пикового детектора 7 и с установочными входами на- капливаюпщх сумматоров 5 и 23, второй выход управляющего счетчика 16 соединен с установочным входом реверсивного счетчика 18, с вторым входом схемы И 21 и со стробируемыми входами второго 12 и третьего 11 вычислительных устройств, выходы первого 3 и второго 20 устройств сравнения подключены соответственно к первому и второму входам коммутатора 19, первый и второй выходы которого подключены соответственно к тактовому входу прямого счета и к тактовому вхог- ду обратного счета реверсивного счетчика 18, выход которого подключен к цифровому входу формирователя 17 уровней сравнения, выход которого соединен с третьим входом коммутатора 19, третий выход которого соединен с вторьм входом первого устройства 3 сравнения, выход усилителя 2 соединен с первым входом второго устройства 20 сравнения, второй вход которог соединен с четвертым входом коммутатора 19, к управляемому входу которого подюпочен управляющий выход реверсивного счетчика 18, выходы первого 5 и второго 23 накапливающих сумматоров подключены к входам третьго вьмислительного устройства 11, вход запуска управляющего счетчика 1 является входом запуска устройства. Амплифазометр работает следующим

образом.

При появлении управляющего сигнала на входе запуска устрайства начинается процесс измерения амплитуды и фазы входного сигнала

S(t)

и

sin (to.t + tf).

4х 0

где амплитуда входного сигнала фаза входного сигнала; несущая частота входного и опорного сигналов. На первом периоде входного сигнала осуществляется инверсия опорного сигнала

йх- Ч - . )

где и. - амплитуда опорного сигнала,- если фазовый сдвиг между и(t) и

5

0

S (t) превьппает 180 ( 1Г ) . Эта инверсия осуществляется управляемьи инвертором 13 по команде с формирователя 8 импульсов. Управляющий сигнал на входе запуска устанавливает коэффициент передачи управляемого делителя 1 напряжения , 1, а коэффициент усиления усилителя 2 kvc const., Пиковьш детектор 7 запоминает максимальное значение сигнала за k периодов сигнала с выхода усилителя 2

S (t) S(t)

kyJUg -sinCw.t +c/)J.

Затем аналого-цифровой преобразователь 10 преобразует выходное напряжение пикового детектора 7 в цифровой код. Этот код в первом вычислительном устройстве 9 преобразуется в код N,,, таким образом, чтобы амплитуда выходного сигнала с усилителя 2 равнялась амплитуде опорного сигна- т.е.

5

ла и

и

оп f ft)f

и

ex

01

(1)

0

5

0

5

5

Далее с использованием метода параллельного усреднения осуществляется процесс измерения амплитуды и фазы входного сигнала. И момент пересечения нулевого уровня нарастающим (с положительной производной) сигналом с выхода управляемого инвертора 13 ; Upn(t) одновибратор 15 формирует импульс, которьй через открытую управляющим счетчиком 16 схему И 21 поступает на первый управляемый умно- жит ель 4 и второй .управляемьй умножитель 22 и устанавливает коэффициент умножения частоты, равным п (если используются п фиксированных уровней сравнения), т.е. ,,, п для обоих управляемых умножителей частоты. При этом в реверсивном счетчике 18 записан начальньп код и на выходе формирователя 17 уровней сравнения сформирован йулевой фиксированный уровень Ug (фиг. 2), и коммутатор 19 удерживается в положении I. При этом выход формирователя 17 уровней сравнения подключается к второму входу первого устройства 3 сравнения, выход которого подключается к тактовому входу прямого счета реверсивного счетчика 18. При каждом очередном пересечении нарастающим сигналом S (t) фиксированного уровня напряжения с выхода1 формирователя 17 уровней сравнения первое устройство 3 сравнения уменьшит на единицу ky, первого :управляе- Ного умножителя 4 и через коммутатор 19 увеличит на единицу выходной код реверсивного счетчика 18, в соот- ветствии с которым на выходе формирователя 17 будет сформирован следующий фиксированньй уровень U,. Как тголько будет пересечен (п - 1)-й фиксированный уровень U(,-i ого управляемого умножителя 1 часто- станет равным нулю и реверсивный с четчик 18 переключит коммутатор 19 $ положение II. При этом выход фор- Цирователя 17 подключается к второму ходу второго устройства 20 сравне- ия, выход которого подключается к актовому входу обратного счета ре- ерсивного счетчика 18. Теперь при каждом пересечении убывающим сигналом $ (t) очередного фиксированного уровня второе устройство 20 сравнения будет на единицу уменьшать ky BTO- рого управляемого умножителя 22 часто ы и на единицу уменьшать выходной сод реверсивного счетчика 18, При $том в накапливающих сумматорах 5 и is будет накоплено определенное число импульсов. Цикл накопления импульсов закончится, когда S (t) пере- сечет нулевой фиксированный уровень, 1ри появлении каждого следующего им- йульса с одновибратора 15 описанный накопления импульсов в обоих накапливающих сумматорах повторится, :С каждым таким циклом будет увеличиваться содержимое этих накапливающих сумматоров. Циклы накопления будут повторяться до тех пор, пока на входе запуска амплифазометра не появит- ся сигнал о прекращении измерения, При появлении такого управляющего сигнала счетчик 16 подает сигнал на стробируемые входы вычислительных устройств 11 и 12, по которому эти вычислительные устройства вычислят имеренные значения амплитуды и фазы входного сигнала. Если в начале процесса измерения было осуществлено инвертирование опорного сигнала, то по соответствующему сигналу с формирователя 8 вычислительное устройство 1 к результату вычисления прибавит fi радиан или 180°,

Формула изобретения

Амплифазометр параллельного усреднения, содержащий последовательно соединенные управляемый делитель напряжения, усилитель, пиковьй детектор и аналого-цифровой преобразователь, выход которого соединен с цифровым входом первого вычислительного устройства, выход которого подключен к цифровому, входу управляемого делителя напряжения, вход опорного напряжения устройства соединен с входами опорного напряжения аналого-цифрового преобразователя и формирователя уровней сравнений, первьй вход первого устройства сравнения соединен с выходом усилителя, выходы первого и второго устройства сравнения соединены с управляющими входами соответственно пе рвого и второго управляемого умножителя частоты, выходы первого и второго управляемых зт ножителей частоты соединены с входами соответственно первого и второго накапливающих сумматоров, выходы которых подключены к входам второго вычислительного устройства, выход которого является фазовым выходом устройства, вход образцовой частоты устройства подключен к тактовым входам первого и второго управляемых умножителей частоты, аналоговый вход управляемого делителя напряжения является измерител.- ным входом устройства, о т л и ч а ю- щ и и с я тем, что, с целью увеличения точности измерения, амплитуды сигнала, в устройство введены третье и четвертое устройства сравнения, формирователь импульсов, управляемьй инвертор, одновибратор, управляющий счетчик, ренерсивньй счетчик, коммутатор, схема И, третье вычислительное устройство,,причем первый вход третьего устройства сравнения соединен с аналоговым входом управляемого делителя напряжения, первьпЧ вход четвертого устройства сравнения соединен с выходом управляемого инвертора, вход которого является входом опорного сигнала устройства, вторые входы третьего и четвертого устройств сравнения подключены к общей шине, выход третьего устройства сравнения подключен к первому входу формирователя импульсов, выход которого подключен к входам управления управляемого инвертора и второго.вычислительного устройства, выход четвертого устройства сравнения подключен к входу одновибратора и к тактовому входу управляющего счетчика, первый выход которого

10

соединен с входом управления первого вычислительного устройства и со стро- бируемым входом аналого-цифрового преобразователя, выход которого соединен с входом третьего вычислительного устройства, выход которого является выходом амплитуды устройства,. выход одновибратора подключен к второму входу формирователя импульсов и к первому входу схемы И, выход которой подключен к установочным входам первого и -второго управляемых .умножителей частоты, объединенные входы заггуска управляющего счетчика и первого вычислительного устройства соединены с третьим входом формирователя импульсов, с входом сброса пикового детектора и с установочными входами первого и

щих сумматоров, второй выход.управу , ляющего счетчика соединен с ус тано- )ночным входом реверсивного счетчика, с вторым входом схемы К и со строби- руемыми входами второго и третьего 25 вычислительных устройств, выходы пер15

вого и второго устройств С1 авнения подключены соответственно к первому и.второму входу коммутатора, первый и второй выход которого подключены соответственно к тактовому входу прямого счета и к тактовому входу обратного счета реверсивного счетчика, выход которого подключен к цифровому входу формирователя уровней сравнения, выход которого соединен с г третьим входом коммутатора, третий выход которого соединен с вторым входом первого устройства сравнения, выход усилителя соединен с первым вхо- ход второго устройства сравнения, второй вход которого соединен с четвертым выходом коммутатора, к управляемому входу которого подключен

L У ISlLJU liA

второго накаплаваю- jn Управляющий выход реверсивного счетчика, выходы первого и второго накапливающих сумматоров подключены к входам третьего вычислительного устройства, вход запуска управляющего счетчика является входом запуска устройства.

( liau. V.o J

5

вого и второго устройств С1 авнения подключены соответственно к первому и.второму входу коммутатора, первый и второй выход которого подключены соответственно к тактовому входу прямого счета и к тактовому входу обратного счета реверсивного счетчика, выход которого подключен к цифровому входу формирователя уровней сравнения, выход которого соединен с г третьим входом коммутатора, третий выход которого соединен с вторым входом первого устройства сравнения, выход усилителя соединен с первым вхо- ход второго устройства сравнения, второй вход которого соединен с четвертым выходом коммутатора, к управляемому входу которого подключен

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения параметров радиоимпульсов | 1980 |

|

SU938206A1 |

| Двухотсчетный преобразователь синусно-косинусно-модулированных сигналов переменного тока в код | 1985 |

|

SU1283969A1 |

| Устройство для считывания графической информации | 1987 |

|

SU1564661A1 |

| Устройство для оценки амплитуды узкополосного случайного процесса | 1987 |

|

SU1499375A1 |

| Цифровой вольтметр | 1985 |

|

SU1337791A1 |

| ЦЕЗИЕВЫЙ СТАНДАРТ ЧАСТОТЫ | 1994 |

|

RU2076411C1 |

| УСТРОЙСТВО КОНТРОЛЯ ЭНЕРГИИ, ПЕРЕДАВАЕМОЙ ПО ВОЛОКОННО-ОПТИЧЕСКИМ ЛИНИЯМ СВЯЗИ (ВАРИАНТЫ) | 1999 |

|

RU2152133C1 |

| Следящий преобразователь угла поворота вала в код | 1983 |

|

SU1116446A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1994 |

|

RU2083995C1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

Изобретение относится к радиотехнике и измерительной технике и может быть использовано для измерения амплитуды и фазы сигналов. Цель изобретения - увеличение точности измерения амплитуды сигналов путем коррекции первоначально измеренного значения амплитуды сигнала, подверженного воздействию шумов. Для этого в устройство введены два блока сравнения 3 и 4, формирователь импульсов 8, управляемый инвертор 13, одновибратор 15, управляющий счетчик 16, реверсивный счетчик 18, коммутатор 19, схема И 21, третье вычислительное устройство 11. Использование метода параллельного усреднения в устройстве позволяет существенно повысить точность и помехоустойчивость измерения фазы на каждом периоде входного сигнала. Устройство также содержит управляемый делитель напряжения 1, усилитель 2, первый накапливающий сумматор 5, третье устройство сравнения 6, формирователь импульсов 8, первое вычислительное устройство 9, аналого-цифровой преобразователь 10, третье вычислительное устройство 11, второе вычислительное устройство 12, четвертое устройство сравнения 14, формирователь уровней сравнения 17, второе устройство сравнения 20, второй управляемый умножитель частоты 22, второй накапливающий сумматор 23. 4 ил.

фц12

Зпод байта значения Л/ запись 3 jT-ieilKj

/Vg ,

I

байт- знаиения Л / .запись в ячейку

02,получение разности сод 1р;«импго ячеек 01 и Oi:, запись,результата S ччсГ;ку 01

Ьзод баПта значения здп,запись в ячейку 03

Z

DiisojX о рлз-:н, r Hvorn ячг;::;;: 01

13вод 3) iOt.ifi Д. 3 in;i(:b ь

По ре ми ож си; . с с D . .с pt;; - кого .ячеек 03 и 12,запись результата в ячейку П

Ьывод сод5С си«о

ячейки i3

j

Г Началс)

Ввод байта значения , запись в ячейку 00, форми- рование константы П/4

т

Ввод байта значения Л / А т сложение с содержимым ячейки 00,деление результата на 4,вычитание из результата

константы

i

U,Q

Перемножение содержимого ячейки 00 с константой П/4 (ячейка 01),запись результа га в ячейку I (JJ

Ввод старшего разряда байта значения с И

Л

::/

/

i Да

Вывод байта из

ячейки 00

| Известия ЛЭТИ: Научные труды | |||

| - Ленинградский электротехнический институт им | |||

| В.И | |||

| Ульянова (Ленина), 1983, вып | |||

| Приспособление, обнаруживающее покушение открыть замок | 1910 |

|

SU332A1 |

| Способ изготовления звездочек для французской бороны-катка | 1922 |

|

SU46A1 |

Авторы

Даты

1990-09-23—Публикация

1988-03-11—Подача