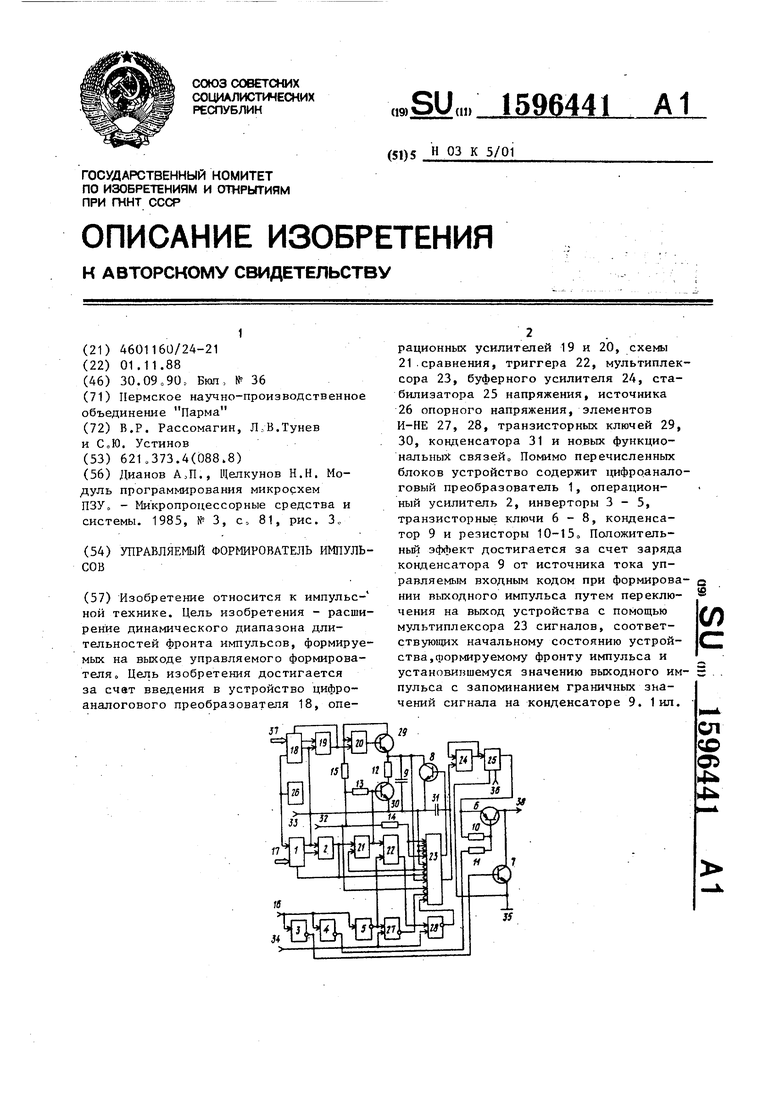

Изобретение относится к импульсной технике и может быть использовано в качестве управляемого формирователя импульсов в устройствах программирования микросхем постоянных запоминающих устройств и программируемых логических матриц. Цель изобретения - расширение динамического диапазона длительностей фронта формируемых управляемым форми рователем импульсов. На чертеже приведена функциональная схема управляемого формирователя импульсов. Управляемый формирователь импульсов содержит первый цифроаналоговый преобразователь 1, первый операционный усилитель 2, первьй 3, второй 4 и третий 5 элементы НЕ, первый 6, второй 7 и третий 8 транзисторные клю чи, первый 1 онденсатор 9, первый 10, второй 11, третий 12, четвертый 13, пятьй 14 и шестой 15 резисторы, вход 16 запуска, первую группу 17 информационных входов, второй .цифроаналоговьш преобразователь 18, второй 19 и третий 20 операционные усилители, схему 21 сравнения, триггер 22, мультиплексор 23, буферньй усилитель 24, стабилизатор 25 напряжения, источник 26 опорного напряжения, первый 27 и второй 28 элементы И-НЕ, четвертьй 29 и пятый 30.транзисторные ключи, второй конденсатор 31, плюсовую шину 32 аналогового питания, шину 33 аналоговой земли, вход 34 разрешения, ши ну 35 цифровой земли, плюсовую шину 36цифрового питания, вторую группу 37информационных входов, выход 38, Вход первого элемента НЕ 3 является входом запуска устройства, первая группа 17 информационных входов.уст-г ройства подключена к группе информационных входов первого цифроаналогового преобразователя 1, первый и вто рой выводы первого резистора 10 подключены соответственно к змиттерному и базовому выводам первого транзистор ного ключа 6, коллекторньй вывод которого подключен к коллекторному выв ду второго транзисторного ключа 7 и к выходу 38 устройствао Первый вывод -шестого резистора 15 соединен с входом разрешения мультиплексора 23, с первыми выводами четвертого 13 и пят го 14 резисторов и подключен к плюсо вой шине 32 аналогового питания, вто рой вывод шестого резистора 15 подключен к первому входу третьего операционного усилителя 20 и коллекторному выводу четвертого транзисторного ключа 29, базовьй вьгаод которого соединен с выходом третьего операционного усилителя 20, а эмиттерньй вывод подключен к первому выводу третьего резистора 12, к первому выводу первого конденсатора 9, к первому, входу схемы 21 сравнения, к второму информационному входу первой группы информационных входов мультиплексора 23 и к коллекторному выводу третьего транзисторного ключа 8, эмиттерньй вывод которого соединен с первым выводом второго конденсатора 31, с вторым выводом первого конденсатора 9, с эмиттерным выводом пятого транзисторного ключа 30, с вторым и третьим-информационными входами второй группы информационных входов и с первым информационным входом первой группы информационных входов мультиплексора 23, с первьми входами первого 2 и второго 19 операционных усилителей и подключен к шине 33 аналоговой земли, второй вывод третьего резистора 12 соединен с коллекторным выводом пятоготранзисторного ключа 30, базовый вывод которого соединен с вторым выводом четвертого резистора 13, с выходом схемы 21 сравнения и с установочным входом триггера 22, вход сброса которого соединер с выходом третьего элемента НЕ 5 и с первым входом первого элемента И-НЕ 27, инверсньй выход триггера 22 соединен с первым входом второго элемента И-НЕ 28, входы первого 3, второго 4 и третьего 5 элементов НЕ соединены, вторые входы первого 27 и второго 28 элементов И-НЕ подключены к входу 34 разрешения устройства, выходы первого 27 и второго 28 элементов И-НЕ соединены соответственно с первым и вторым управляющими входами мультиплексора 23, третий и четвертый информационные входы первой группы информационных входов которого соединены с выходом первого операционного усилителя 2, с вторым входом схемы 21 сравнения, с выводом резистора обратной связи первого цифроаналогового преобразователя 1. Выход второго операционного усилителя 19 соединен с вторым входом третьего операционного усилителя 20 и с выводом резистора обратной связи второго цифроаналогового преобразователя 18, первый и второй аналоговые выходы первого 1 и второго 18 цифроаналоговых преобразователей подключены соответственно к первым и вторым входам первого 2 и второго 19 операционных усилителей, входы опорного напряжения первого 1 и второго 18 цифроаналоговых преобразователей подключены к выходу источника 26 опорного напряжения. Группа информационных входов второго 191фроаналоГового преобразователя 18 является второй группой информационных входов 37 устройства Первьй и четвертый информационные входы второй группы информационных входов мультиплексора 23 соединены с вторым выводом пятого резистора 14 первый выход мультиплексора 23 подключен к первому входу буферного усилителя 24 и к второму выводу второго конденсатора 31, второй выход мультип лексора 23 подключен к базовому выводу третьего транзисторного ключа 8, вькод буферного усилителя 24 соедине с его вторым входом и с входом стабилизатора 25 напряжения, выход которого соединен с эмиттерным выводом первого транзисторного ключа 6, базовый вывод которого соединен с первым выво дом второго резистора 11, второй вывод которого соединен с выходом второ го элемента FIE 4, выход -первого элемента НЕ 3 подключен к базовому выводу второго транзисторного ключа 7, эмиттерньй вывод которого и минусовый вывод питания стабилизатора 25 напряжения соединены с шиной 35 цифровой земли, а плюсовый вывод питания стабилизатора 25 напряжения подключен к плюсовой шине 36 цифрового питания Устройство работает следующим образомВ исходном состоянии сигналы ЗаРазрешение и сигналы информа ционных входов первого 1 и второго 18 цифроаналоговых преобразователей имеют уровни логического нуля. Нулевой уровень сигнала Разрешение поступав ет на вторые входы первого 27 и второго 28 элементов И-НЕ и устанавливает их выходы в единичное состояние. Напряжение плюсовой шины 32 аналогового питания поступает через пятьй резистор 14 на четвертьй информационньй вход второй группы информационньк входов мультиплексора 23 и с его второго выхода на базовьй вывод третьего транзисторного ключа 8, открьшает его и разряжает первый конденсатор 9 до уровня напряжения шины 33 аналоговой земли за вычетом падения напряжения на открытом третьем транзисторном ключе 8. Нулевое напряжение с выхода первого операционного усилителя 2 поступает через четрертьй информационньй вход первой группы информационных входов мультиплексора 23 на его первый выход, далее на вход буферного усилителя 24 и с его выхода на вход дифференциального усилителя (на чертеже не показан) стабилизатора 25 напряжения, при этом на выходе стабилизатора 25 напряжения действует напряжение прямо пропорциональное напряжению, поступающему на его вход, но развязанное от аналогового питания. Напряжение с выхода стабилизатора 25 . напряжения не поступает на выход 38 устройства, так как сигнал Запуск находится в состоянии логического нуля, а выходы первого 3 и второго 4 элементов НЕ находятся в состоянии логической единицы. Уровень логической единицы выхода второго элемента НЕ 4 поступает через второй резистор 11 на базовьй вывод первого транзисторного ключа 6 и закрывает его. Второй транзисторньп ключ 7 открыт уровнем логической единицы поступающим с выхода первого элемента НЕ 3 и передает на выход 38 устройства уровень шины 35 Iy фpoвoй земли. Уровень напряжения разряженного первого конденсатора 9 поступает на первьй (неинвертируюп1ий) вход схемы 21 сравнения и, так как на ее втором (инвертирующем) входе уровень напряжения равен нулю, то выход схеьм 21 сравнения находится в состоянии логической единицы, открывает пятьй транзистор 30 и дополнительно включает цепь разрядки первого конденсатор 9. Триггер 22 находится в неопределенном состоянии „ При поступлении на группу информационных входов 17 устройства импульсов какой-либо кодовой комбинации,на первом и втором аналоговых выходах первого аналого-цифрового преобразователя 1 формируются сигналы, поступающие на первьй и второй входы первого операадонного усилителя 2, а с его выхода на второй (инвертирующий) вход схемы 21 сравнения и через четвертьй информационный вход первой группы информационных входов мультиплексора 23 на его первый .выход и далее через буферный усилитель 24 на вход дифференциального усилителя стабилизатора 25 напряжения. На выходе стабилизатора 25 напряжения формируется напряжение, пропорциональное входному. При поступлении положительного перепада импульса запуска на вход 16 запуска выходы первого 3, второго 4 и третьего 5 элементов НЕ устанавливаются в уровень логического нуля, закрывается второй транзисторный ключ 7 и открывается первый транзисторный ключ 6, а на выход 38 устройства поступает напряжение выхода стабилизатора 25 напряжения . Кроме того, нулевой уровень третьего элемента НЕ 5, поступая на вход сброса триггера 22, разрешает его работу. Таким образом, при отсутствии единичного уровня сигнала Разрешение на выход 38 устройства в течение времени действия запускающего импульса подается уровень напряжения, снимаемого с выхода стабилизатора 25 напряжения. При переходе уровня запускающего импульса из состояния логической единицы в состояние логического нуля, первый транзисторный ключ 6 закрьшается, а второй транзисторньй ключ 7 открьшается и на выход 38 устройства подается напряжение, равное

НУЛЮо

При работе устройства в режиме формирования длительности фронта на первую 17 и вторую 37 группы информационных входов устройства подаются кодовые комбинации, соответствуннцие ампли туде и длительности фронта формируемых импульсовс При поступлении сигнала Разрешение на вход 34 разрешения единичным уровнем разрешается работа первого 27 и второго 28 элементов И-НЕ. Так как сигнал Запуск, поступающий на вход 16 запуска, имеет уровень логического нуля, то выход третьего элемента НЕ 5 установлен в единичное состояние и удерживает триггер 22 в состоянии логического нуля. Выходы первого 27 и второго 28 элементов И-НЕ также находятся в состоянии логического нуля. При этом на первый и второй выходы мультиплексора 23 подаются соответственно уровни напряжений шины 33 аналоговой земли и плюсовой шины 32 аналогового питания i

Таким образом, на выход стабилизатора 25 напряжения подается уровень напряжения, равный нулю, а на первый вход схемы 21 сравнения - напряжение разряженного первого конденсатора 9 Выход схемы 21 сравнения находится в нулевом уровне, так как на ее втором входе уровень напряжения вьш1е, чем на ее первом входе, при этом пятый транзисторньй ключ 30 закрывается,, Триггер 22 заблокирован в нулевом состоянии сигналом по входу сброса. При переходе запускающего импульса в уровень логической единицы выход третьего элемента НЕ 5 устанавливается в уровень логического нуля и разрешает работу триггера 22, но блокирует первый элемент И-НЕ 27. При этом напряжение шины 33 аналоговой земли через второй информационный вход второй группы информационных входов мультиплексора 23 подается на базовый вывод третьего транзисторного ключа 8 и закрывает его. Первьй конденсатор 9 начинает заряжаться от плюсовой шины 33 аналогового питания через шестой резистор 15 и через четвертый

транзисторньй ключ 29„ Одновременно с началом заряда конденсатора напряжение с него подается на первый вход схемы 21 сравнения и на второй информационный вход первой группы информационных входов мультиплексора 23, а с его первого выхода через буферный усилитель 24 и стабилизатор 25 нап- ряжения - на эмиттерньй вывод откры,того запускающим импульсом первого

транзисторного ключа 6 и далее на выход 38 устройства. огда первый конденсатор 9 зарядится до напряжения, установленного на втором входе схемы 21 сравнения, выход схемы 21 сравнени установится в уровень логической единицы и откроет Пятьй транзисторньй ключ 30, которьй начнет медленно (т.е третий резистор 12 выбран большим), разряжать первый конденсатор 9. Это производится для поддержания напряжения на первом конденсаторе 9 постоянным.на общее время переключения триггера 22 и мультиплексора 23 о Выход схемы 21 сравнения единичным уровнем устанавливает триггер 22 в единичное состояние, инверсньй выход которого блокирует второй элемент И-НЕ 28. При этом на второй выход мультиплексора 23 начинает поступать напряжение плюсовой шины 32 аналогового питания с четвертого информационного входа вто рой группы информационных входов мул типлексора 23, а на первый выход напряжение выхода первого операционного усилителя 2, поступающее далее описанным способом на выход 38 устройствао Выход схемы 21 сравнения.устанавливается в нулевое состояние, так как первый конденсатор 9 начал разряжаться а По переходу импульса из единичного в нулевое состояние первьй транзисторный ключ 6 закрывается а второй транзисторный ключ 7 открыва ется и подает на выход 38 уровень напряжения шины 35 цифровой земли. Триггер 22 выходом третьего элемента НЕ 5 устанавливается в нулевое состояние, при этом устройство устанавливается в исходное состояние. При возникновении ситуации, когда сигнал разрешения находится в уровне логич.еской единицы, сигнал запуска - в уровне логического нуля, на вы ходе первого операционного усилителя 2 действует напряжение, равное нулю, а на выходе второго операционного усилителя 19 напряжение больше нуля, то триггер 22 может быть установлен в неопределенное состояние, так как на его обоих входах действуют уровни логической единицы,При этом на выход 38 устройства всегда коммутируется напряжение, равное нулю, так как на первый выход мультиплексора 23 поступает напряжение выхода первого операционного усилителя 2 либо через третий, либо через четвертый информационные входы первой группы информационных входов мультиплексора 23. Таким образом, в управляемом фор1.дарователе импульсов происходит регулирование длительности фронта выход.ных импульсов путем изменения кода на второй группе 37 информационных входов устройства в более пшроком динами ческом диапазоне, чем в известном устройстве Формула изобретения Управляемый формирователь импульсов, содержащий первый цифроаналоговый преобразователь, первьй операцион ный усилитель, первый, второй и третий элементы НЕ, первый, второй и тре тий транзисторные ключи, первый.:конденсатор, первый - шестой резисторы, первый и второй выводы первого резистора соединены соответственно с эмиттерным и базовым выводами первого транзисторного ключа,- коллекторные выводы первого и второго транзисторных ключей объединены, вход первого элемента НЕ является входом запуска устройства, группа информационных входов первого цифроаналогового преобразователя является первой группой информационных входов устройства, отличающийся тем, что, с целью расширения динамического диапазона длительностей фронта формируемых импульсов, в него введены второй цифроаналоговый преобразователь, второй и третий операционные усилители, схема сравнения, триггер, мультиплексор, буферный усилитель, стабилизатор напряжения, источник опорного напряжения, первый и второй элементы И-НЕ,. четвертый и пятьш транзисторные ключи и второй конденсатор, первьй вывод шестого резистора соединен с входом разрешения мультиплексора, с первыми выводами четвертого и пятого резисторов и п одключен к плюсовой гшне аналогового питания, второй вывод шестого резистора подключен к первому входу третьего операционного усилителя и к коллекторному выводу четвертого транзисторного ключа, базовьй вывод которого соединен с выходом третьего операционного усилителя, а эмиттерный вывод подключен к первому выводу третьего резистора, к первому выводу первого конденсатора, к первому входу схемы сравнения, к второму информационному входу первой группы информационных входов мультиплексора и к коллекторному выводу третьего транзисторного ключа, эмиттерньш вывод которого соединен с первым выводом второго конденсатора, с-вторым выводом первого конденсатора, с эмиттерным выводом пятого транзисторного ключа, с ВТОРЫМ и третьим информационными входами второй группы информационных входов мультиплексора и с первым информационным входом первой группы информа-, ционных входов мультиплексора, с первыми входами первого и второго операционных усилителей и подключен к шине аналоговой земли, второй вывод третьего резистора соединен с коллекторным выводом пятого транзисторного ключа, базовый вывод которого соединен с вторьм выводом четвертого резистора, с выходом схемы сравнения и с установочным входом триггера, вход сброса которого подключен к выходу третьего элемента НЕ и к первому входу первого элемента И-НЕ, инверсный выход триггера соединен с первым входом второго элемента И-ИЕ, входы первого, второго и третьего элементов НЕ объединены вторые входы первого и второго элементов И-НЕ подключены к входу разрешения устройств, а выходы соединены соответственно с первым и вторым управляющими входами мультиплексора, третий и четвертый информационные входы первой группы информационных входов которого соединены с выходом первого операционного усилителя, вторым входом схемы сравнения, выводом резистора обратной связи первого цифроаналогового преобразователя, выход второго onepaipioHHoro усилителя соединен с вторым входом третьего операционного усилителя и с выводом резисто ра обратной связи второго цифроаналогового преобразователя , первый и второй аналоговые выходы второго цифроаналогового преобразователя подключены соответственно к первому и второму входам второго операционного усилителя первьй и второй аналоговые выходы первого цифроаналогового преобразователя подключены соответственно к первому и второму входам первого операционного усилителя входы опорного напряжения первого и второго цифроаналоговых преобразователей подключены к выходу источника опорного напряжения, группа информационных входов второго цифроаналогового преобразователя является второй группой информационных входов устройства, первый и четвертый информационные входы второй группы информационных входов мультиплексора соединены с вторым выводом пятого резистора, первый выход мультиплексора подключен к первому входу буферного усилителя и к второму .выводу второго конденсатора, второй выход мультиплексора подключен к базовому выводу третьего транзисторного ключа, выход буферного усилителя соединен с его вторым входом и с входом стабилизатора напряжения, выход которого соединен с эмиттерным вьшодом первого транзисторного ключа, коллекторный вывод которого является выходом устройства, а базовый вывод соединен с первым вьшодом второго резистора, второй вывод которого соединен с выходом второго элемента НЕ, выход первого элемента НЕ подключен к базовому выводу второго транзисторного ключа, эмиттерньш вывод которого и минусовый вывод питания стабилизатора напряжения соединены с шиной цифровой земли, плюсовый вывод питания стабилизатора напряжения подключен к плюсовой шине цифрового питания.

| название | год | авторы | номер документа |

|---|---|---|---|

| УПРАВЛЯЕМЫЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 2006 |

|

RU2325027C2 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1988 |

|

SU1594699A1 |

| АНАЛОГО-ЦИФРОВАЯ МНОГОПРОЦЕССОРНАЯ СИСТЕМА | 2006 |

|

RU2333533C1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2012 |

|

RU2485681C1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СРЕДНЕКВАДРАТИЧЕСКОГО ЗНАЧЕНИЯ НАПРЯЖЕНИЯ | 2000 |

|

RU2198410C2 |

| Двухтональное устройство для звуковой предупредительной сигнализации | 1989 |

|

SU1728873A1 |

| РЕЗЕРВИРОВАННЫЙ ИСТОЧНИК ТОКА | 2013 |

|

RU2512890C1 |

| Устройство для измерения средних значений нестационарных сигналов | 1985 |

|

SU1347028A1 |

| УСТРОЙСТВО КОНТРОЛЯ ТЕХНОЛОГИЧЕСКОГО ПРОЦЕССА СЕЛЬСКОХОЗЯЙСТВЕННОГО АГРЕГАТА | 2005 |

|

RU2284014C1 |

Изобретение относится к импульсной технике. Цель изобретения - расширение динамического диапазона длительностей фронта импульсов, формируемых на выходе управляемого формирователя. Цель изобретения достигается за счет введения в устройство цифроаналогового преобразователя 18, операционных усилителей 19 и 20, схемы 21 сравнения, триггера 22, мультиплексора 23, буферного усилителя 24, стабилизатора 25 напряжения, источника 26 опорного напряжения, элементов И-НЕ 27, 28, транзисторных ключей 29, 30, конденсатора 31 и новых функциональных связей. Помимо перечисленных блоков устройство содержит цифроаналоговый преобразователь 1, операционный усилитель 2, инверторы 3-5, транзисторные ключи 6-8, конденсатор 9 и резисторы 10-15. Положительный эффект достигается за счет заряда конденсатора 9 от источника тока управляемым входным кодом при формировании выходного импульса путем переключения на выход устройства с помощью мультиплексора 23 сигналов, соответствующих начальному состоянию устройства, формируемому фронту импульса и установившемуся значению выходного импульса с запоминанием граничных значений сигнала на конденсаторе 9. 1 ил.

| Дианов АоП., Щелкунов Н.Н | |||

| Модуль программирования микросхем ПЗУ» - Микропроцессорные средства и системы | |||

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-09-30—Публикация

1988-11-01—Подача