Изобретение относится к области вычислительной техники и может быть использовано в вычислительных системах с параллельной обработкой информации смешанной формы представления.

Известны устройства [1] и [2], позволяющие осуществлять многоканальную обработку аналоговой информации, аналого-цифровое и цифроаналоговое преобразование, а также операцию деления [2], проводить дифференцирование и интегрирование [1]. К недостаткам устройств относится одноканальная загрузка цифровой информации и последовательное обслуживание каналов, что приводит к низкому быстродействию в целом.

Наиболее близким по технической сущности является аналого-цифровое множительно-делительное устройство [3], содержащее цифроаналоговый преобразователь, две запоминающие ячейки, распределитель импульсов, группу элементов И, регистр, компаратор напряжений, генератор импульсов, девять аналоговых ключей. Устройство выполняет операции умножения и деления операндов, представленных в цифровой и аналоговой форме и представляет результат в цифровой или аналоговой форме. Устройство имеет следующие недостатки:

1) низкое быстродействие, заключающееся в том, что все выполняемые операции, кроме умножения цифрового операнда на аналоговый с представлением результата в аналоговой форме, требуют нескольких циклов работы устройства;

2) ограниченные функциональные возможности, позволяющие выполнять только операции умножения и деления.

Целью изобретения является повышение быстродействия и расширение функциональных возможностей.

С целью повышения быстродействия дополнительно введены N (N>=2) процессоров. Процессоры объединены шиной цифровых данных и шиной аналоговых данных. Для управления многопроцессорной системой введен блок управления, при этом управляющие и тактовые входы процессоров подключены к соответствующим выходам блока управления. В каждый процессорный блок вводится первый аналоговый мультиплексор, выход которого подключен к сигнальному входу кодоуправляемой резистивной матрицы, адресные входы подключены к соответствующим выходам блока управления, первый вход является вторым аналоговым входом процессора, входы с 2-го по m+1-й подключены к шине аналоговых данных, вводится второй аналоговый мультиплексор, выход которого подключен к первому входу компаратора напряжений, адресные входы - к соответствующим выходам блока управления, первый вход является третьим аналоговым входом процессора, входы с 2-го по m+1-й подключены к шине аналоговых данных, вводится первый цифровой мультиплексор, выход которого подключен ко вторым входам группы элементов И, 1-й вход которого подключен к выходу второго цифрового мультиплексора, 2-й вход - к выходу компаратора напряжений, адресный вход - к соответствующим выходам блока управления. Используемый цифроаналоговый преобразователь состоит из кодоуправляемой резистивной матрицы, операционного усилителя и масштабирующего резистора, при этом управляющие входы кодоуправляемой резистивной матрицы подключены к выходам регистра, аналоговый вход - к выходу первого аналогового мультиплексора, выход - к инвертирующему входу операционного усилителя, первому выводу первого масштабирующего резистора, второй вывод которого подключен к входу ключа, второму входу компаратора напряжений, выходу операционного усилителя, неинвертирующий вход которого подключен к шине нулевого потенциала устройства. С целью расширения функциональных возможностей введен третий аналоговый мультиплексор, 1-й вход которого является первым аналоговым входом процессора, входы с 2-го по m+1-й подключены к шине аналоговых данных, адресные входы подключены к соответствующим выходам блока управления, а выход соединен с первым выводом второго масштабирующего резистора, второй вывод которого соединен с выходом кодоуправляемой резистивной матрицы, первым выводом первого масштабирующего резистора и инвертирующим входом операционного усилителя. Для обеспечения приема цифровых данных введен второй цифровой мультиплексор, адресные входы которого подключены к соответствующим выходам блока управления, выход - к первому входу первого цифрового мультиплексора, 1-й вход подключен к цифровому входу процессора, выходы с 2-го по m+1-й подключены к шине цифровых данных. Для обеспечения возможности обмена цифровыми данными между блоками в каждый блок введен сдвиговый регистр с параллельной загрузкой, подключенный входами данных к входам. цифроаналогового преобразователя и выходам регистра, управляющим и тактирующим входами - к соответствующим выходам блока управления, выходом - к шине цифровых данных.

Введение дополнительных блоков в каждый процессор позволяет осуществлять операции сложения и вычитания. Введение дополнительных процессоров и шин данных позволяет распараллеливать выполнение составных операций, требующих нескольких операций умножения и подбора кода, и одновременно использовать любым количеством процессоров данные из одной аналоговой запоминающей ячейки. Результат операции в цифровой форме может использоваться этим же процессором для последующей обработки или однократно для одновременной загрузки и обработки несколькими процессорами.

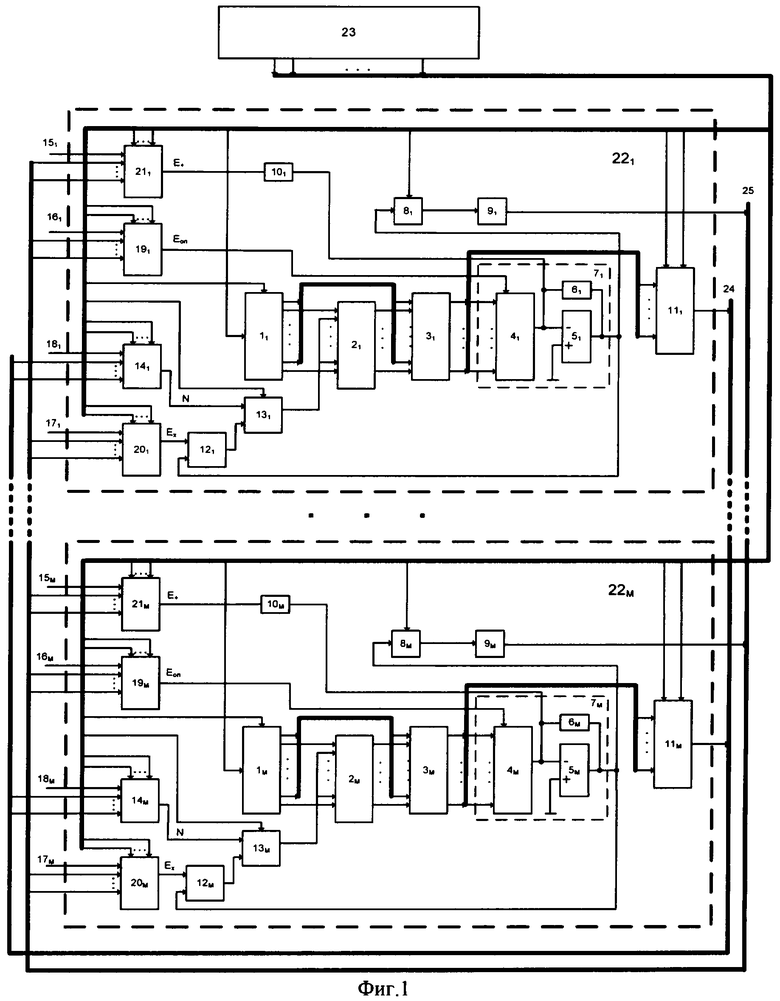

На Фиг.1 изображена структурная схема аналого-цифровой многопроцессорной системы, где

11, ..., 1M - распределители импульсов;

21, ..., 2M - группы элементов И;

31, ..., 3M - регистры;

41, ..., 4M - кодоуправляемые резистивные матрицы;

51, ..., 5M - операционные усилители;

61, ..., 6M - первые масштабирующие резисторы;

71, ..., 7M - цифроаналоговые преобразователи;

81, ..., 8M - ключи;

91, ..., 9M - аналоговые запоминающие ячейки;

101, ..., 10M - вторые масштабирующие резисторы;

111, ..., 11M - сдвиговые регистры с параллельной загрузкой;

121, ..., 12M - компараторы напряжений;

131, ..., 13M - первые цифровые мультиплексоры;

141, ..., 14M - вторые цифровые мультиплексоры;

151, ..., 15M - первые аналоговые входы процессоров;

161, ..., 16M - вторые аналоговые входы процессоров;

171, ..., 17М - третьи аналоговые входы процессоров;

181, ..., 18M - цифровые входы процессоров;

191, ..., 19M - первые аналоговые мультиплексоры;

201, ..., 20M - вторые аналоговые мультиплексоры;

211, ..., 21M - третьи аналоговые мультиплексоры;

221, ..., 22M - процессорные блоки;

23 - блок управления;

24 - шина цифровых данных;

25 - шина аналоговых данных.

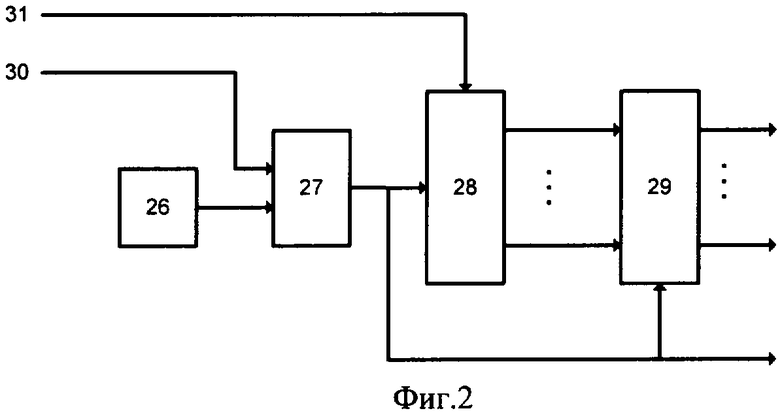

На Фиг.2 изображена структурная схема блока управления, где

26 - генератор тактовых импульсов;

27 - элемент И;

28 - счетчик;

29 - ПЗУ;

30 - первый информационный вход;

31 - второй информационный вход.

Процессор работает следующим образом.

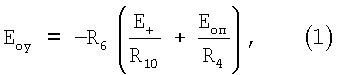

Напряжение на выходе операционного усилителя 5 описывается следующей формулой:

где Е+ - напряжение на выходе мультиплексора 21, которое выбирается с соответствующего входа при поступлении сигналов с блока 23 на адресные входы мультиплексора;

Eоп - напряжение на выходе мультиплексора 19, которое выбирается с соответствующего входа при поступлении сигналов с блока 23 на адресные входы мультиплексора;

R4 - сопротивление кодоуправляемой резистивной матрицы 4;

R6 - сопротивление масштабирующего резистора 6;

R10 - сопротивление масштабирующего резистора 10.

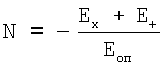

Сопротивление кодоуправляемой резистивной матрицы может быть описано следующим образом:  ,

,

где Rx - наименьшее сопротивление кодоуправляемой резистивной матрицы;

N определяется кодом, хранящимся в регистре 3, N лежит в интервале от 0 до 1-2-m, где

m - количество управляющих входов кодоуправляемой резистивной матрицы.

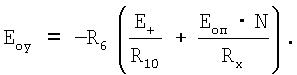

Выражение (1) преобразуется к виду:

Тогда при R6=R10=Rx

Eоу=-(E++Eоп·N).

Процессор имеет два режима работы.

Режим 1.

В этом режиме результат операции представлен сигналом на выходе цифроаналогового преобразователя. ЕЦАП=Еоу=-(N·Eоп+Е+). Если для выполнения операции необходим цифровой операнд, отличный от имеющегося в регистре 3, то сначала выполняется загрузка цифрового кода. Цифровой код загружается в регистр 3 последовательно с выхода мультиплексора 14, начиная со старших разрядов при подаче блоком управления 23 нулевого сигнала на адресный вход мультиплексора 13 и разрешающего сигнала на управляющий вход распределителя импульсов 1. При этом распределитель импульсов 1 вырабатывает последовательность импульсов, каждый из которых сдвинут на такт относительно предыдущего. Нечетные импульсы с нечетных входов распределителя импульсов 1 последовательно устанавливают в "единицу" разряды регистра 3, а четные импульсы через группу 2 элементов И при наличии разрешающего потенциала на выходе компаратора напряжений сбрасывают соответствующие разряды в "нуль", а при наличии запрещающего потенциала - оставляют соответствующие разряды в "единице". По окончании загрузки в регистре 3 записан цифровой код. Результат операции записывается в запоминающую ячейку 9 при поступлении разрешающего сигнала из блока управления 23 на управляющий вход ключа 8.

Режим 2.

В этом режиме результат операции представлен кодом в регистре 3. При подаче единичного сигнала на адресный вход мультиплексора 13 осуществляется подбор кода, уравновешивающего сигналы с выхода цифроаналогового преобразователя 7 и выхода мультиплексора 20 на входах компаратора напряжений 12. При наличии разрешающего сигнала с блока управления 23 на управляющем входе распределителя импульсов 1, совершается цикл преобразования, по завершении которого достигается равенство

Еx=ЕЦАП,

где Ex - сигнал на выходе аналогового мультиплексора 20;

ЕЦАП - сигнал на выходе цифроаналогового преобразователя 7.

EЦАП=Eоу=-(N·Eоп+E+)

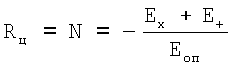

Соответственно, Ех=-N·Еоп-Е+. Таким образом, по окончании операции в регистре 3 записан код  . При поступлении управляющего сигнала из блока 23 на вход записи сдвигового регистра с параллельной загрузкой 11 код из регистра 3 записывается в регистр 11.

. При поступлении управляющего сигнала из блока 23 на вход записи сдвигового регистра с параллельной загрузкой 11 код из регистра 3 записывается в регистр 11.

Возможны следующие частные случаи, которые определяют базовые операции, выполняемые одним процессором:

1) операция умножения со сложением и инверсией Rа=Еоу=-(Е++Еоп·N);

2) операция умножения с инверсией Rа=Еоу=-Еоп·N, при Е+=0;

3) операция сложения с инверсией Ra=Еoy=-(Е++Еоп), при N=1;

4) операция инверсии цифрового операнда с представлением результата в аналоговой форме Rа=Еоу=-N, при Еоп, принятом за единицу;

5) операция инверсии аналогового операнда Ra=Еоу=-Е+, при N=0;

6) операция деления со сложением и инверсией  ;

;

7) операция деления с инверсией  , при E2=0;

, при E2=0;

где Ra - результат операции в аналоговой форме, записываемый в запоминающую ячейку 9 при поступлении управляющего сигнала на ключ 8;

Rц - результат операции в цифровой форме, записанный в регистр 3.

Многопроцессорная система работает следующим образом.

Аналоговая величина, хранящаяся в запоминающей ячейке 9, i-го процессора 22i доступна по шине аналоговых данных 25 любым процессорам 22j1, ..., 22jk и может быть использована в качестве Eоп, Ех, E+ при подаче на мультиплексоры 19, 20, 21 соответственно требуемых адресов блоком 23. Цифровая величина, хранящаяся в регистре 11i процессора 22i, доступна для одновременного однократного считывания любым процессорам 22j1, ..., 22jk в качестве Ny при подаче на мультиплексоры 14 соответствующих адресов блоком 23. При поступлении сигналов с тактового выхода блока 23 на тактовый вход регистра 11 значение, записанное в регистре 11, последовательно передается по шине цифровых данных.

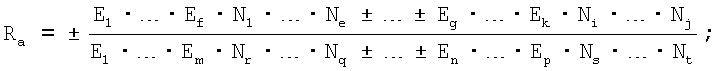

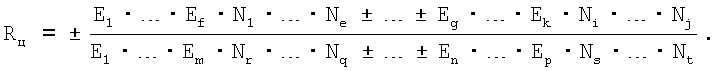

Многопроцессорная система позволяет выполнять операции вида

Каждая операция разбивается на несколько базовых операций так, что каждая базовая операция может выполняться одним процессором, что позволяет конвейеризировать вычисление результата, причем часть базовых операций может выполняться параллельно несколькими процессорами.

При поступлении соответствующих сигналов из блока управления многопроцессорная система позволяет параллельно выполнять операции над операндами, поступающими как на аналоговые, так и на цифровые входы системы и организовать параллельную выдачу аналоговой и цифровой информации на выходы системы.

Блок управления работает следующим образом.

При установлении на первом информационном входе 30 блока потенциала логической единицы и потенциале логического нуля на входе 31 тактовые импульсы с выхода генератора тактовых импульсов 26 через элемент 27 И поступают на тактирующий вход счетчика 28. При этом на выходе счетчика появляются последовательно возрастающие двоичные коды, поступающие на адресные входы ПЗУ 29. По тактовому импульсу считанные из ПЗУ 29 микрокоманды поступают на выходы блока управления. При наличии на первом информационном входе 30 потенциала логического нуля работа блока синхронизации приостанавливается. При появлении на втором информационном входе 31 потенциала логической единицы счетчик 28 сбрасывается в ноль. Блок управления может быть выполнен иным образом.

Источники информации

1. Авторское свидетельство СССР №1388913 от 19.03.86.

2. Авторское свидетельство СССР №1564606 от 08.02.88.

3. Авторское свидетельство РФ №2121712 от 4.08.97 - прототип.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Цифроаналоговая вычислительная система | 1987 |

|

SU1483468A1 |

| Устройство для решения нелинейных задач теории поля | 1983 |

|

SU1156101A1 |

| Цифровой измерительный мост | 1988 |

|

SU1656469A1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| Устройство для определения среднего значения выборочного размаха | 1984 |

|

SU1363252A1 |

| УСТРОЙСТВО ДЛЯ СБОРА И ОБРАБОТКИ ДАННЫХ | 2002 |

|

RU2218597C2 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| Устройство для определения модуля @ -мерного вектора | 1987 |

|

SU1481806A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СИГНАЛА ЗАПУСКА МНОГОКАНАЛЬНОЙ ИНФОРМАЦИОННО-ИЗМЕРИТЕЛЬНОЙ СИСТЕМЫ | 1994 |

|

RU2079880C1 |

Изобретение относится к области вычислительной техники и может быть использовано в вычислительных системах с параллельной обработкой информации смешанной формы представления. Техническим результатом является расширение функциональных возможностей и повышение быстродействия. Он достигается тем, что система содержит М процессорных блоков, шину цифровых данных, шину аналоговых данных, блок управления. Процессорный блок содержит распределитель импульсов, группу элементов И, регистр, цифроаналоговый преобразователь, ключ, запоминающую ячейку, масштабирующий резистор, сдвиговый регистр с параллельной загрузкой, компаратор, два цифровых мультиплексора, три аналоговых мультиплексора. 2 ил.

Аналого-цифровая многопроцессорная система, содержащая процессор, который содержит распределитель импульсов, первая группа выходов которого подключена к единичным установочным входам регистра, нулевые установочные входы которого подключены к выходам группы элементов И, первые входы которой подключены ко второй группе выходов распределителя импульсов, при этом выходы регистра подключены к управляющим входам кодоуправляемой резистивной матрицы, выход которой подключен к первому выводу первого масштабирующего резистора и инвертирующему входу операционного усилителя, неинвертирующий вход которого соединен с шиной нулевого потенциала устройства, а выход подключен к второму выводу первого масштабирующего резистора, второму входу компаратора и сигнальному входу ключа, выход которого подключен к аналоговой запоминающей ячейке, отличающаяся тем, что в процессор введены первый, второй и третий аналоговые мультиплексоры, первый и второй цифровые мультиплексоры, второй масштабирующий резистор и сдвиговый регистр с параллельной загрузкой, подключенный тактирующим входом и входом записи к соответствующим выходам блока управления, а входами загрузки - к выходам регистра и управляющим входам кодоуправляемой резистивной матрицы, сигнальный вход которой подключен к выходу первого аналогового мультиплексора, адресные входы которого подключены к соответствующим выходам блока управления, 1-й информационный вход является вторым аналоговым входом устройства, входы с 2-го по m+1-й подключены к шине аналоговых данных, к которой также подключены информационные входы с 2-го по m+1-й второго аналогового мультиплексора, 1-й информационный вход которого является третьим аналоговым входом устройства, адресные входы подключены к соответствующим выходам блока управления, а выход - к первому входу компаратора, выход которого подключен к второму входу первого цифрового мультиплексора, выход которого подключен ко вторым входам группы элементов И, адресный вход подключен к соответствующему выходу блока управления, а первый вход подключен к выходу второго цифрового мультиплексора, 1-й информационный вход которого является цифровым входом устройства, входы 2-го по m+1-й подключены к шине цифровых данных, а адресные входы - к соответствующим выходам блока управления, также к соответствующим выходам блока управления подключены тактирующий и управляющий входы распределителя импульсов и управляющий вход ключа, выход кодоуправляемой резистивной матрицы соединен с вторым выводом второго масштабирующего резистора, первый вывод которого соединен с выходом третьего аналогового мультиплексора, адресные входы которого подключены к соответствующим выходам блока управления, 1-й информационный вход является первым аналоговым входом устройства, входы с 2-го по m+1-й подключены к шине аналоговых данных, также введены М-1 процессоров, идентичных с указанным выше процессором, при этом выходы сдвиговых регистров с параллельной загрузкой процессоров и входы с 2-го по m+1-й вторых цифровых мультиплексоров процессоров подключены к шине цифровых данных, соединенной с цифровыми выходами системы, выходы аналоговых запоминающих ячеек и входы с 2-го по m+1-й первых, вторых и третьих аналоговых мультиплексоров процессоров подключены к шине аналоговых данных, соединенной с аналоговыми выходами системы, а первые входы первого, второго и третьего аналоговых мультиплексоров процессоров подключены к внешним аналоговым входам системы, первые выходы цифровых мультиплексоров подключены к цифровым входам системы.

| АНАЛОГО-ЦИФРОВОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1997 |

|

RU2121712C1 |

| Аналого-цифровое вычислительное устройство | 1986 |

|

SU1388913A1 |

| Множительно-делительное устройство | 1976 |

|

SU674042A1 |

| Многоканальное устройство для ввода-вывода аналоговой информации | 1988 |

|

SU1564606A1 |

| JP 2001034735, 09.02.2001 | |||

| МАРКИРОВОЧНЫЙ МОДУЛЬ | 1993 |

|

RU2088990C1 |

Авторы

Даты

2008-09-10—Публикация

2006-12-04—Подача