Фиг.

Изобретение относится к импульсной технике, в частности к делителям частоты следования импульсов со счетными цепочками,в которых основание сиетемы счисления является дробным числом, и может быть использовано в устройствах для синтеза сигналов необходимых частот, например в синтезаторах частот, системах автоматического управления и контроля,

Цель изобретения - повышение быстродействия при одновременном расширении диапазона коэффициентов деления.

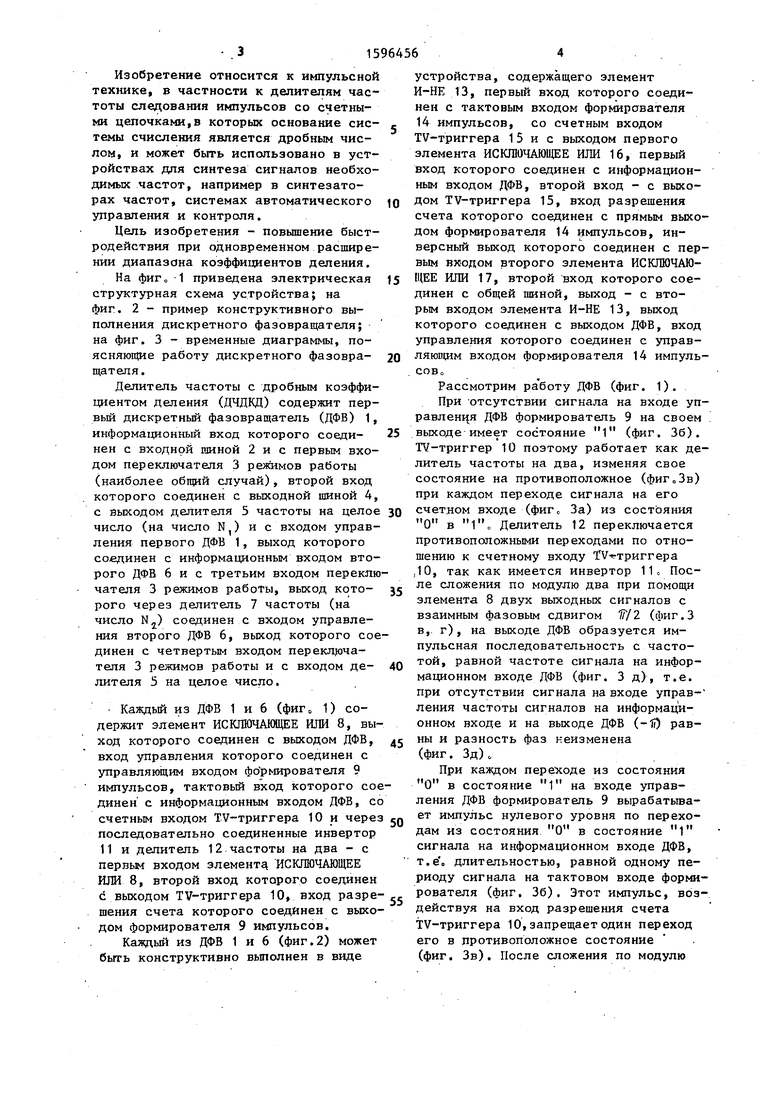

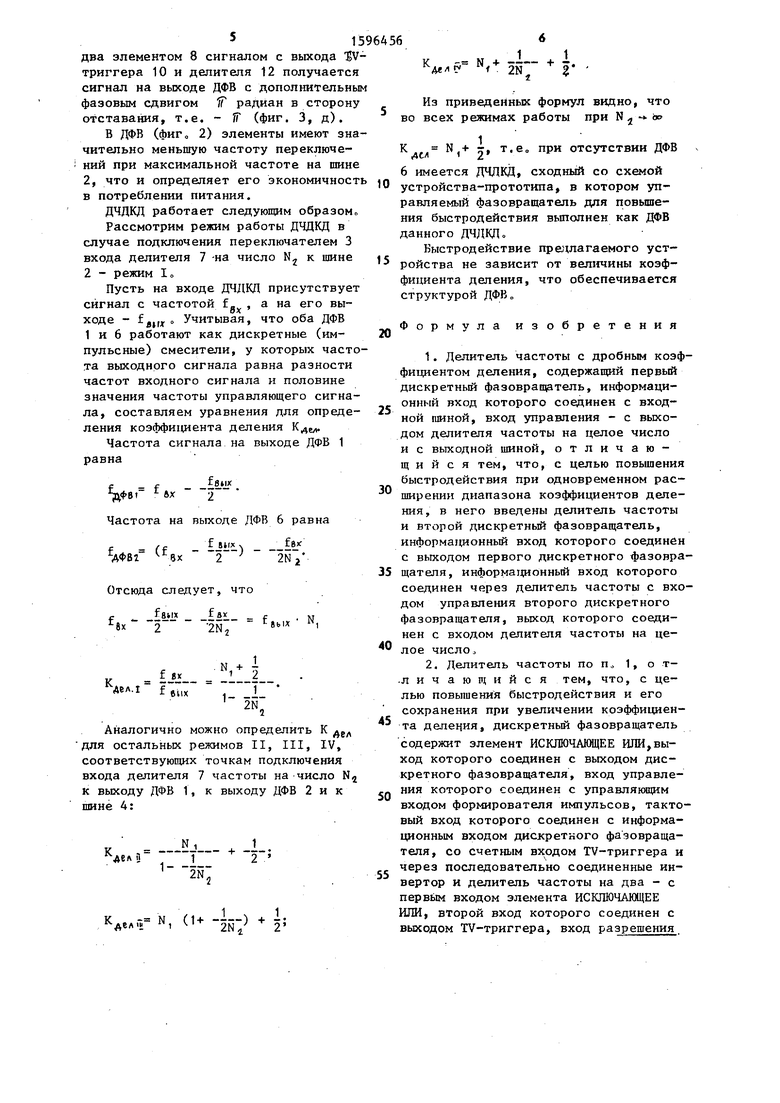

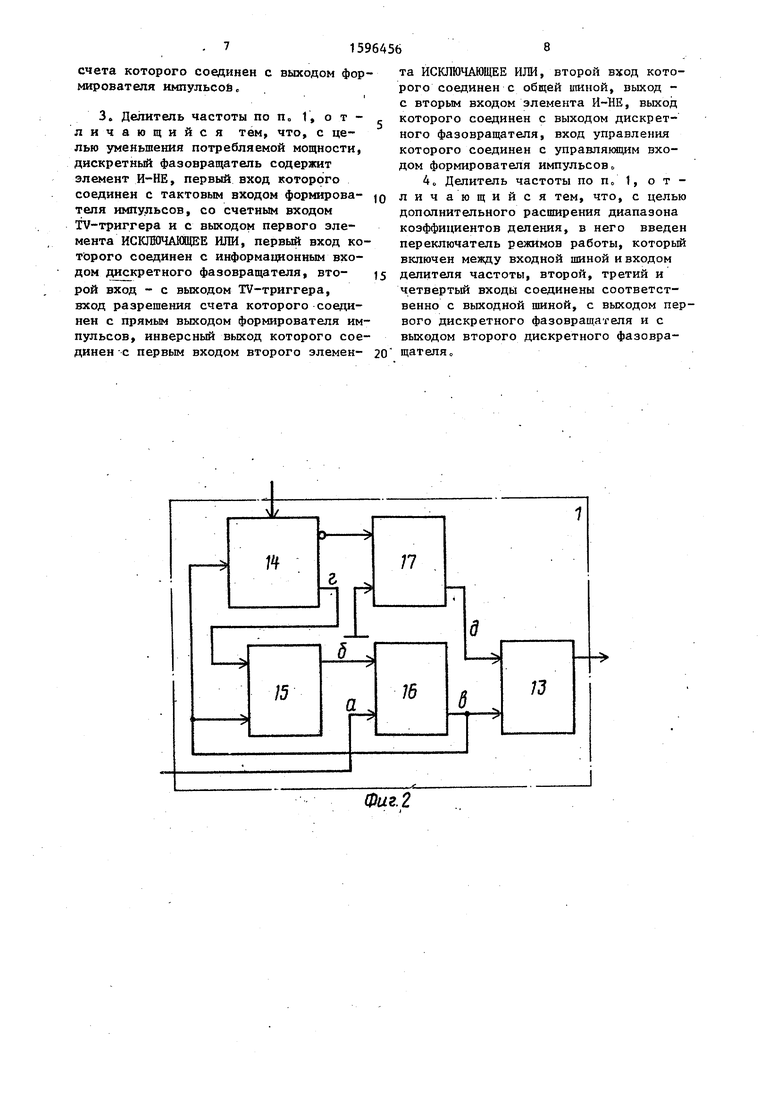

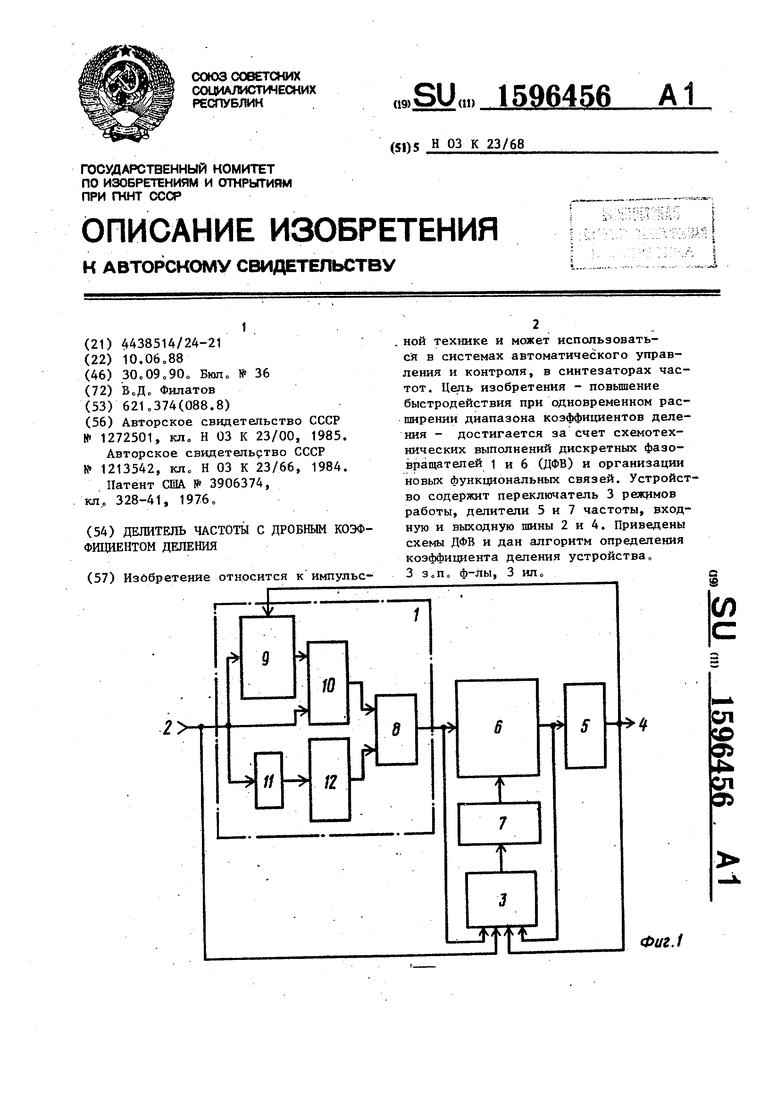

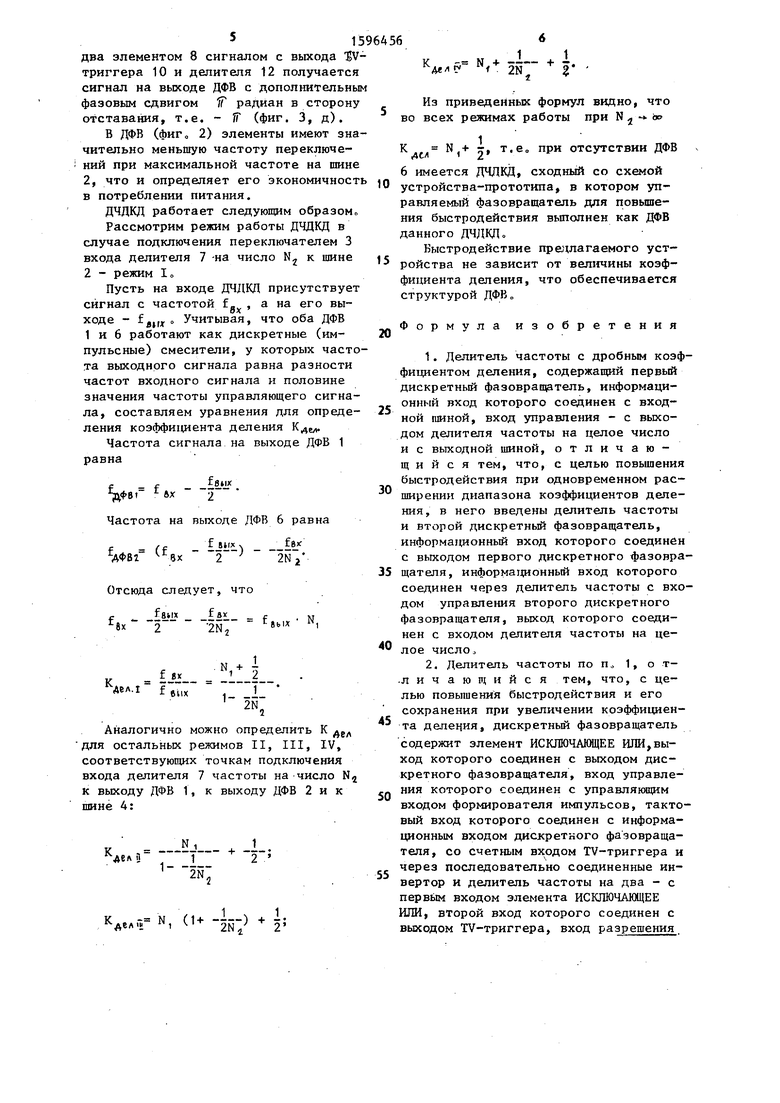

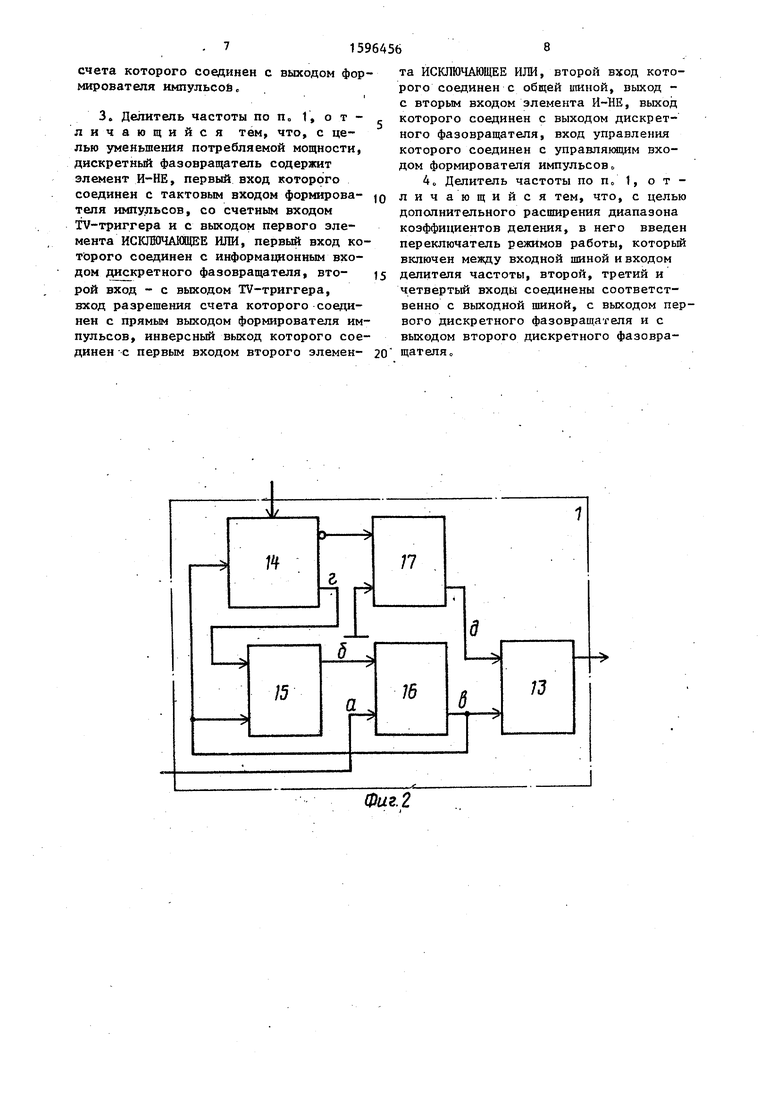

На фиГо -1 приведена злектрическая структурная схема устройства; на фиг. 2 - пример конструктивного выполнения дискретного фазовращателя; на фиг. 3 - временные диаграммы, поясняюп ие работу дискретного фазовращателя.

Делитель частоты с дробным коэффициентом деления (ДЧДКД) содержит первый дискретньш фазовращатель (ДФВ) 1, информационный вход которого соединен с входной шиной 2 и с первым входом переключателя 3 реясимов работы (наиболее общий случай), второй вход которого соединен с выходной шиной 4, с выходом делителя 5 частоты на целое число (на число N,) и с входом управления первого ДФВ 1, выход которого соединен с информационным входом второго ДФВ бис третьим входом переключателя 3 режимов работы, выход которого через делитель 7 частоты (на число NJ) соединен с входом управления второго ДФВ 6, выход которого соединен с четвертым входом перекл очателя 3 режимов работы и с входом делителя 5 на целое число.

Каждый из ДФВ 1 и 6 (фиго 1) содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 8, выход которого соединен с выходом ДФВ, вход управления которого соединен с управляющим входом формирователя 9 импульсов, тактовый вход которого соединен с информационным входом ДФВ, со счетньм входом TV-триггера Ю и через последовательно соединенные инвертор 11 и делитель 12 частоты на два - с первым входом элементу ИСКЛЮЧАЮЩЕЕ ИЛИ 8, второй вход которого соединен с выходом TV-триггера 10, вход разрешения счета которого соединен с выходом формирователя 9 импульсов.

Каждый из ДФВ 1 и 6 (фиг.2) может быть конструктивно выполнен в виде

устройства, содержащего элемент И-НЕ 13, первый вход которого соединен с тактовым входом формирователя 14 импульсов, со счетным входом TV-триггера 15 и с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 16, первьй вход которого соединен с информационным входом ДФВ, второй вход - с выходом TV-триггера 15, вход разрешения счета которого соединен с прямым выходом формирователя 14 импульсов, инверсный выход которого соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 17, второй вход которого соединен с общей пиной, выход - с вторым входом элемента И-НЕ 13, выход которого соединен с выходом ДФВ, вход управления которого соединен с управляющим входом формирователя 14 импульсов

Рассмотрим работу ДФВ (фиг. 1).

При -отсутствии сигнала на входе управлен1|я ДФВ формирователь 9 на своем выходе имеет состояние 1 (фиг. 36). TV-триггер 10 поэтому работает как делитель частоты на два, изменяя свое состояние на противоположное (фиг„3в) при каждом переходе сигнала на его счет.ном входе (фиг с За) из состояния О в Делитель 12 переключается противоположными переходами по отношению к счетному входу TV TpHrrepa ,10, так как имеется инвертор 11« После сложения по модулю два при помощи злемента 8 двух выходньк сигналов с взаимным фазовым сдвигом Т/2 (фиг.З в, г), на выходе ДФВ образуется импульсная последовательность с частотой, равной частоте сигнала на информационном входе ДФВ (фиг. 3 д), т.е. при отсутствии сигнала на входе управления частоты сигналов на информационном входе и на выходе ДФВ (-10 равны и разность фаз кеизменена (фиг. Зд),

При каждом переходе из состояния О в состояние 1 на входе управления ДФВ формирователь 9 вырабатьгоает импульс нулевого уровня по переходам из состояния О в состояние 1 сигнала на информационном входе ДФВ, т.ео длительностью, равной одному периоду сигнала на тактовом входе формирователя (фиг. Зб), Этот импульс, воздействуя на вход разрешения счета tv-триггера 10,запрещает один переход его в противоположное состояние (фиг, Зв). После сложения по модулю 5 два элементом 8 сигналом с выхода 5 триггера 10 и делителя 12 получаетс сигнал на выходе ДФВ с дополнительн фазовым сдвигом Г радиан в сторон отставания, т.е. - 1Г (фиг. 3, д). В ДФВ (фиг о 2) элементы имеют зн чительно меньшую частоту переключений при максимальной частоте на шин 2, что и определяет его экономичнос в потреблении питания. ДЧДКД работает следующим образом Рассмотрим режим работы ДЧДКД в случае подключения переключателем 3 входа делителя 7 -на число N к шине 2 - режим 1о Пусть на входе ДЧДКД присутствуе сигнал с частотой „ , а на его выходе - f e,,;f о Учитывая, что оба ДФВ 1 и 6 работают как дискретные (импульсные) смесители, у которых част та выходного сигнала равна разности частот входного сигнала и половине значения частоты управляющего сигна ла, составляем уравнения для опреде ления коэффихщента деления К Частота сигнала на выходе ДФВ 1 равна 1ХФВ1 ftx Частота на выходе ДФВ 6 равна f вИ1 WBI вх 2 Отсюда следует, что fax , Аналогично можно определить К д для остальньк режимов II, III, IV, соответствующих точкам подключения входа делителя 7 частоты на -число N к выходу ДФВ 1, к выходу ДФВ 2 и к шине 4: с -ь-; - N дел «Е 1 6 1-- + 1 Кде.е Nf2N г Из приведенных формул видно, что во всех режимах работы при ТИ ьо т.е., при отсутствии ДФВ А(-л 1- 2 6 имеется ДЧДКД, сходный со схемой устройства-прототипа, в котором управляемый фазовращатель для повьшения быстродействия вьшолнен как ДФВ данного ДЧДКДо Быстродействие предлагаемого устройства не зависит от величины коэффициента деления, что обеспечивается структурой ДФВ„ Формула изобретения 1.Делитель частоты с дробным коэффициентом деления, содержащий первый дискретньй фазовращатель, информационный вход которого соединен с входной шиной, вход управления - с выходом делитепя частоты на целое число и с выходной шиной, отличающийся тем, что, с целью повышения быстродействия при одновременном расширении диапазона коэффициентов деления, в него введены делитель частоты и второй дискретньй фазовращатель, информа1Ц1онный вход которого соединен с выходом первого дискретного фазовращателя, информационный вход которого соединен через делитель частоты с входом управления второго дискретного фазовращателя, выход которого соединен с входом делителя частоты на целое число, 2.Делитель частоты по п 1, о тличающийся тем, что, с целью повышения быстродействия и его сохранения при увеличении коэффициента деления, дискретньй фазовращатель содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ,выход которого соединен с выходом дискретного фазовращателя, вход управления которого соединен с управляющим входом формирователя импульсов, тактовый вход которого соединен с информационным входом дискретного фазовращателя, со счетным входом TV-триггера и через последовательно соединенные инвертор и делитель частоты на два - с первьм входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом TV-триггера, вход разрешения счета которого соединен с выходом фор мирователя импульсой. 3. Делитель частоты по п„ 1, отличающийся тем, что, с целью уменьшения потребляемой мощности, дискретный фазовращатель содержит элемент И-НЕ, первый вход которого соединен с тактовым входом формирователя импульсов, со счетным входом TV-триггера и с выходом первого элемента ИСКЛЮЧАКЩБЕ ИЛИ, первый вход ко торого соединен с информационным входом дискретного фазовращателя, второй вход - с выходом TV-триггера, вход разрешения счета которого -соединен с прямым выходом формирователя им пульсов, инверсный выход которого сое динен -с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с общей шиной, выход с вторым входом элемента И-НЕ, выход которого соединен с выходом дискретного фазовращателя, вход управления которого соединен с управлякнцим входом формирователя импульсов 4 о Делитель частоты по По 1, отличающийся тем, что, с целью дополнительного расширения диапазона коэффициентов деления, в него введен переключатель режимов работы, который включен между входной шиной и входом делителя частоты, второй, третий и четвертый входы соединены соответственно с выходной шиной, с выходом первого дискретного фазовращателя и с выходом второго дискретного фазовращателя

| название | год | авторы | номер документа |

|---|---|---|---|

| Дискретный фазовращатель | 1985 |

|

SU1338005A1 |

| Устройство для измерения времени установления цифроаналогового преобразователя | 1986 |

|

SU1432776A1 |

| Измерительный преобразователь активной и реактивной составляющих синусоидального тока | 1990 |

|

SU1748079A1 |

| Цифровой низкочастотный частотомер | 1981 |

|

SU966619A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1272509A1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1833966A1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Многофазный цифровой фазовращатель | 1978 |

|

SU790210A1 |

| Управляемый делитель частоты следования импульсов | 1983 |

|

SU1088136A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

Изобретение относится к импульсной технике и может использоваться в системах автоматического управления и контроля, в синтезаторах частот. Цель изобретения - повышение быстродействия при одновременном расширении диапазона коэффициентов деления - достигается за счет схемотехнических выполнений дискретных фазовращателей 1 и 6 (ДФВ) и организации новых функциональных связей. Устройство содержит переключатель 3 режимов работы, делители 5 и 7 частоты, входную и выходную шины 2 и 4. Приведены схемы ДФВ и дан алгоритм определения коэффициента деления устройства. 3 з.п. ф-лы, 3 ил.

15

/J

Ю

Фие.2

Фиг.З

| Делитель частоты следования импульсов | 1985 |

|

SU1272501A1 |

Авторы

Даты

1990-09-30—Публикация

1988-06-10—Подача