сл

со

1

сл

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1982 |

|

SU1088016A1 |

| Преобразователь активной мощности в цифровой код | 1985 |

|

SU1275308A1 |

| Множительно-делительное устройство | 1977 |

|

SU696444A1 |

| Интегратор | 1982 |

|

SU1062726A1 |

| Цифровой измеритель параметров | 1977 |

|

SU702317A1 |

| Цифровой измеритель -параметров | 1978 |

|

SU788036A1 |

| Измеритель энергии искры | 1981 |

|

SU1013866A1 |

| Множительно-делительное устройство | 1980 |

|

SU934494A1 |

| Измерительный преобразователь активной мощности | 1985 |

|

SU1308910A1 |

| Множительно-делительное устройство | 1978 |

|

SU1095195A1 |

Изобретение относится к электроизмерительной технике и может найти применение при построении быстродействующих преобразователей автоматизированных систем управления энергообъектами. Целью изобретения является повышение быстродействия и расширение частотного диапазона. Цель достигается введением в устройство второго ключа 6, второго интегратора 5, множительно-делительного блока 1, источника 7 опорного напряжения, дифференцирующий цепи 9 и схемы 10 задержки. Формирователь 8, ключ 6, интегратор 5 формируют в первом такте напряжение, подаваемое на вход делителя множительно-делительного блока 1, которое во втором такте нормирует сигнал мгновенной мощности, интегрируемый интегратором 2. Длительность каждого такта составляет половину периода основной частоты измеряемой сети. При этом время всего преобразования равно периоду сети. Устройство обладает высокой точностью в широком диапазоне входных токов и напряжений, поскольку множительно-делительный блок 1 работает в линейном режиме. Устройство также содержит ключ 3, блок 4 памяти. 2 ил.

ФигЛ

Изобретение относится к электроизмерительной технике и может быть использовано при построении быстро- действуницих преобразователей автома- тизированных систем управления энергообъектами.

Цель изобретения - повьппение быстродействия и расширение частотного диапазоч.а.

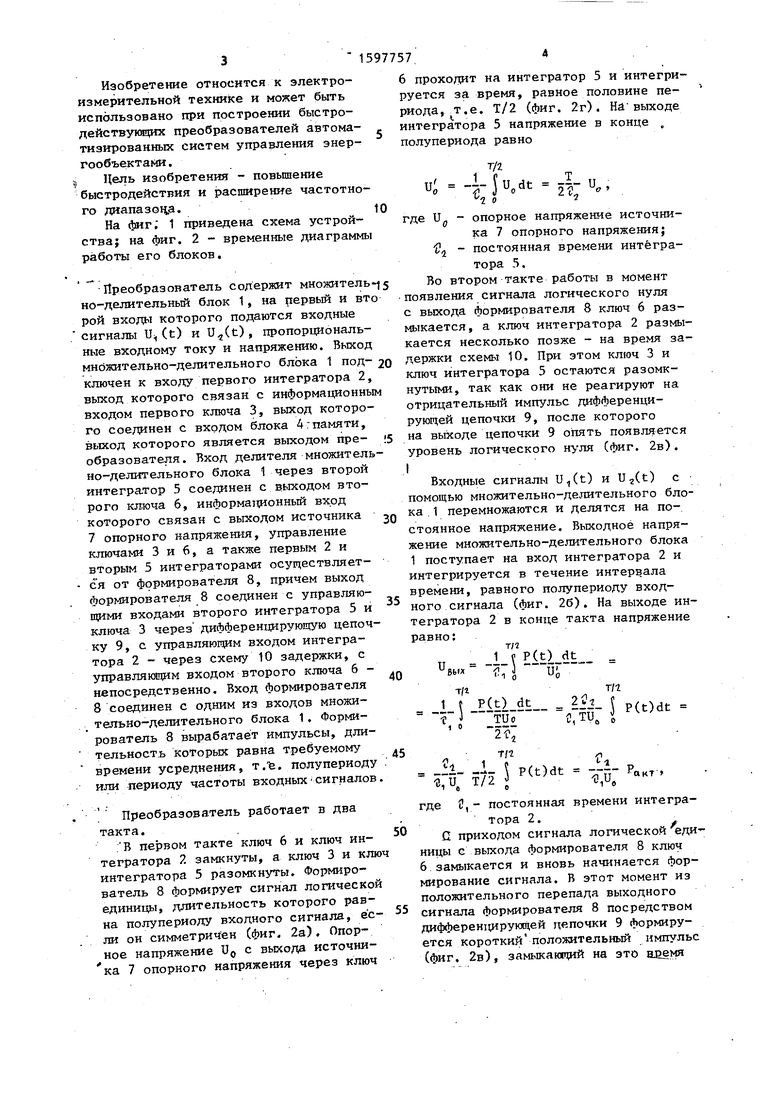

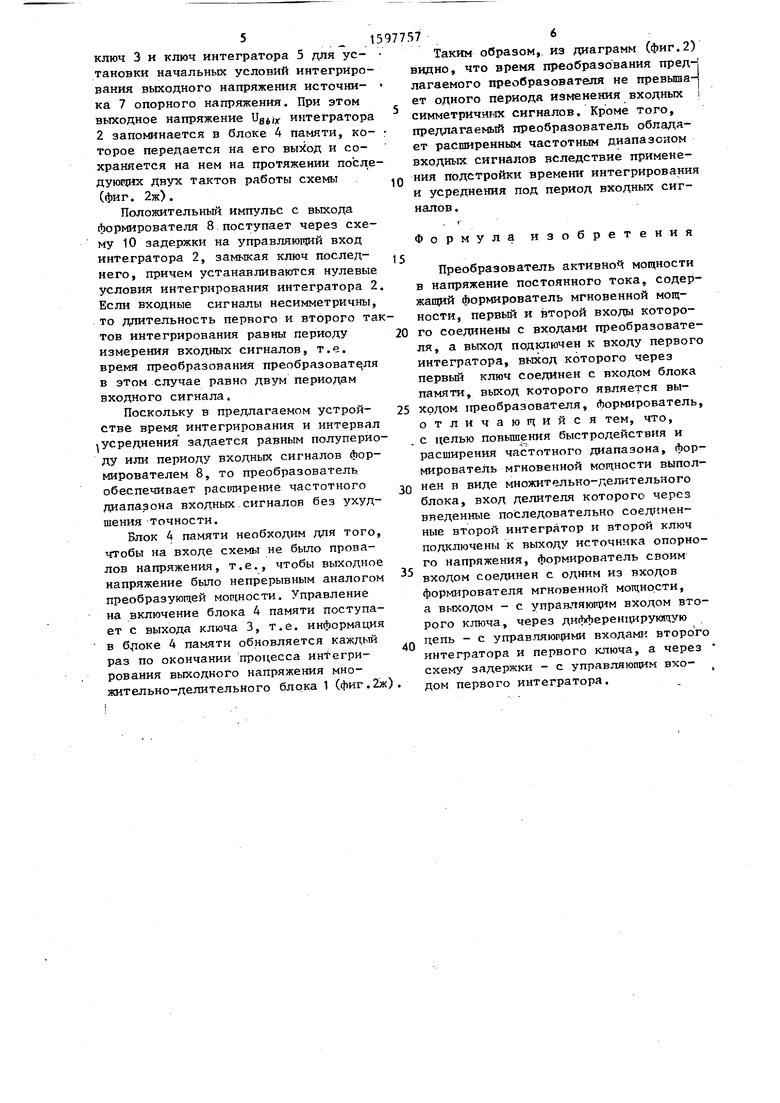

На фиг; 1 приведена схема устройства; на фиг. 2 - временные диаграммы работы его блоков.

Преобразователь содержит множитель 5 но-делительный блок 1 , на рервый и вто рой входы которого подаются входные

сигналы и, (t) и U(t), пропорциональные входному току и напряжению. Выход

6 проходит на интегратор 5 и интегрируется за время, равное половине пеI JtilV-Д v l f- ,

риода, т.е. Т/2 (фиг. 2т). Ни выходе интегратора 5 напряжение в конце полупериода равно

и;

т/2

1 е Т

-

и

о

2 о

где Up - опорное напряжение источника 7 опорного напряжения; tl- - постоянная времени интегратора 5.

Во втором такте работы в момент появления сигнала логического нуля с выхода формирователя 8 ключ 6 размыкается, а ключ интегратора 2 размыкается несколько позже - на время за .1

iiLTO nvnnHnMV TOKV И напряжению. JJPIAUM

Г.ГГ„е™ л.о™ а..„а , „о„- .0 f :еГ,Паз1к

ключен к входу первого интегратора 2, выход которого связан с информационным входом первого ключа 3, выход которого соединен с входом блока 4:памяти, выход которого является выходом преобразователя. Вход делителя множитель- но-делительного блока 1 через второй интегратор 5 соединен с выходом второго ключа 6, информационный вход которого связан с вьпсодом источника 7 опорного напряжения, управление ключами 3 и 6, а также первым 2 и вторым 5 интеграторами осуществляет- - с я от формирователя 8, причем выход

ключ интегратора 5 остаются разомкнутыми, так как они не реагируют на отрицательный импульс дифференцирующей цепочки 9, после которого на выходе цепочки 9 опять появляется уровень логического нуля (фиг. 2в). I

30

равно:

40

и

вЬ1Х

т/1

т/7

1 V P(t) dt

иГ

1 S

Входные сигналы U,(t) и U2(t) с помощью множительно-делительного блока 1 перемножаются и делятся на постоянное напряжение. Выходное напряжение множительно-делительного блока 1 поступает на вход интегратора 2 и интегрируется в течение интервала

ГоР«РоГа-;в :в сов„„ е„ .пра,л„„- , й Т Г-нПьГдГин- laTfe / SeZp Snr,- .:гра:ора 2 JKOH,. .ак.а напряжение ку 9, С управляющим входом интегра- тора 2 - через схему Ю задержки, с управлякацим входом второго ключа 6 - непосредственно. Вход формирователя 8 соединен с одним из входов множительно-делительного блока 1. Форми- рователь В вырабатаёт импульсы, длительность которых равна требуемому времени усреднения, T.-fe. полупериоду или .периоду частоты входных.сигналов.

Преобразователь работает в два

такта. .

В первом такте ключ 6 и ключ интегратора 2 замкнуты, а ключ 3 и ключ интегратора 5 разомкнуты. Формиро- ватель 8 формирует сигнал логической единицы, длительность которого рав- на полупериоду входного сигнала, если он симметричен (фиг. 2а). Опорное напряжение Uo с выхода источии- ка 7 опорного напряжения через ключ

-г,ггп

.1 t 2|j j p(d, t J TUo C,TU, i

1 0

45

.v Tl-i

Ji

где

L

cr Ш -4-

я 50

постоянная времени интегратора 2. С приходом сигнала логической единицы с выхода формирователя 8 ключ 6 замыкается и вновь начиняется формирование сигнала. В этот момент из положительного перепада выходного сигнала формирователя 8 посредством дифферен1у1РУмщей цепочки 9 формируется короткий положительный импульс (фиг. 2в), замьжанщий на это авемя

1597757,

6 проходит на интегратор 5 и интегрируется за время, равное половине пеI JtilV-Д v l f- ,

риода, т.е. Т/2 (фиг. 2т). Ни выходе интегратора 5 напряжение в конце полупериода равно

т/2

1 е Т

-

и

о

2 о

где Up - опорное напряжение источника 7 опорного напряжения; tl- - постоянная времени интегратора 5.

Во втором такте работы в момент появления сигнала логического нуля с выхода формирователя 8 ключ 6 размыкается, а ключ интегратора 2 размыкается несколько позже - на время за .1

f :еГ,Паз1к

f :еГ,Паз1к

ключ интегратора 5 остаются разомкнутыми, так как они не реагируют на отрицательный импульс дифференцирующей цепочки 9, после которого на выходе цепочки 9 опять появляется уровень логического нуля (фиг. 2в). I

Входные сигналы U,(t) и U2(t) с помощью множительно-делительного блока 1 перемножаются и делятся на постоянное напряжение. Выходное напряжение множительно-делительного блока 1 поступает на вход интегратора 2 и интегрируется в течение интервала

равно:

0

и

вЬ1Х

т/1

т/7

1 V P(t) dt

иГ

1 S

, й Т Г-нПьГдГи .:гра:ора 2 JKOH,. .ак.а напряжен

-г,ггп

.1 t 2|j j p(d, t J TUo C,TU, i

1 0

, й Т Г-нПьГдГин- .:гра:ора 2 JKOH,. .ак.а напряжение

5

.v Tl-i

Ji

где

L

cr Ш -4-

я 50

постоянная времени интегратора 2. С приходом сигнала логической единицы с выхода формирователя 8 ключ 6 замыкается и вновь начиняется формирование сигнала. В этот момент из положительного перепада выходного сигнала формирователя 8 посредством дифферен1у1РУмщей цепочки 9 формируется короткий положительный импульс (фиг. 2в), замьжанщий на это авемя

5 15

ключ 3 и ключ интегратора 5 для ус- тановки начальных условий интегрирования выходного напряжения источни- ка 7 опорного напряжения. При этом выходное напряжение etix интегратора 2 запоминается в блоке 4 памяти, которое передается на его вы54од и сохраняется на нем на протяжении последующих двух тактов работы схемы (фиг. 2ж).

Положительный импульс с выхода формирователя 8 поступает через схему 10 задержки на управляющий вход интегратора 2, замыкая ключ последнего, причем устанавливаются нулевые условия интегрирования интегратора 2. Если входные сигналы несимметричны, то длительность первого и второго тактов интегрирования равны периоду измерения входных сигналов, т.е. время преобразования преобразователя в этом случае равно двум периодам входного сигнала.

Поскольку в предлагаемом устройстве время интегрирования и интервал .усреднения задается равным полупериоду или периоду входных сигналов формирователем 8, то преобразователь обеспечивает расишрение частотного диапазона входных.сигналов без ухудшения точности.

Блок 4 памяти необходим для того, чтобы на входе схемы не было провалов напряжения, т.е., чтобы выходное напряжение было непрерывным аналогом преобразующей мощности. Управление на включение блока 4 памяти поступает с выхода ключа 3, т.е. информация в 4 памяти обновляется каждьй раз по окончании процесса интегрирования выходного напряжения мно- жительно-делительного блока 1 (фиг.2ж

Таким образом, из диаграмм .фиг.-i видно, что время преобразования пред лагаемого преобразователя не превыша ет одного периода изменения входных ,

симметричньпс сигналов. Кроме того, предлагаемый преобразователь обладает расширенным частотным диапазоном входных сигналов вследствие примене,0 ния подстройки времени интегрирования и усреднения под период входных сигналов .

Формула изобретения

Преобразователь активной мощности в напряжение постоянного тока, содержащий формирователь мгновенной мощности, первый и второй входы которо- 0 го соединены с входами преобразователя, а выход подключен к входу первого интегратора, вьпсод которого через первый ключ соединен с входом блока памяти, выход которого является вы- 5 ходом преобразователя, формирователь, отличающийся тем, что, с целью повьшения быстродействия и расширения частотного диапазона, формирователь мгновенной мощности выпол- эп нен в виде множительно-делительного блока, вход делителя которого через введенные последовательно соединенные второй интегратор и второй ключ подключены к выходу источника опорного напряжения, формирователь своим 35 входом соединен с одним из входов формирователя мгновенной мощности, а выходом - с управляющим входом второго ключа, через дифференцирующую цепь - с управляюгр5ми входами второго интегратора и первого ключа, а через схему задержки - с управляющим вхо- , дом первого интегратора.

a б

Ш

I I

U2

Составитель С.Хромов Редактор Н.Яцола Тетсред М.Дидык | Корректор Т.Малец

Заказ 3050

Тираж 549

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Фиг. 2 .

Подписное

| Кизилов В.У,., Максимов В.М., Смилянский И.И | |||

| Измерительные преобразователи активной мощности энергообъектов | |||

| - Харьков: Вища школа, 1983 | |||

| Усредняющее устройство | 1981 |

|

SU1023345A1 |

| Г, 01 R 21/00, 1981. | |||

Авторы

Даты

1990-10-07—Публикация

1988-12-26—Подача