со ел

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1974 |

|

SU554540A1 |

| Множительно-делительное устройство | 1978 |

|

SU1005081A1 |

| Множительно-делительное устройство | 1978 |

|

SU723596A1 |

| Множительно-делительное устройство | 1984 |

|

SU1203543A1 |

| Аналого-цифровое множительное устройство | 1983 |

|

SU1124346A1 |

| Множительно-делительное устройство | 1981 |

|

SU1001116A1 |

| Множительно-делительное устройство | 1986 |

|

SU1361581A1 |

| Множительно-делительное устройство | 1979 |

|

SU1023344A1 |

| Множительно-делительное устройство | 1986 |

|

SU1405077A1 |

| Множительно-делительное устройство | 1980 |

|

SU900294A1 |

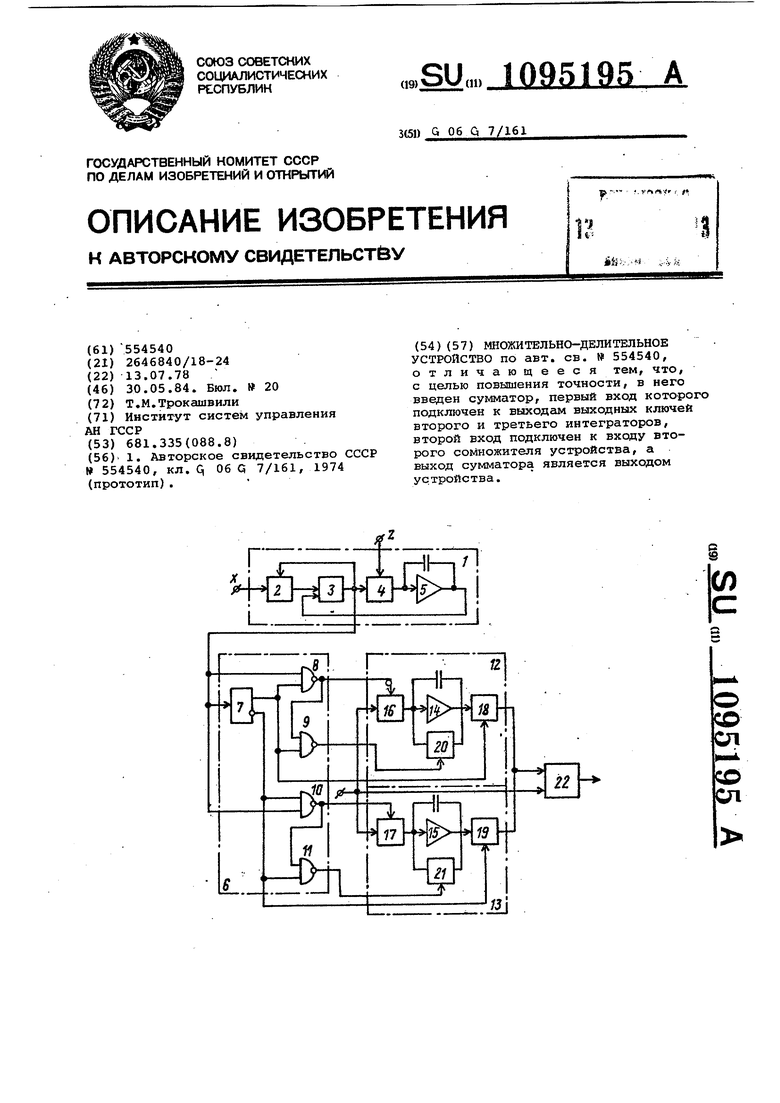

МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО по авт. св. № 554540, отличающееся тем, что, с целью повышения точности, в него введен сумматор, первый вход которого подключен к выходам выходных ключей второго и третьего интеграторов, второй вход подключен к входу второго сомножителя устройства, а выход сумматора является выходом устройства.

ел

Изобретение предназначено для умножения и деления аналоговых напряжений и может быть использовано в аналоговых вычислительных устрой ствах. По основному авт.св. № 554540 известны множительно-делительные устройства, построенные на принципе времяимпульсного преобразования 1J, которые содержат первый компаратор, один вход которого через ключ соединен с входом первого сомножителя.устройства, другой вход первого компаратора соединен с выходом первого интегратора, подключенного входом к выходу второго компаратора, первый вход которого подключен к выходу первого компаратора, подсоединенному к управляющему входу ключа, второй вход ; второго компаратора является входом делителя устройства, второй интегратор а входным выходным и раз рядным-. ключами, третий интегратор с входным, выходным и разрядным ключами, элементы И-НЕ и управляющий триггер, вход которого подключен к выходу первого компаратора, первый выход управляющего три гера соединен с одними.входами первого и второго элементов И-НЕ и с управляющим входом выходного ключа второго интегратора, другие входы первого и второго элементов И-НЕ соединены соответственно с выходом первого компаратора и с выходом первого элемента И-НЕ, выхоцы первого и второго элементов И-НЕ соеди нены соответственно с управляющими входами входного и разрядного ключей второго интегратрра, второй выход управляющего триггера соединен с одними входами третьего и четвертого элементов И-НЕ и с управляющим входом выходного ключа третьего интегратора, другие входы третьего и четвертого элементов И-НЕ соединены соответственно с выходом первого компаратора и с выходом третьего элемента И-НЕ, выходы третьего и четвертого элементов И-НЕ соединены соответственно с управляющими входами входного и разрядного ключе третьего интегратора, информационны входы входных ключей второго и трет его интеграторов объединены и подключены к входу второго сомножителя устройства, выходы выходных ключей второго и третьего интеграторов объ единены и подключены к выходу устро ства. в указанном МДУ (множительно-дел тельном устройстве) точность выполнения операции зависит от времени запаздывания переключающих устройст преобразователя АВИ , блока упра ления ll. и схемы умножения tj С учетом суммарного запаздывания Ъ t, интегратор схемы умножения интегоирует входной сигнал у не в течение времени t 2 где X и Z - входные сигналы преобразователя АВИ, а в течение времени в результате на выходе устройства X л получаем напряжение -гг-У + V, отличающееся от истинного на величину 1у. Цель изобретения - повышение точности работы устройства. Указанная цель достигается тем, что в известное устройство введен первый сумматор, первый вход которого подключен к выходам выходных ключей второго и третьего интеграторов, второй вход подключен к входу второго сомножителя устройства, а выход сумматора является выходом устройства. На чертеже приведена структурная схема множительно-делительного уст ; ройства. Множительно-делительное устройство содержит преобразователь аналог-временной интервал (АВИ) 1, имеющий ключ 2, первый компаратор 3, второй компаратор 4 и первый интегратор 5, блок управления б, выполненный на упраалямцем триггере 7 и логических элементов И-НЕ 8, 9,10 и 11, первый блок умножения 12, второй блок умножения 13, выполненные на интеграторах 14 и 15 соответственно с входныт ми 16 и 17, выходными 18 и 19 и разрядными 20 и 21 ключами и выходкой сушлаторгЗЗ, Множительно-делительное устройство работает следующим образом. При поступлении аналоговых напряжений X и Z на ключ 2 и компаратор 4 на компараторе 3 происходит сравнение напряжений X с напряжением Z t интегратора 5. В момент равенства этих напряжений компараторы 3 и 4 перебрасываются в состояние О, запирается ключ 2 и интегратор 5 начинает компенсировать напряже ние Z t. Когда на выходе интегратора 5 напряжение становится больше О, колшараторы 3 и 4 перебрасываются в состояние , отпирается ключ 2 и процесс циклически повторяется, при этом на выходах компаратора 3 формируются прямоугольные импульсы с равной. скважностью, период которых равенX Z Операция умножения-деления происходит на блоках умножения 12 и 13, интеграторы 14 и 15 которых за время длительности положительных импульсов поочередно формируют напряжение пропорциональное величине. Очередность работы интеграторов 14 и 15 определяется начальным состоянием триггера 7, который перебрасывается отрицательным фронтом каждого импульса. Например, когда триггер переходи, в состояние отпирается ключ 20, управляемый элементом И-НЕ 9, и происходит разряд интегратора 14. В момент запирания ключа 20 отпирается ключ 16, связанный с элементом И-НЕ 8, ч интегратор 14 за время Т/2(Х/2) Z интегрирует напряжение у. В последующие отрицательный и положительный полупериоды ключ 18, управляелвлй триггером 7, открыт и на вход сумматора поступает напряжение, пропорциональное (X/Z).- у. В послед ющий отрицательный полупериод ключ 20 OTKjajT, интегратор 14 разряжается и блок умножения 12 подготовлен для формирования нового значения (X/Z) у. Последовательность операций, выполняемых блоком умножения 13, аналогична, но сдвинута на период Т. Запаздывание выполнения множительно-делительной операции компенсируется следующим образом. Напряжение с интегратора блока умножения 12, равное Ц , складывается на сумматоре с напряжением, равным в дан-i у, вследствие чего ном случае и В, -2 у откуда Использование предлагаемого устройства позволит выполнять операции умножения-деления с высокой точностью при сниженных Чебованиях к переключающим элементам.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Множительно-делительное устройство | 1974 |

|

SU554540A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-05-30—Публикация

1978-07-13—Подача