сд

со

со

4

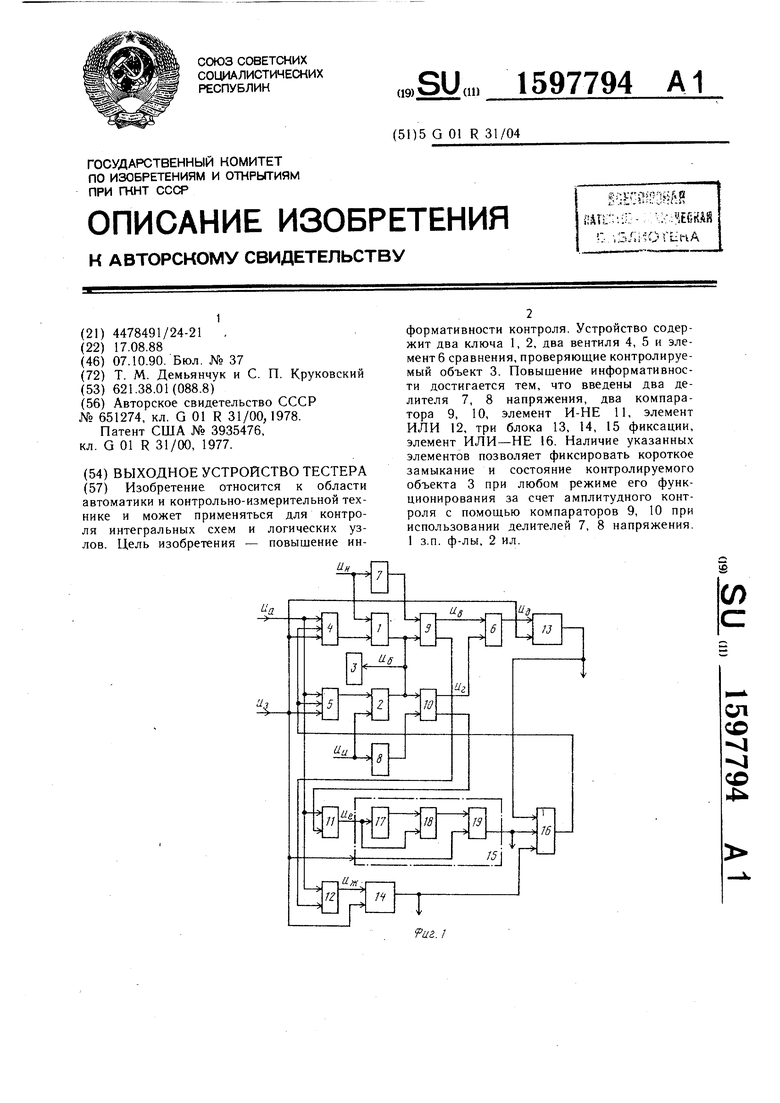

Изобретение относится к автоматике и контрольно-измерительной технике и может применяться для контроля интегральных схем и логических узлов.

Цель изобретения - повышение информативности контроля при использовании устройства.

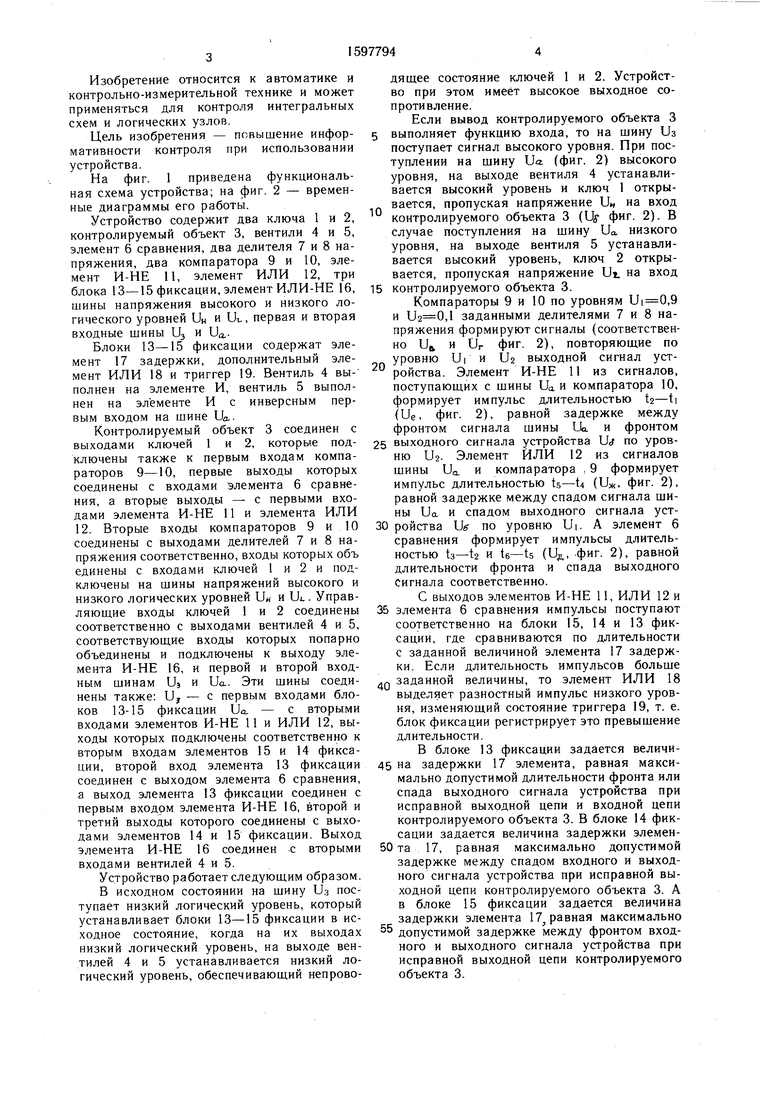

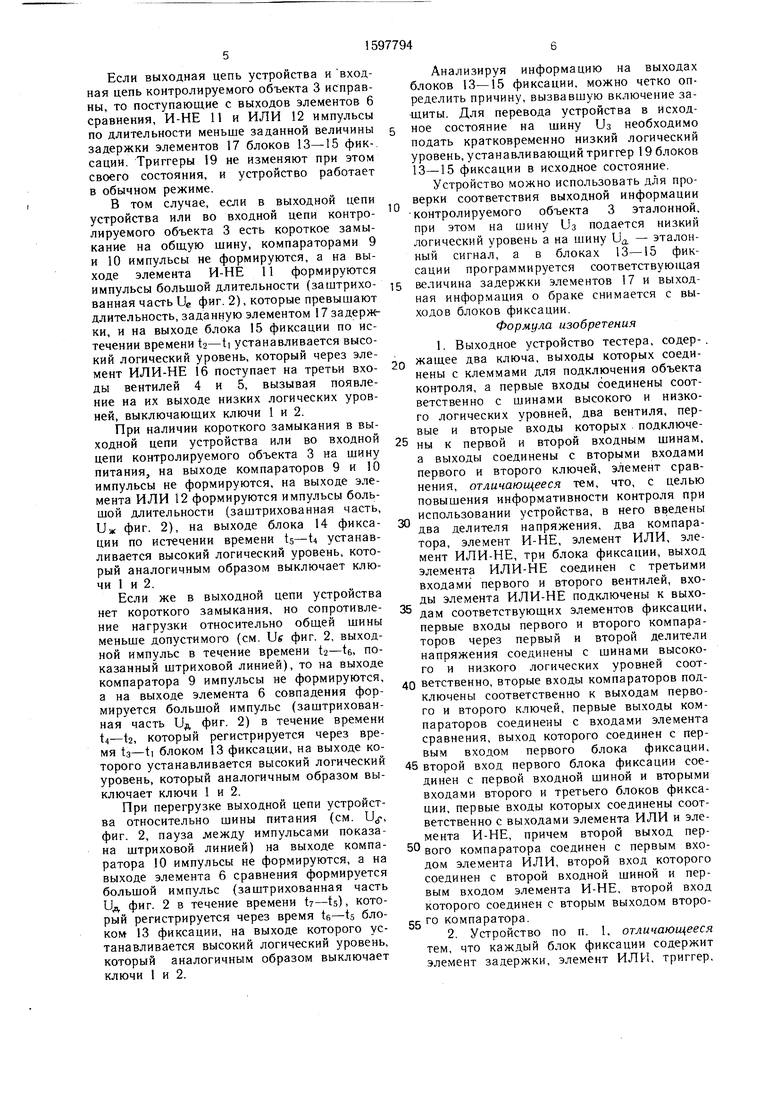

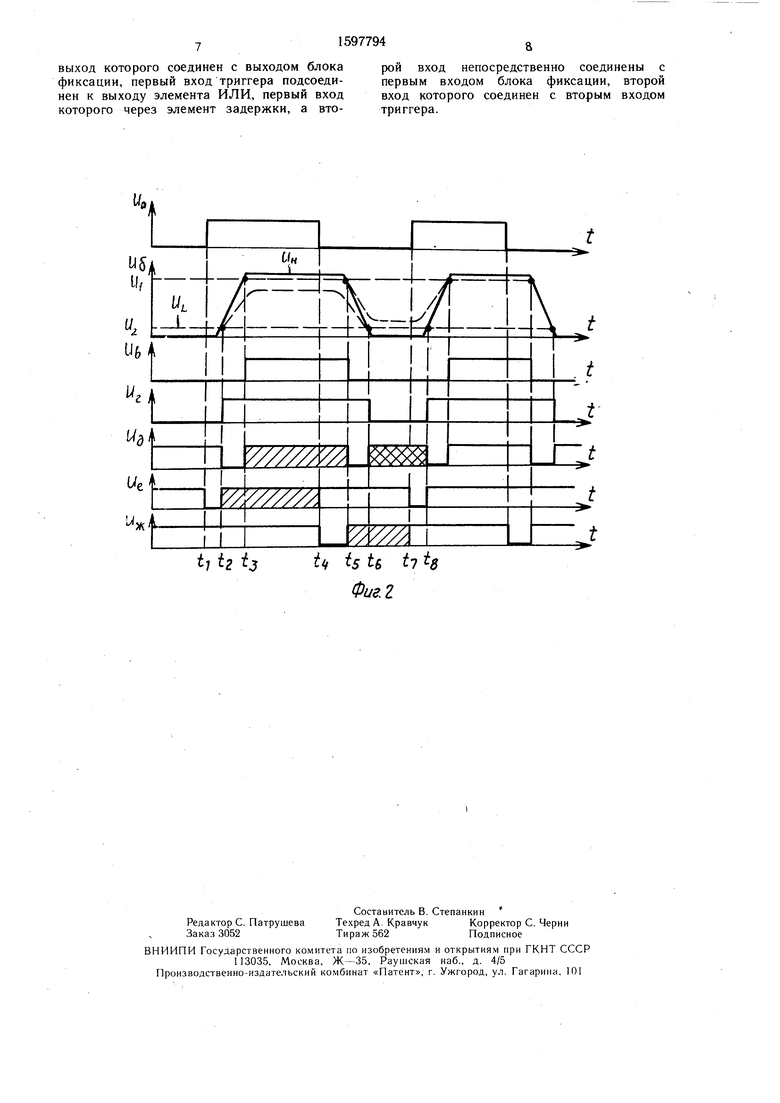

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - временные диаграммы его работы.

Устройство содержит два ключа 1 и 2, контролируемый объект 3, вентили 4 и 5, элемент 6 сравнения, два делителя 7 и 8 напряжения, два компаратора 9 и 10, элемент И-НЕ 11, элемент ИЛИ 12, три блока 13-15 фиксации, элемент ИЛИ-НЕ 16, шины напряжения высокого и низкого логического уровней UH и Ut., первая и вторая входные шины Uj и Uo.Блоки 13-15 фиксации содержат элемент 17 задержки, дополнительный элемент ИЛИ 18 и триггер 19. Вентиль 4 вы- полней на элементе И, вентиль 5 выполнен на элементе И с инверсным первым входом на шине Ua.

Контролируемый объект 3 соединен с выходами ключей 1 и 2, которые подключены также к первым входам компараторов 9-10, первые выходы которых соединены с входами элемента 6 сравнения, а вторые выходы - с первыми входами элемента И-НЕ 11 и элемента ИЛИ 12. Вторые входы компараторов 9 и 10 соединены с выходами делителей 7 и 8 напряжения соответственно, входы которых объ единены с входами ключей 1 и 2 и подключены на шины напряжений высокого и низкого логических уровней UH и UL. Управляющие входы ключей 1 и 2 соединены соответственно с выходами вентилей 4 и 5, соответствующие входы которых попарно объединены и подключены к выходу элемента И-НЕ 16, и первой и второй входным шинам Uj и Ua. Эти шины соединены также: U, - с первым входами блоков 13-15 фиксации Uo, - с вторыми входами элементов И-НЕ 11 и ИЛИ 12, выходы которых подключены соответственно к вторым входам элементов 15 и 14 фиксации, второй вход элемента 13 фиксации соединен с выходом элемента 6 сравнения, а выход элемента 13 фиксации соединен с первым входом элемента И-НЕ 16, второй и третий выходы которого соединены с выходами элементов 14 и 15 фиксации. Выход элемента И-НЕ 16 соединен с вторыми входами вентилей 4 и 5.

Устройство работает следующим образом. В исходном состоянии на шину Us поступает низкий логический уровень, который устанавливает блоки 13-15 фиксации в исходное состояние, когда на их выходах низкий логический уровень, на выходе вентилей 4 и 5 устанавливается низкий логический уровень, обеспечивающий непрово0

дящее состояние ключей 1 и 2. Устройство при этом имеет высокое выходное сопротивление.

Если вывод контролируемого объекта 3 выполняет функцию входа, то на шину Us поступает сигнал высокого уровня. При поступлении на шину Ua (фиг. 2) высокого уровня, на выходе вентиля 4 устанавливается высокий уровень и ключ 1 открывается, пропуская напряжение UH на вход контролируемого объекта 3 (Uy фиг. 2). В случае поступления на шину Ua низкого уровня, на выходе вентиля 5 устанавливается высокий уровень, ключ 2 открывается, пропуская напряжение Ut на вход контролируемого объекта 3.

Компараторы 9 и 10 по уровням ,9 и ,l заданными делителями 7 и 8 напряжения формируют сигналы (соответственно Ufc и Ur фиг. 2), повторяющие по уровню Ui и и выходной сигнал устройства. Элемент И-НЕ 1 из сигналов, поступающих с щины Ua и компаратора 10, формирует импульс длительностью ta-ti (Ue, фиг. 2), равной задержке между фронтом сигнала шины Ua и фронтом 5 выходного сигнала устройства Ш по уровню U2. Элемент ИЛИ 12 из сигналов щины UQ. и компаратора , 9 формирует импульс длительностью ts-14 (U, фиг. 2), равной задержке между спадом сигнала шины Ua и спадом выходного сигнала уст- 0 ройства Ug по уровню Ui. А элемент 6 сравнения формирует импульсы длительностью ts-12 и te-ts (U, фиг. 2), равной длительности фронта и спада выходного сигнала соответственно.

С выходов элементов И-НЕ 11, ИЛИ 12 и 35 элемента 6 сравнения импульсы поступают соответственно на блоки 15, 14 и 13 фиксации, где сравниваются по длительности с заданной величиной элемента 17 задержки. Если длительность импульсов больше д заданной величины, то элемент ИЛИ 18 выделяет разностный импульс низкого уровня, изменяющий состояние триггера 19, т. е. блок фиксации регистрирует это превышение длительности.

В блоке 13 фиксации задается величи- 45 на задержки 17 элемента, равная максимально допустимой длительности фронта или спада выходного сигнала устройства при исправной выходной цепи и входной цепи контролируемого объекта 3. В блоке 14 фиксации задается величина задержки элемен- 50 та 17, равная максимально допустимой задержке между спадом входного и выходного сигнала устройства при исправной выходной цепи контролируемого объекта 3. А в блоке 15 фиксации задается величина задержки элемента 17., равная максимально 5 допустимой задержке между фронтом входного и выходного сигнала устройства при исправной выходной цепи контролируемого объекта 3.

Если выходная цепь устройства и входная цепь контролируемого объекта 3 иСправ- ны то поступающие с выходов элементов 6 сравнения, И-НЕ 11 и ИЛИ 12 импульсы по длительности меньше заданной величины задержки элементов 17 блоков 13-15 фик-. сации. Триггеры 19 не изменяют при этом своего состояния, и устройство работает в обычном режиме.

В том случае, если в выходной цепи устройства или во входной цепи контролируемого объекта 3 есть короткое замыкание на общую щину, компараторами 9 и 10 импульсы не формируются, а на выходе элемента И-НЕ 11 формируются импульсы больщой длительности (заштрихованная часть Uc фиг. 2), которые превышают длительность, заданную элементом 17 задержки, и на выходе блока 15 фиксации по истечении времени ts-ti устанавливается высокий логический уровень, который через элемент ИЛ И-НЕ 16 поступает на третьи входы вентилей 4 и 5, вызывая появление на их выходе низких логических уровней, выключающих ключи 1 и 2.

При наличии короткого замыкания в выходной цепи устройства или во входной цепи контролируемого объекта 3 на шину питания, на выходе компараторов 9 и 10 импульсы не формируются, на выходе элемента ИЛИ 12 формируются импульсы большой длительности (заштрихованная часть, и ж фиг. 2), на выходе блока 14 фиксации по истечении времени ts-14 устанавливается высокий логический уровень, который аналогичным образом выключает ключи 1 и 2.

Если же в выходной цепи устройства нет короткого замыкания, но сопротивление нагрузки относительно общей шины меньще допустимого (см. Us фиг. 2, выходной импульс в течение времени 12-te, показанный штриховой линией), то на выходе компаратора 9 импульсы не формируются, а на выходе элемента 6 совпадения формируется большой импульс (заштрихованная часть Uft фиг. 2) в течение времени , который регистрируется через время 1з-ti блоком 13 фиксации, на выходе которого устанавливается высокий логический уровень, который аналогичным образом выключает ключи 1 и 2.

При перегрузке выходной цепи устройства относительно шины питания (см. U фиг. 2, пауза между импульсами показана штриховой линией) на выходе компаратора 10 импульсы не формируются, а на выходе элемента 6 сравнения формируется большой импульс (заштрихованная часть Ufl. фиг. 2 в течение времени ), который регистрируется через время U-is блоком 13 фиксации, на выходе которого устанавливается высокий логический уровень который аналогичным образом выключает ключи 1 и 2.

Анализируя информацию на выходах блоков 13-15 фиксации, можно четко определить причину, вызвавшую включение защиты. Для перевода устройства в исход- ное состояние на шину Us необходимо подать кратковременно низкий логический уровень, устанавливающий триггер 19 блоков 13-15 фиксации в исходное состояние.

Устройство можно использовать для проверки соответствия выходной информации контролируемого объекта 3 эталонной, при этом на шину Уз подается низкий логический уровень а на шину и - эталонный сигнал, а в блоках 13-15 фиксации программируется соответствующая 5 величина задержки элементов 17 и выходная информация о браке снимается с выходов блоков фиксации.

Формула изобретения 1. Выходное устройство тестера, содер-, г, жащее два ключа, выходы которых соеди- нены с клеммами для подключения объекта контроля, а первые входы соединены соответственно с шинами высокого и низкого логических уровней, два вентиля, первые и вторые входы которых подключе- 25 ны к первой и второй входным щинам, а выходы соединены с вторыми входами первого и второго ключей, элемент сравнения, отличающееся тем, что, с целью повышения информативности контроля при .,,, ,,/, п нргп введены

30

использовании устройства, в него введены два делителя напряжения, два компаратора, элемент И-НЕ, элемент ИЛИ, элемент ИЛИ-НЕ, три блока фиксации, выход элемента ИЛИ-НЕ соединен с третьими входами первого и второго вентилей, входы элемента ИЛИ-НЕ подключены к выхо- 35 дам соответствующих элементов фиксации, первые входы первого и второго компараторов через первый и второй делители напряжения соединены с шинами высокого и низкого логических уровней соот- 40 ветственно, вторые входы компараторов подключены соответственно к выходам первого и второго ключей, первые выходы компараторов соединены с входами элемента сравнения, выход которого соединен с первым входом первого блока фиксации, 45 второй вход первого блока фиксации соединен с первой входной шиной и вторыми входами второго и третьего блоков фиксации, первые входы которых соединены соответственно с выходами элемента ИЛИ и элемента И-НЕ, причем второй выход пер- 50вого компаратора соединен с первым входом элемента ИЛИ, второй вход которого соединен с второй входной шиной и первым входом элемента И-НЕ, второй вход которого соединен с вторым выходом второ- сс го компаратора.

2. Устройство по п. 1, отличающееся тем, что каждый блок фиксации содержит элемент задержки, элемент ИЛИ, триггер.

-71597794g

выход которого соединен с выходом блокарой вход непосредственно соединены с

фиксации, первый вход триггера подсоеди-первым входом блока фиксации, второй

йен к выходу элемента ИЛИ, первый входвход которого соединен с вторым входом

которого через элемент задержки, а вто-триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических и временных параметров сигналов | 1990 |

|

SU1777235A1 |

| Устройство для контроля работоспособности модуля усилительного тракта радиоэлектронной аппаратуры | 1989 |

|

SU1817047A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1481887A1 |

| ФОРМИРОВАТЕЛЬ КОМАНД УПРАВЛЕНИЯ | 2003 |

|

RU2244960C2 |

| Устройство для регулирования температуры | 1986 |

|

SU1403025A1 |

| Фильтр-реле тока | 1991 |

|

SU1814131A1 |

| Аналого-цифровой частотомер | 1988 |

|

SU1712894A1 |

| Устройство для фиксации временного положения импульса | 1986 |

|

SU1437976A1 |

| Устройство для автоматического контроля сопротивления изоляции электрических цепей | 1989 |

|

SU1647472A1 |

| Демодулятор сигналов с фазово-импульсной модуляцией | 1984 |

|

SU1267605A1 |

Изобретение относится к области автоматики и контрольно-измерительной технике и может применяться для контроля интегральных схем и логических узлов. Цель изобретения - повышение информативности контроля. Устройство содержит два ключа 12, два вентиля 4, 5 и элемент 6 сравнения, проверяющее контролируемый объект 3. Повышение информативности достигается тем, что введены два делителя 7,8 напряжения, два компаратора 9,10, элемент И-НЕ 11, элемент ИЛИ 12, три блока, фиксации 13, 14, 15, элемент ИЛИ-НЕ 16. Наличие указанных элементов позволяет фиксировать короткое замыкание и состояние контролируемого объекта 3 при любом режиме его функционирования за счет амплитудного контроля с помощью компараторов 9, 10 при использовании делителей 7, 8 напряжения. 1 з.п. ф-лы, 2 ил.

i; 2ifjt i sU

Фиг.2

| Выходной узел тестера для контроля логических устройств | 1977 |

|

SU651274A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3935476, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1990-10-07—Публикация

1988-08-17—Подача