{

Изобретение относится к области импульсной техники.

IteBGCTiio логическое устройство для ввода и вывода информадии, содержащее буферный каскад, токоогратцгчисаюший резистор и схему сравнения, первый вход которой соединен со входок буферного каскада, а второй вход через токоогра1-и Ч1шающий резистор - с его выход сзм l

Недостатками этого устрюйства ЯВЛЯЮТСЯ низкие точность передачи логических уровней и нагрузочная способность.

Известно устройство, содержащее входной вентиль, вентиль запрета, буферный каскад, ключ уровня логической единиш и КЛЮЧ уровня логического ну

ЛЯ 21;

Нед1х:татком этого устройс-тва является отсутствие защиты ключей от перегрузок.

Известно также, устройство, содержащее входной вентиль, вентиль запрс-

та, )ерный каскад, ключ уровня логического нуля, ключ уровня логической единнщз, в котором входы кяючой соединены с выходами буферного каскада, а выходы подкллочены к выходному кон- такту З .

Его недостатком является отсутствие защиты ключей от нерегрузок при замыкаш выходного контакта на одну из шин источ1шка питания.

Целью изобретения является обеспечение защиты : ключей; от нерегруоок.

Поставленная цепь достигается тем, что в выходной узел тестера для кон гроля логических устройств, содержащий два , выходы которых подключены к выходному контакту, а первые входы соединены соответственно с шИнамн лэ- пгческого нуля и логической единицы, и два вентиля, первый и второй входы первого КЗ ко горых соодинены с входными -(линами, доиолни1х льно введены элемент сравнения и триггер. Входы элемента сравнения соединены с первой

входной шиной и выхолньил контактом, выход соединен с Q -входом триггера, С вход которого подключен к шине синхронизации, инверсный S -входк второй входной шине. Первый вход второго вентиля соединен с второй входной шиной, второй вход через инверторс первой входной шиной. Третьи входы вентилей соединены с выходом триггера, а выходы - с Вторыми входами соответствующих ключей.

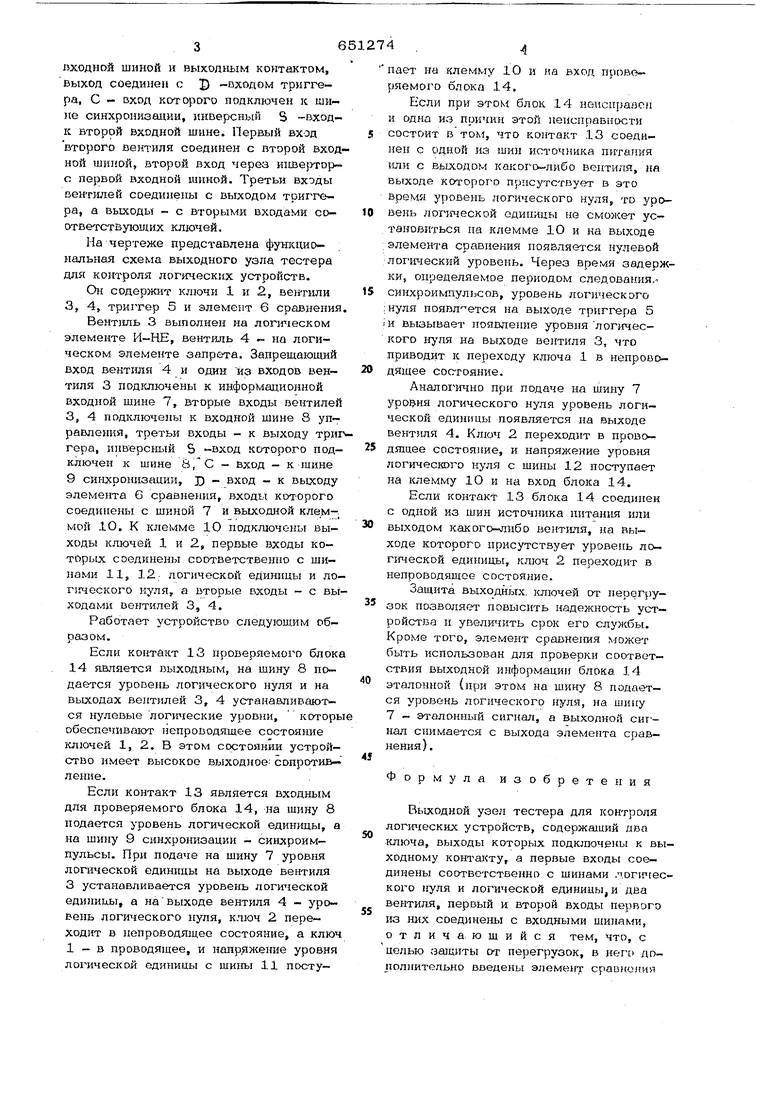

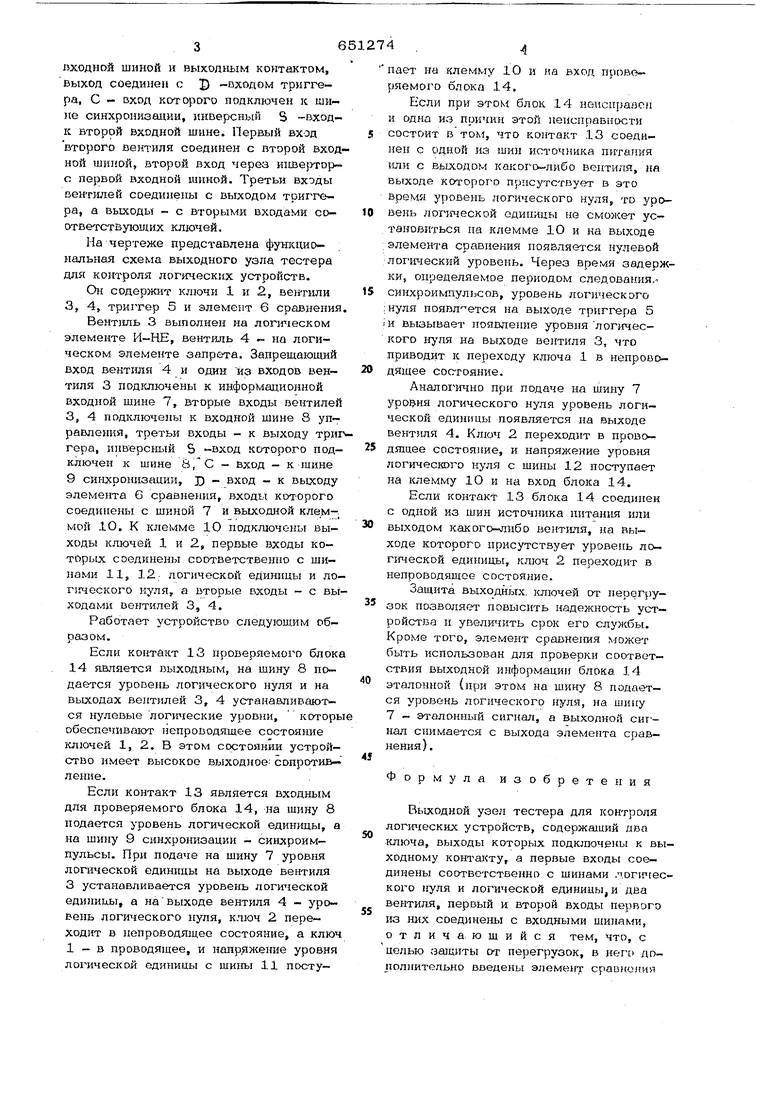

На чертеже представлена фушс1шо- ; нальная схема выходного узла тостера для контроля логических устройств.

Oil содержит ключи 1 и 2, вентуши 3, 4, триггер 5 и элемент 6 сравнения

Вентиль 3 выполнен на логическом элементе И-НЕ, вент1шь 4 - на логическом элементе занрета. Занрещающий вход вентиля 4 и один из входов вентиля 3 под1шючены к информационной входной шине 7, вторые входы вентилей 3, 4 подключены к входной шине 3 управлеш я, третьи входы - к выходу триггера, инверсный S -вход которого подключен к шине 8,С - вход - к-шине 9 синхронизации, D - вход - к выходу элемента 6 сравнения, входы кот-орого соединены с шиной 7 и выходной клем- мой Ю. К клемме 10 нодключоны выходы ключей 1 и 2, первые входы которых соединены соответственно с шинами 11, 12; логической единицы и лопгческого нуля, а вторые входы - с выходами вентилей 3, 4.

Работает устройство следующим образом.

Если контакт 13 проверяемого блока 14 является выходным, на шину 8 нодается уровень логического нуля и на выходах вентилей 3, 4 устанавливают ся нулевые логические уровни, которы обеснечивают непроводящее состояние ключей 1, 2. В этом состоянии устройство имеет высокое выходное сопротив- ление.

Если контакт 13 является входным для нроверяемого блока 14, на шину 8 подается уровень логической единицы, а на шину 9 синхронизации - синхроимпульсы. При подаче на шину 7 уровня логической единицы на выходе вентиля 3 устанавливается уровень логической единицы, а на выходе вентиля 4 - уровень логического нуля, ключ 2 нереходит в непроводящее состояние, а ключ 1 - в проводящее, и напряжение уровня логической единицы с шины 11 посту-

нает на клемму Ю и ка вход проверяемого блока 14.

Если при этом блок 14 неисправен и одна из причин этой неиснравности состоит в том, что контакт 13 соеди ген с одной из шин источника питания или с выходом какого-либо вентиги, на Выходе которого присутствует в это Время уровень логического нуля, то уровень лопгческой единицы не сможет установиться на клемме 10 и на выходе . элемента сравнения появляется нулевой лопгческий уровень. Через время задержки, определяемое периодом следования.синхроимпульсов, уровень логического .; нуля появляется на выходе триггера 5 iH вызывает появление уровнялогического на выходе вентиля 3, что приводит к переходу ключа 1 в непроводящее состояние.

Аналогично при подаче на шину 7 ypoijHH логического нуля уровень логической единицы появляется на выходе вентиля 4. Ключ 2 переходит в проводящее состояние, и напряжение уровня логического нуля с шины 12 поступает на клемму 10 и на вход блока 14.

Если контакт 13 блока 14 соедииен с одной из шин источника питания или выходом какого-либо вентиля, на выходе которого присутствует уровень логической единицы, ключ 2 переходит в непроводящее состояние.

Защита выходных, ключей от нерегрузок позволяет повысить надежность устройства и увеличить срок его службы. Кроме того, элемент сравнения может быть использован для проверки соответствия выходной информации блока 14 эталонной (нри этом на шину 8 подается уровень логического нуля, на шину 7 - эталонный сигнал, а выходной сигнап снимается с выхода элемента сравнения).

Формула изобретен и

я

Выходной узел тестера для контроля логихеских устройств, содержащий два ключа, выходы которых подюпочекы к выходному контакту, а первые входы соединены соответственно с шинами лопгческого нуля и логической единицы, и два вентиля, первый и второй входы первого из них соединены с входными щинами, отличающийся тем, что, с целью защиты от перегрузок, в него допол)штельно введены элемент сравиолия

и триггер; причем входы элемента сравнения соедине11Ы с первой входной шкной и выходным контактом, выход соединен с D -входом триггера, С вход которого подключен к шине синхронизашп, инверсный 5 -вход - к второй входной шине; первый вход второго вентиля соединен с второй входной шиной, второй вход через инвертор с первой входной шиной; третьи входы вентилей соединены с выходом триггера, а выходы с вторыми входами соответствуюлшх ключей.

Источники информшхии, принятые во внимание ори экспертизе

1.Патент США № 3935476, кл. ЗО7-213, 27.01.76.

2.Патент США lo 36О2733, кл, 307-2О9, 31.08.71.

3.Патент США .N9 3792292, кл, 307-2О9, 16.О6.72.

I1

J

/4

| название | год | авторы | номер документа |

|---|---|---|---|

| Выходной узел тестера для контроля логических блоков | 1980 |

|

SU940090A1 |

| Выходной узел тестера для контроля логических схем | 1982 |

|

SU1018064A1 |

| Выходной узел тестера для контроля цифровых блоков | 1987 |

|

SU1788516A1 |

| БАЗОВОЕ МАТРИЧНОЕ УСТРОЙСТВО | 1989 |

|

SU1690513A1 |

| Фазовый детектор | 1980 |

|

SU949797A1 |

| Устройство для управления трехфазным инвертором | 1984 |

|

SU1354365A1 |

| Способ поиска дефектов в цифровых блоках и устройство для его осуществления | 1985 |

|

SU1260884A1 |

| Цифровые электронные часы | 1978 |

|

SU779967A1 |

| УСТРОЙСТВО ТОКОВОЙ ЗАЩИТЫ ЭЛЕКТРОУСТАНОВКИ | 1993 |

|

RU2114496C1 |

| Выпрямитель с защитой от токов короткого замыкания | 1983 |

|

SU1156213A1 |

Авторы

Даты

1979-03-05—Публикация

1977-05-26—Подача