ел

со

00

4;: ГС

Изобретение относится к автомати- :ке и вычислительной технике.

Цель изобретения - повышение быстродействия асинхронного распределите- ля.

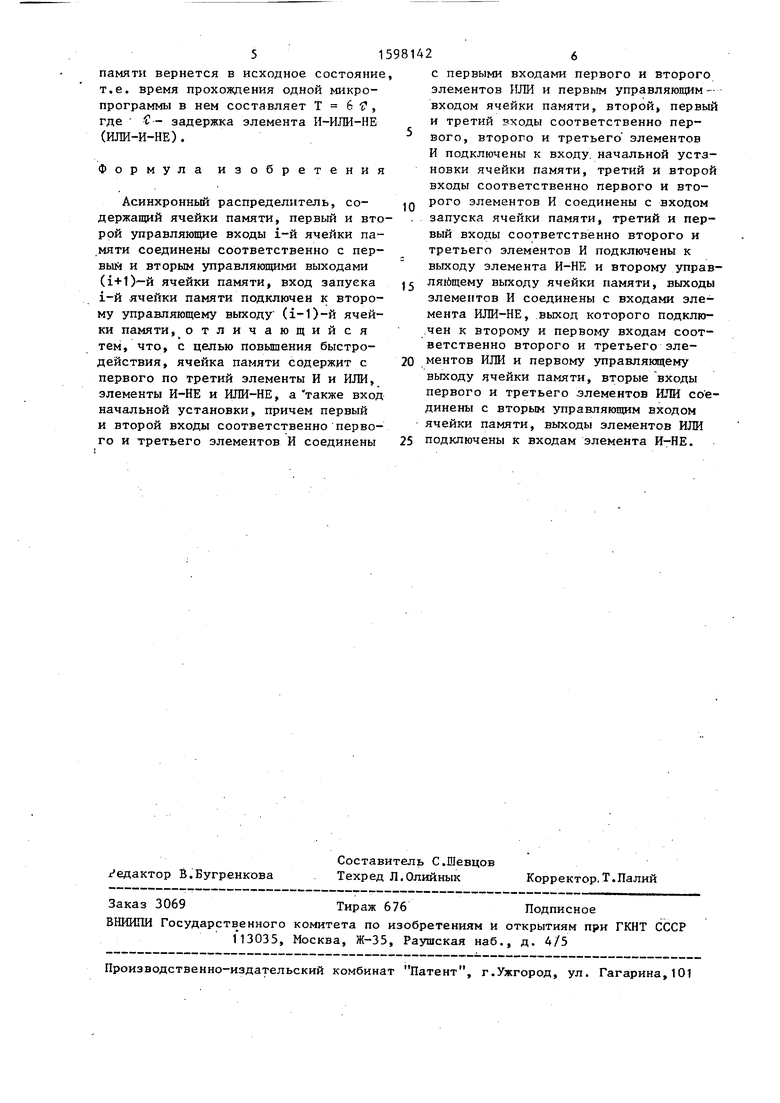

На чертеже представлена функциональная схема устройства.

Асинхронньш распределитель состоит из ячеек 1 памяти, каждая из кото- рых содержит с первого по третий элементы И -2-4 и элементы ИЛН 5-7, элемент ИЛИ-НЕ 8, элемент И-НЕ 9, первый 10 и второй 11 управляющие входы первый 12 и второй 13 управляющие выходы, вход 14 запуска и вход 15 начальной установки.

Функционирование асинхронного распределителя осуществляется следующим образом.

В исходном состоянии ячейки 1 памяти в R-триггер, состоящий из элементов 2-9, записан логический О, т.е. на выходе элемента ИЛИ-НЕ 8 имеется единичный логический уро- вень, на выходе И-НЕ 9 - нулевой. Для этого на вход 10 начальной уста- подается нулевой логический сигнал, что приводит к появлению единичных уровней на выходах всех элементов ИЛИ-НЕ 8, которые в свою очередь устанавливают на выходах элементов И-НЕ 9 единичные логические уровни. После окончания начальной установки на входе 10 поддерживается единичный логический уровень.

В рабочем режиме в асинхронном распределителе установка (1-1)-й ;ячейки 1 памяти производится подачей единичного логического уровня на ее вход 14 запуска. При этом в R-триггер запишется 1,.т.е. на выходе элемента ИЛИ-НЕ 8 появится нулевой логический зфовень, а на выходе элемента И-НЕ 9 - единичный. Это состояние триггера не может измениться пока на входе 14 запуска (1-1)-й ячейки памяти не появится снова нулевой логический уровень. Установка R-триг гера (1-1)-й ячейки памяти в -1 вы- зывает появление единичного логичест когЬ уровня на втором управляющем выходе 13, который поступает на вход 14 запуска i-й ячейки памяти. В результате этого в R-триггер i-й ячей- ки памяти записывается 1, т.е. на выходе элемента ИЛИ-НЕ 8 появляется нулевой логический уровень, на выход элемента И-ИЕ 9 - единичный логичест

s

0

о

о 5 п е

5

кий уровень. Установка R-триггера i-й ячейки памяти вызывает появление нулевого логического уровня на первом управляющем выходе 12 i-й ячейки памяти, которьй поступает на первый управляющий вход 10 (i-1)-й ячейки памяти. Если к этому моменту на входе 14 запуска (i-)-й ячейки памяти - нулевой логический уровень, то появление нулевого логического уровня на первом управляющем входе 10 и единичного логического уровня на втором управляющем входе 11 (i-1)-й ячейки памяти приводит к возврату R-триггера , (i-1)-и ячейки памяти в нулевое состояние, т.е. на выходе элемента ИЛИ-НЕ 8 появится единичный логический уровень, на выходе элемента И-НЕ 9 - нулевой. Одновременно с этим произойдет установка (i+1)-й ячейки 1 памяти, процесс срабатывания которой аналогичен рассмотренному.

До тех пор пока в R-триггере .-й ячейки 1 памяти записана R-триггер (i-i)-и ячейки-1 памяти.jie может быть записана 1. Действительно, при этом на первом 12 и втором 13 управляющих выходах i-й ячейки памяти (на первом 10 и втором 11 управляющих входах (i-1)-и ячейки памяти) установятся соответственно нул евой и единичный логический уровни, которые удерживают R-триггер (i-1)-й ячейки памяти в состоянии О. Появление единичного логическо- го уровня на входе 14 запуска (i-1)-й ячейки памяти при этом не вызывает переключения R-триггера.

Таким образом, повторная установ- ;Ка (i-1)-и ячейки 1 памяти осуществляется лишь после того, как i-я ячейка памяти окажется в исходном состоянии. Следовательно, при повтор- ной инициации работы асинхронного распределителя до того, ка.к завершится предьщущий цикл его работы, юсле- дующая волна установок ячеек памяти не достигнет предыдущей, так как между ними всегда будет находиться по крайней мере одна ячейка памяти в исходном состоянии, что обеспечивает правильное функционирование распределителя в мультипрограммном режиме .

В асинхронном распределителе повторная лнициация может осуществляться после того как его вторая ячейка

памяти вернется в исходное состояние т.е. время прохождения одной микропрограммы в нем составляет Т /1

(-

Ь- J

где I. - задержка элемента И-ИЛИ-НЕ (ИЛИ-И-НЕ).

Формула изобретения

Асинхронный распределитель, содержащий ячейки памяти, первый и второй управляющие входы i-й ячейки памяти соединены соответственно с первый и вторым управляющими выходами (1+1)й ячейки памяти, вход запуска i-й ячейки памяти подключен к второму управляющему выходу (-1)-й ячейки памяти, отличающийся тем, что, с целью повышения быстродействия, ячейка памяти содержит с первого по третий элементы И и ИЛИ, элементы И-НЕ и ИЛИ-НЕ, а также вход начальной установки, причем первый и второй входы соответственно перво0

с первыми входами первого и второго элементов ИЛИ и первым управляющим- входом ячейки памяти, второй, первый и третий входы соответственно первого, второго и третьего элементов И подключены к входу, начальной установки ячейки памяти, третий и второй входы соответственно первого и второго элементов И соединены с входом запуска ячейки памяти, третий и первый входы соответственно второго и третьего элементов И подключены к выходу элемента И-НЕ и второму управ-

5 ляйщему выходу ячейки памяти, выходы элементов И соединены с входами элемента ИЛИ-НЕ, выход которого подклю- .чен к второму и nepBoi-iy входам соответственно второго и третьего эле0 ментов ИЛИ и первому управляющему выходу ячейки памяти, вторые входы первого и третьего элементов ИЖ со е- динены с вторым управляющим входом ячейки памяти, выходы элементов ИЛИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Асинхронный распределитель | 1982 |

|

SU1064461A1 |

| Асинхронный распределитель | 1982 |

|

SU1026304A1 |

| Реверсивный регистр сдвига | 1989 |

|

SU1817135A1 |

| Асинхронный распределитель | 1981 |

|

SU1018245A1 |

| ДИСКРЕТНАЯ МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1997 |

|

RU2110827C1 |

| Кольцевой асинхронный распределитель | 1985 |

|

SU1322452A1 |

| Ячейка асинхронного распределителя | 1981 |

|

SU984060A1 |

| Асинхронный распределитель | 1983 |

|

SU1249714A1 |

| Многоканальное устройство ввода аналоговой информации | 1987 |

|

SU1418726A1 |

| Линейный интерполятор | 1989 |

|

SU1659986A1 |

Изобретение относится к автоматике и вычислительной технике. Цель изобретения - повышение быстродействия асинхронного распределителя. Асинхронный распределитель состоит из ячеек 1 памяти, каждая из которых содержит с первого по третий элементы И 2 - 4 и элементы ИЛИ 5 - 7, элементы ИЛИ - НЕ 8, элемент И - НЕ 9, первый 10 и второй 11 управляющие входы, первый 12 и второй 13 управляющие выходы, вход 14 запуска и выход 15 начальной установки. За счет обеспечения дополнительных возможностей управления состоянием ячейки памяти асинхронного распределителя достигается повышение его быстодействия. Время прохождения одной микропрограммы составляет 6 Τ, где Τ - задержка элемента И - ИЛИ - НЕ (ИЛИ - И - НЕ). 1 ил.

го и третьего элементов И соединены 25 подключены к входам элемента И-НЕ.

Авторы

Даты

1990-10-07—Публикация

1988-05-31—Подача