26% Я 28 23 .1.1 1 1

2S 2728 23

25 27 28 23

28 272323 25 2728 29 Ц- J-LJL1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1987 |

|

SU1552388A2 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1986 |

|

SU1401629A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1352624A1 |

| Устройство для считывания изображений | 1986 |

|

SU1429142A1 |

| Устройство для контроля постоянной памяти | 1987 |

|

SU1411838A2 |

| Ассоциативное оперативное запоминающее устройство | 1988 |

|

SU1667155A1 |

| Устройство для поиска информации в памяти | 1985 |

|

SU1352494A1 |

| Устройство для решения системы линейных уравнений | 1987 |

|

SU1411776A1 |

| Вычислительная система "Антикон" для предотвращения столкновения судов | 1983 |

|

SU1136178A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании устройств хранения и сдвига информации. Целью изобретения является расширение области применения регистра за счет обеспечения самосинхронного режима его работы. Это позволяет использовать регистр как в устройствах с внешней синхронизацией, так и в самосинхронных устройствах. Входные и выходные сигналы регистра являются парофазными. Регистр содержит ячейки памяти 4, первый и второй блоки сопряжения. Для достижения поставленной цели в регистр введены блок индикаторов, распределитель управляющих сигналов и блок местного управления, а в каждую ячейку памяти 4 - четыре дополнительных элементов И-НЕ 5-8. 6 ил.

ттттт

5(555357

54 5SS3S7

$$59 SS 57 Фиг. 2.

ттттг

73

11

Ю 56,12гттгг

&SSS9f У, 55 5) 57

оо

GJ СЛ

Изобретение относится к вычислительной технике и цифровой автоматике и может быть использовано при построении различных функциональных узлов процессоров и других средств вычислительной техники, а также в устройствах хранения и обработки дискретной информации,

Цель изобретения - расширение области применения реверсивного регистра сдвига за счет обеспечения самосинхронно- го режима его работы.

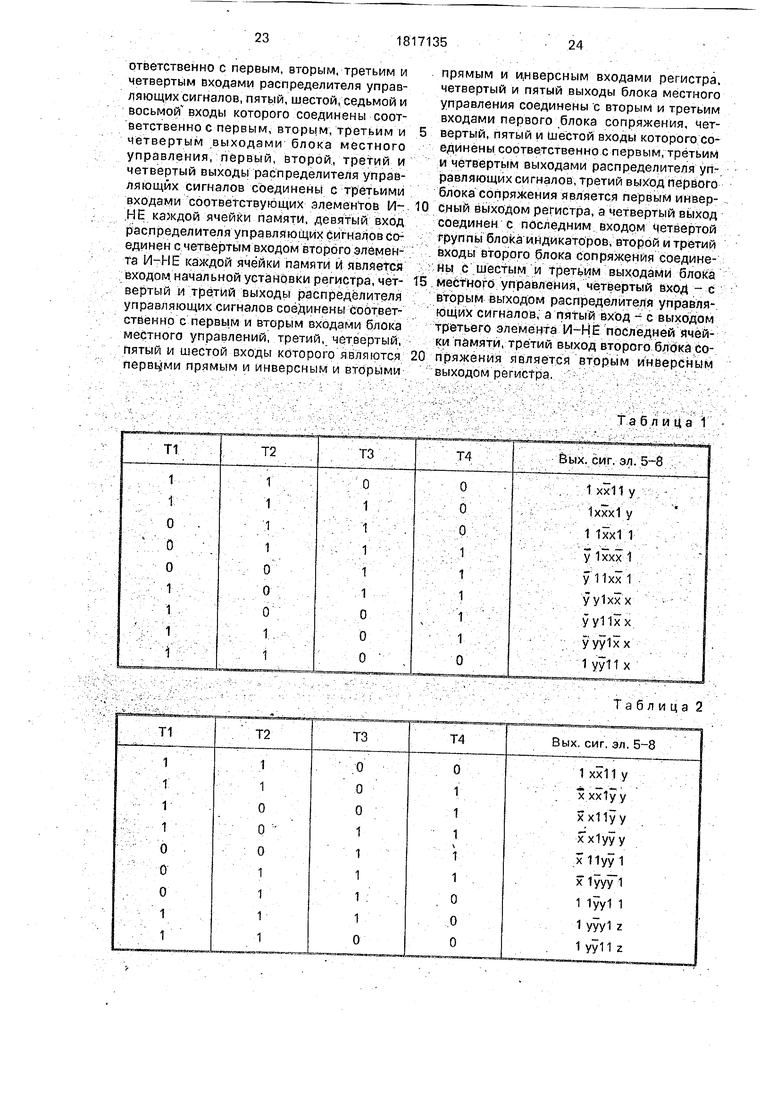

На фиг, 1 приводится структурная схема реверсивного регистра сдвига; на фиг. 2 - схема ячеек памяти регистра; на фиг. 3 - схема блока индикаторов, вариант выполне- ния; на фиг. 4 - схема распределителя управляющих сигналов, вариант; на фиг. 5 - схема блока местного управления, вариант; на фиг. 6 - схема первого и второго блоков сопряжения совместно с ячейками памяти, вариант.

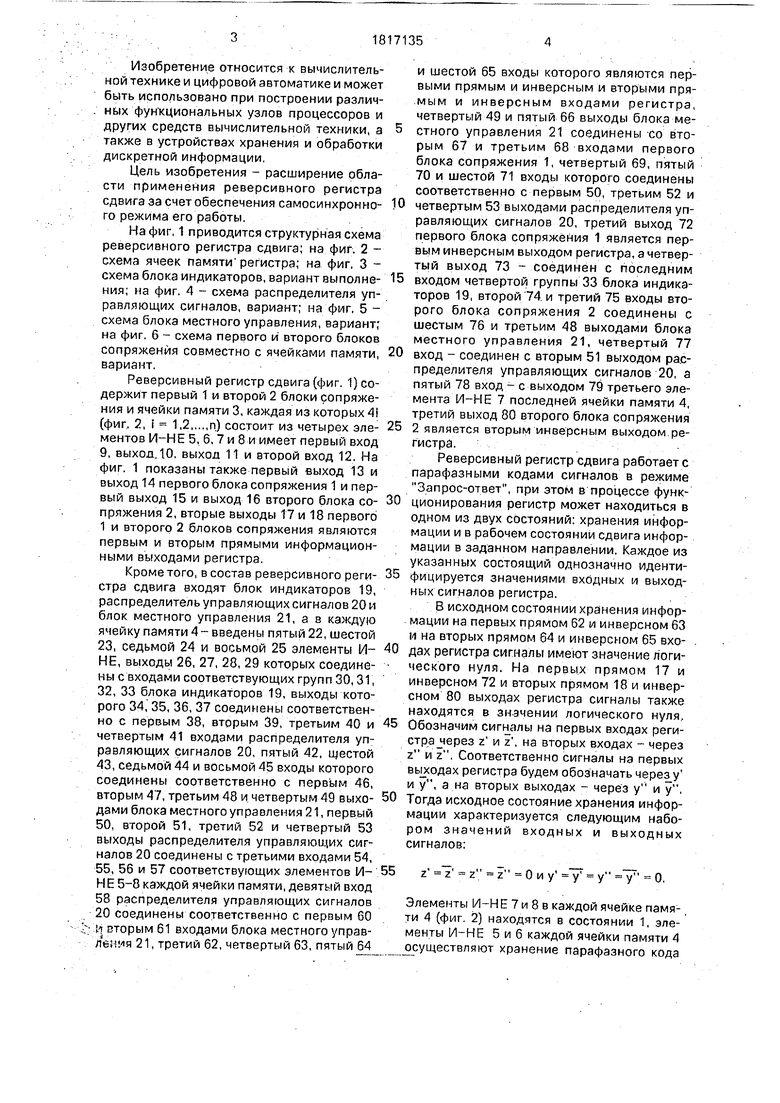

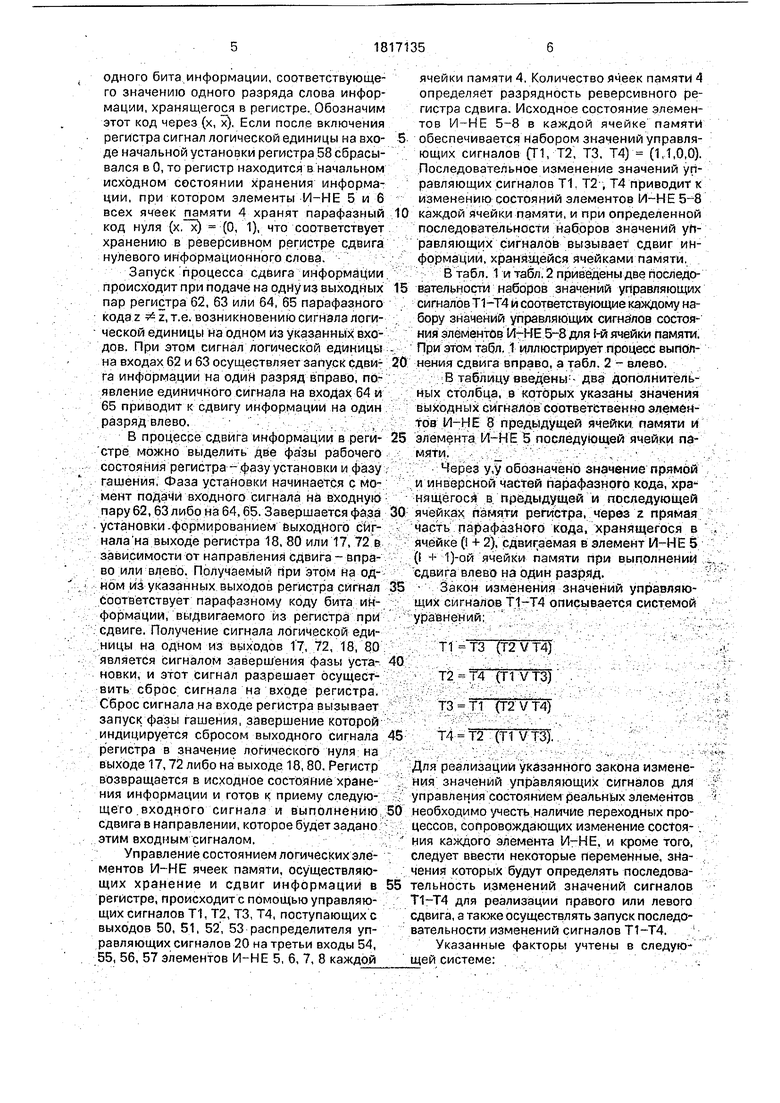

Реверсивный регистр сдвига (фиг. 1) содержит первый 1 и второй 2 блоки сопряжения и ячейки памяти 3, каждая из которых 4| (фиг, 2, i 1,2,,..,п.) состоит из четырех эле- ментов И-НЕ 5, 6,7 и 8 и имеет первый вход 9, выход. 10, выход 11 и второй вход 12. На фиг, 1 показаны также первый выход 13 и выход 14 первого блока сопряжения 1 и первый выход 15 и выход 16 второго блока со- пряжения 2, вторые выходы 17 и 18 первого 1 и второго 2 блоков сопряжения являются первым и вторым прямыми информационными выходами регистра.

Кроме того, в состав реверсивного реги- стра сдвига входят блок индикаторов 19, распределитель управляющих сигналов 20 и блок местного управления 21, а в каждую ячейку памяти 4- введены пятый 22, шестой 23, седьмой 24 и восьмой 25 элементы И- НЕ, выходы 26, 27, 28, 29 которых соедине- ны с входами соответствующих групп 30,31, 32, 33 блока индикаторов 19, выходы которого 34, 35, 36, 37 соединены соответственно с первым 38, вторым 39, третьим 40 и четвертым 41 входами распределителя управляющих сигналов 20, пятый 42, шестой 43, седьмой 44 и восьмой 45 входы которого соединены соответственно с первым 46, вторым 47, третьим 48 и четвертым 49 выхо- дами блока местного управления 21, первый 50, второй 51, третий 52 и четвертый 53 выходы распределителя управляющих сигналов 20 соединены с третьими входами 54, 55, 56 и 57 соответствующих элементов И- Н Е 5-8 каждой ячейки памяти, девятый вход 58 распределителя управляющих сигналов 20 соединены соответственно с первым 60 - I вторым 61 входами блока местного управления 21, третий 62, четвертый 63, пятый 64

и шестой 65 входы которого являются первыми прямым и инверсным и вторыми прямым и инверсным входами регистра, четвертый 49 и пятый 66 выходы блока местного управления 21 соединены со вторым 67 и третьим 68 входами первого блока сопряжения 1, четвертый 69, пятый 70 и шестой 71 входы которого соединены соответственно с первым 50, третьим 52 и четвертым 53 выходами распределителя управляющих сигналов 20, третий выход 72 первого блока сопряжения 1 является первым инверсным выходом регистра, а четвертый выход 73 - соединен с последним входом четвертой группы 33 блока индикаторов 19, второй 74. и третий 75 входы второго блока сопряжения 2 соединены с шестым 76 и третьим 48 выходами блока местного управления 21, четвертый 77 вход - соединен с вторым 51 выходом распределителя управляющих сигналов 20, а пятый 78 вход - с выходом 79 третьего элемента И-НЕ 7 последней ячейки памяти 4, третий выход 80 второго блока сопряжения 2 является вторым инверсным выходом.регистра.

Реверсивный регистр сдвига работает с парафазными кодами сигналов в режиме Запрос-ответ, при этом в процессе функционирования регистр может находиться в одном из двух состояний: хранения информации и в рабочем состоянии сдвига информации в заданном направлении, Каждое из указанных состоящий однозначно идентифицируется значениями входных и выходных сигналов регистра.

В исходном состоянии хранения информации на первых прямом 62 и инверсном 63 м на вторых прямом 64 и инверсном 65 входах регистра сигналы имеют значение логического нуля. На первых прямом 17 и инверсном 72 и вторых прямом 18 и инверсном 80 выходах регистра сигналы также находятся в значении логического нуля. Обозначим сигналы на первых входах регистра через z и г , на вторых входах - через т. иг, Соответственно сигналы на первых выходах регистра будем обозначать через у и у, а на вторых выходах - через у и у, Тогда исходное состояние хранения информации характеризуется следующим набором значений входных и выходных сигналов;

г -г - г

z 0 и у у у у 0.

Элементы И-НЕ 7 и 8 в каждой ячейке памяти 4 (фиг. 2) находятся в состоянии 1. элементы И-НЕ 5 и 6 каждой ячейки памяти 4 осуществляют хранение парафазного кода

одного бита информации, соответствующего значению одного разряда слова информации, хранящегося в регистре.. Обозначим этот код через (х, х). Если после включения регистра сигнал логической единицы на входе начальной установки регистра 58 сбрасывался в 0, то регистр находится в начальном исходном состоянии хранения информации, при котором элементы И-НЕ 5 и 6 всех ячеек памяти 4 хранят парафазный код нуля (х.х) - (0, 1), что соответствует хранению в реверсивном регистре сдвига нулевого информационного слова.

Запуск процесса сдвига информации, происходит при подаче на одну из выходных пар регистра 62, 63 или 64, 65 парафазного кода z z, т.е. возникновений сигнала логической единицы на одном из указанных входов. При этом сигнал логической единицы на входах 62 и 63 осуществляет запуск сдвига информации на один разряд вправо, появление единичного сигнала на входах. 64 и 65 приводит к сдвигу информации на один . разряд влево. . .-.-,. . ; , /

В процессе сдвига информации в регй- стрё можно выделить Две фазы рабочего состояния регистра-фазу установки и фазу; гашения, Фаза установки начинается с мо-: мент подачи входного сигнала на входную: пару 62,63 либо на 64,65. Завершается фаза установки-формированием выходного сигнала на выходе регистра 18, 80 или 17, 72 в зависимости от направления сдвига- вправо или влево. Получаемый при этом на одном из указанных выходов регистра сигнал соответствует парафазному коду бита ий- формации, выдвигаемого из регистра при сдвиге. Получение сигнала логической еди- .ницы на одном из выходов 17, 72, 18, 80-. является сигналом завершения фазы установки, и этот сигнал разрешает осуществить сброс сигнала на входе регистра. Сброс сигнала.на входе регистра вызывает запуск фазы гашения, завершение которой .индицируется сбросом выходного сигнала регистра в значение логического нуля; на выходе 17,72 либо на выходе 18,80. Регистр возвращается в исходное состояние хранения информации и готов к приему следующего .входного сигнала и выполнению, сдвига в направлении, которое будет задано этим входным сигналом.

Управление состоянием логических элементов И-НЕ ячеек памяти, осуществляющих хранение и сдвиг информации в регистре, происходит с помощью управляющих сигналов Т1, Т2, ТЗ, Т4, поступающих с выходов 50, 51, 52, 53 распределителя управляющих сигналов 20 на третьи входы 54, 55, 56, 57 элементов И-НЕ 5, 6, 7, 8 каждой

ячейки памяти 4. Количество ячеек памяти 4 определяет разрядность реверсивного регистра сдвига. Исходное состояние элементов И-НЕ 5-8 в каждой ячейке памяти обеспечивается набором значений управляющих сигналов (Т1,Т2, ТЗ, Т4) (1,1,0,0). .Последовательное изменение значений уп- равляющих сигналов Т1, Т2 , Т4 приводит к изменению состояний элементов И-НЕ каждой ячейки памяти, и при определенной последовательности наборов значений управляющих сигналов вызывает сдвиг ин- формаций, хранящейся ячейками памяти. В табл. 1 и табл.2 приведены две последо- вательности наборов значений управляющих сигналов Т1-Т4 и соответствующие каждому набору значений управляющих сигналов состояния элементов Й-НЕ 5-8 для 5-й ячейки памяти. При этом табл. .1 иллюстрирует процесс выпол- нения сдвига вправо, а табл. 2 - влево. :В таблицу введены- два дополнительных столбца, а которых указаны значения выходных сигналов соответственно элемен- тбв И-НЁ 8 предыдущей ячейки памяти и элемента И-НЕ В последующей ячейки па- MXtVi. : ...-.. -У.-/ :; . - -. ,.,- ... , : Через у,у обозначено значение прямой и инверсной частей парафазнрго кода, хра нящёгося в. предыдущей и последующей ячейках памяти регистра, через z прямая часть парафазного кода, хранящегося в ячейке (I + 2), сдвигаемая в элемент И-НЕ 5 (I + 1)-ой ячейки памяти при выполнений

сдвига влево на один разряд. -Закон изменения значений управляющих сигналов Т1-Т4 описывается системой уравнений; ;;;-: : v .;., ;. ... - -;;;

::, : {T2VT4} 40 -: ; V -v лу;;;...; - Т2 ; Т4 frivTS)

.. (T2VT4);-.:

.4S-; (- .. Т4 Т2 (Т1 V ТЗ).... . . .

; ;Дяя реализации указанного закона измене- :; ния значений управляющих сигналов для ;:; управления состоянием реальных элементов 50 необходимо учесть наличие переходных про- : цессов, сопровождающих изменение состоя- ния каждого элемента И-НЕ, и кроме того, : следует ввести некоторые переменные, значения которых будут определять последова- 55 тельность изменений значений сигналов Т1-Т4 для реализации правого или левого сдвига, а также осуществлять запуск последовательности изменений сигналов Т1-Т4. ;; Указанные факторы учтены в следую- щей системе:

Т1 - ТЗ(а1(Т2T23VT4 ri2)Va2(T4 T34VT2 Г41))

Т2 Т4(а1(ТЗT34VT1 Г23) V а2{Т1 M1VT3 Г12))

ТЗ Т1(г Т441Va1 Т2 Г34 V г Т2) V а2(Т2 Г12 V ТА Г23))

Т4 Т2(а1(Т1T12VT3 Г41)У(1 ТЗ Г23 V а2 Т1 Г34 VI T1)).

В приведенной системе использованы следующие обозначения:

а1, а2 - логические переменные, значения которых определяют направления сдвига информации: (а1, а2) (1, 0)- зада- ют сдвиг вправо; (а1, а2) (0, 1) - задают сдвиг влево. Значения переменных а1 и а2 формируются блоком местного управления 21 на выходах 46 и 47 соответственно. В состоянии хранения информации значения переменных (а 1,а2)сохраняют направление последнего выполненного регистром сдвига; :

г, I - фазовые переменные запуска сдвига соответственно вправо и влево..В состоянии хранения информации регистром имеют значение логические единицы. Формируются блоком местного управления 21 соответственно на выходах 48, .49,,Запуск- сдвига вправо или влево запускается сбросом в значение логического нуля сигнала на выходе 48 или 49. Единичное значение сигнала на выходе 48 либо 49 блока местного управления 21 восстанавливается после завершения фазы гашения рабочего состояния регистра;

П - логические переменные, изменение значений которых индицируют моменты окончания переходных процессов при изменении состояний в одноименных элементах И-НЕ 5, 6, 7, 8 во всех ячейках памяти 4 регистра. Значения переменных Г41, 712, 723, 734 формируются на выходах 34, 35, 36, 37 блока индикаторов 19 соответственно. Сигнал Flj принимает единичное значение только в том случае, если в единицу установились выходные сигналы всех элементов И-НЕ 22-25 (соответствующих данному выходу блока индикаторов 19) во всех ячейках памяти 4 регистра. Сброс в 0 значения nj возможен только при переходе в О значений всех выходных сигналов соответствующих элементов И-НЕ 22-25 в ячейках памяти 4 регистра. Значения сигналов на выходах 26, 27, 28, 29 элементов И-НЕ 22- 25 в дальнейшем будем обозначать через 141,112, (23,134. Изменение значения любого из указанных сигналов с 1 на 0, либо с О на 1 свидетельствует о завершении переходных процессов в соответствующей паре ементов И-НЕ 5-8.

Работа реверсивного регистра сдвига , ; происходит следующим образом.

В исходном состоянии хранения инфор Т :мации на входах регистра 62, 63 и 64, 65

входные сигналы имеют значение логиче15 ского нуля, На выходах 48, 49 блока местного управления 21 сигналы имеют значение логической единицы. На выходах 46, 47 блока местного управления 21 сигнал может иметь произвольное значение либо {1,

0 0) либо (0, 1). На выходах 50, 51, 52, 53 распределителя управляющих сигналов 20 управляющие сигналы имеют значения (Т1, Т2, ТЗ, Т4) 1,1,0,0), обеспечивая устойчивое хранение информации элемента5 ми И-НЕ 5-8 всех ячеек памяти регистра. На

выходах 29 элементов 25 всех ячеек памяти

сигнал 34 0, так как элементы И-НЕ 7, 8

всех ячеек памяти 4 регистра находится в

состоянии единицы. Сигнал на выходах 27

0 элементов И-НЕ 23 всех ячеек памяти 4 регистра 112 1, так как элементы И-НЕ 5, 6 осуществляют хранение парафазного кода одного двоичного разряда (х,х). На выходах регистрах 17, 72 и 18, 80 сигналы имеют

5 значение логического нуля. На выходах 66,

76 блока местного управления 21 выдаются

единичные сигналы. Положим, что на входы.

62, 63 регистра подается сигнал (z, z) (1,0).

Для определенности считаем, что в регистре

0 хранится нулевое информационное слово,

т.е. элементы И-НЕ 5, 6 всех ячеек памяти

находится в состоянии (х, х) (1, 0). Сигнал

У на входах 62, 63 приводит к сбросу в

нулевое значение сигналов на выходах 48 и

5 66 блока местного управления 21, что соответствует сбросу в 0 значений переменных запуска сдвига вправо г 0 и инверсной части входного парафазного кода z 0. Нулевой сигал на выходе 48 блока местного

0 управления 21 должен осуществить запуск фазы установки сдвига вправо. Но это справедливо только в том случае, если сигналы на выходах 46, 47 соответствует направлению сдвига вправо (а1, а2) (1,0).

5 Если на выходах 46, 47 сигнал равен (а1, а2) (1, 0), т.е. хранится направление сдвига влево, то по сбросу в 0 сигнала на выходе 48 запуска фазы установки сдвига вправо не происходит, и этот запуск осуществляется

сбросом в значение логического нуля сигнала на выходе 47 блока местного управления 21, т.е. после изменения значения сигнала на выходах 46, 47 на соответствующее выполняемому сдвигу - (а 1, а2) (1,0). Нулевое значение сигнала на выходе 47 блока местного управления 21 осуществляет запуск работы распределителя управляющих сигналов 20. При том первым изменяется значение сигнала на выходе 52 распределителя 20, который устанавливается в единицу ТЗ 1. На выходах элементов И- НЕ 7 всех ячеек памяти устанавливается сигнал, равный х - прямой части парафаз- ного кода, хранящегося в конкретной ячейке памяти 4i, в рассматриваемом примере х 0 выходные сигналы элементов И-НЕ 7 во всех ячейках памяти сбросятся в 0. После окончания переходных процессов, связанных с изменением состояния элемента И- НЕ 7 в каждой ячейке памяти, на выходах 28 элементов И-НЕ 24 должен установиться сигнал логической единицы I23 1. Сигналы с выходов 28 всех ячеек памяти 41 поступают на входы группы 32 блока индикаторов 19. Когда завершаться переходные процессы во всех ячейках памяти 41, единичное значение сигнала I23 1 установится на всех входах группы 32, и на выходе 36 блока индикаторов 19 будет сформирован единичный, сигнал Г23 1. Единичный сигнал с выхода 36 блока индикаторов 19 поступает на вход. 40 распределителя управляющих сигналов 20 и запускает изменение значения управляющего сигнала Т1, значение логического нуля которого формируется на выходе 50 распределителя управляющих сигналов 20. По И 0 на выходе 50 элементы И-НЕ 5 всех ячеек памяти регистра переключаются в состояние единицы, что приводит к изменению выходного сигнала элементов И-НЕ 22 и сигнала на выходах 26 всех ячеек памяти. С выходов 26 сигналы поступают на входы группы 30 блока индикаторов 19. После сброса в значение логического нуля сигналов 141 О всех ячеек памяти на выходе 34 блока индикаторов 19 сигнал Г41 0 также сбрасывается в нуль и через вход 38 распределителя управляющих сигналов 20 обеспечивает установку единичного значения управляющего сигнала Т4 1 на выходе 53 распределителя 20. По Т4 1 элементы И- НЕ 8 всех ячеек памяти 4 на своих выходах формируют сигнал, равный инверсной части парафазного кода бита, хранящегося в соответствующей ячейке памяти, а на выходе 13 первого блока сопряжения 1 устанавливается сигнал, равный инверсной части парафазного кода, подаваемого на входы

62, 63 регистра -z . Окончание переходных процессов, связанных с переключением состояний элементов И-НЕ 8 и в первом блоке сопряжения 1, индицируется установкой 5 единичных сигналов на выходах элементов И-НЕ 25 и, соответственно, на выходах 29 всех ячеек памяти и выходе 73 первого блока сопряжения 1. Указанные сигналы поступают на входы четвертой группы 33 блока

0 индикаторов 19, Когда все сигналы I34 устанавливаются в значении логической единицы I34 10 на выходе 37 блока индикаторов 19 принимает единичное - значение сигнал Г34 1, что свидетельст5 вует о завершении переходных процессов в регистре. Через вход 41 распределителя 20 сигнал Г34 1 инициирует сброс в значение логического нуля управляющего сигнала Т2 0 на выходе 51 распределителя 20.

0 По Т2 0 элементы 6 ячеек памяти 41 переходят в состояние единицы, что приводит к установке единичных сигналов на выходах элементов И-НЕ 23 и выходах 27 всех ячеек памяти, а на выходах 18, 80 второго блока

5 сопряжения 2 формируется сигнал (х, х) парафазного кода младшего разряда регистра, выдвинутого из регистра в результате сдвига информации на один разряд вправо. Для рассматриваемого случая (х, х) (1, 0).

0 Сигналы 112 1 с выходов 27 всех ячеек памяти, поступающие на входы блока индикаторов 19 группы 31, обеспечивают формирование на выходе 35 блока индикаторов 19 единичного сигнала

5 окончания переходных процессов в регистре П2 1, который через вход 39 распределителя 20 вызывает восстановление единичного значения управляющего сигнала Т1 1 на выходе 50

0 распределителя 20. Завершена фаза установки при выполнении сдвига информации на один разряд вправо. Сигналом завершения фазы установки является выдача нэ выходах 18, 80 второго сопряжения 2

5 парафазного кода у у значения младшего разряда, выдвинутого из регистра. При этом регистр переходит в устойчивое состояние с набором значений управляющих сигналов (Т1, Т2,ТЗ,Т4) (1,0, 1,1), при

0 котором элемент И-НЕ 5 в каждой ячейке памяти на выходе выдают значение прямой части парафазного кода, хранящегося в предыдущей ячейке памяти, а элемент И-НЕ 5 первой ячейки памяти 4i на выходе

5 имеет сигнал z прямой части парафазного кода (z , z ), поданного на вход регистра 62, 63. Элементы И-НЕ 6 всех ячеек памяти находится в состоянии единицы. Элементы И-НЕ 7, 8 осуществляют хранение пара- фазного кода (х, х), хранившегося в данной

ячейке памяти до начала сдвига на элементах И-НЕ 5,6. Устойчивость этого состояния регистра обеспечивается нулевыми сигналами на выходах 48 блока местного управления 21 г 0 и на 51 распределителя управляющих сигналов 20 Т2 0, а также единичными сигналами на выходах 52, 53 распределителя 20 ТЗ Т4 1. Действитель- но:, дальнейшее изменение значений управляющих сигналов Т1-Т4 возможно при сбросе в нуль управляющего сигнала ТЗ О на выходе 52 распределителя 20, но распределитель 20 для ТЗ - реализует соотношение

ТЗ Т1 (гТ4 Г41 Val T2 Г34 Vr T2)),

которое при значениях Т2 0 и г 0 имеет устойчивое значение логической единицы. Таким образом, запуск фазы гашения для завершения рабочего цикла сдвига информации вправо возможен только при восстановлении единичного значения фазовой переменной г на выходе 28 блока местного управления 21. Реализуется запуск фазы гашения сбросом в значение логического нуля сигнала на входе регистра 62, 63 z1 z1 0, Следовательно, входной сигнал, поданный на любой вход регистра и инициировавший начало сдвига информации в регистре, должен присутствовать на этом входе до завершения фазы установки, что индицируется появлением выходного сигнала регистра. После этого для запуска фазы гашения сигал на входе регистра должен быть сброшен в значение логического нуля.

Сброс сигнала на входе 62, 63 регистра вызывает восстановление единичного значения сигнала на выходе.48 блока местного управления 21. С выхода 48 единичный сигнал поступает на вход 44 распределителя 20 и на вход 75 второго блока сопряжения 2. При том на выходах регистра 18, 80 и на выходе 52 распределителя 20 сигналы принимают значения логического нуля, что соответствует у у 0 и ТЗ 0, Нулевой сигнал на выходе 52 распределителя 20 вызывает переключение в единичное состояние элементов И-НЕ 7 всех ячеек памяти 4. . Это приводит к сбросу в 0 выходного сигнала элементов И-НЕ 24 и сигнала на выходе 28 каждойячейки памяти4-123 0. Нулевой сигнал 123 0 всех ячеек памяти свидетельствует о завершении переходных процессов в регистре и, поступая на входы группы 32 блока индикаторов 19, приводит к формированию на выходе 36 блока индикаторов 19 нулевого сигнала Г23 0. Этот сигнал подается на вход 40 распределителя 20, что приводит к восстановлению единичного

сигнала на выходе 51 распределителя 20. восстанавливается в единичном значении управляющий сигнал Т2 1. По Т2 1 на выходах элементов И-НЕ 6 всех ячеек памяти формируется сигнал, равный инверсной части парафазного кода, хранившегося в предыдущей ячейке памяти, а на выходе элемента И-НЕ 6 первой ячейки памяти 41- устанавливается значение z инверсной час0 ти входного сигнала на входах 62, 63, инициировавшего начало сдвига. Таким образом, к моменту восстановления единичного значения управляющего сигнала Т2 1 завершается выполнение сдвига информа5 ции на один разряд вправо и запись пара- фазного кода входного сигнала в старшую ячейку памяти регистра. Окончание переходных процессов, связанных с переключением состояний элементов И-НЕ 6 всех

0 ячеек памяти, индицируется сбросом в значение нуля выходных сигналов элементов И-НЕ 23 и сигналом на выходах 27 всех ячеек памяти. Сигналы 112 0 с выходов 27 ячеек памяти поступают на вход группы 31

5 блока индикаторов 19 и обеспечивают формирование сигнала 712 0 на выходе 35 блока индикаторов 19, с которого нулевой сигнал подается на вход 39 распределителя 20, вызывая сброс в значение логического

0 нуля управляющего сигнала Т4 0 на выходе 53 распределителя 20. По сигналу Т4 О восстанавливается единичный выход элемента И-НЕ 8 всех ячеек памяти и реверсив- ный регистр сдвига возвращается в

5 исходное состояние хранения информации. Сдвиг влево в регистре запускается подачей сигнала z z на входы 64, 65. При этом сбрасывается в нуль сигнал на выходе 49 блока местного управления 21, что соот0 ветствует сбросу в 0 значения фазовой переменной запуска сдвига влево I О, Аналогично запуску сдвига вправо, если значение парафазной переменной направления сдвига на выходах 46, 47 блока мест5 ного управления 21 соответствует сдвигу влево (а 1, а2) (0, 1), то по нулевому сигналу на выходе 49 происходит запуск распределителя управляющих сигналов 20, и, следо- . вательно, сдвига влево. Если на выходах 46,

0 47 сигнал равен (а1, а2) (1, 0), что соответствует направлению сдвигу вправо, нулевой сигнал на выходе 49 не может осуществить запуск фазы установки сдвига влево, и запуск происходит по сбросу в нуль сигнала на

5 выходе 46, т.е. после изменения значения парафазной переменной направления сдвига (э1, а2) (О, Т), которое осуществляется через транзитное состояние (а1, а2) (1, 1), также не позволяющее произойти запуску фазы установки. Дальнейшая работа регистpa при сдвиге влево происходит аналогично сдвигу вправо с точностью до наборов значений управляющих сигналов Т1-Т4 на выходах 50-53 распределителя 20. Конец фазы установки индицируется получением пара- фазного кода разряда, выдвинутого из старшего разряда регистра, на выходах 17, 72, что разрешает осуществить сброс сигнала на входах 64, 65 регистра. Сброс сигнала на выходах 17, 72 свидетельствует о завершении фазы гашения и возможности установки на входах регистра 62, 63 или 64, 65 нового сигнала для запуска следующего цикла сдвига информации регистром.

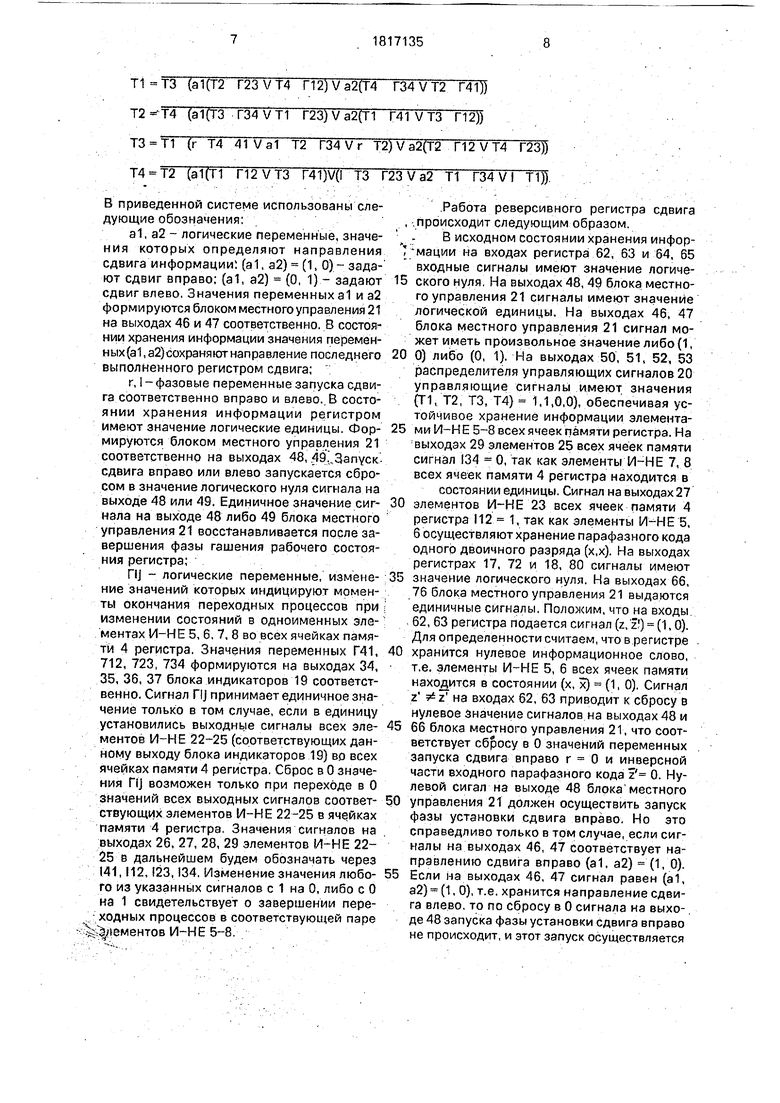

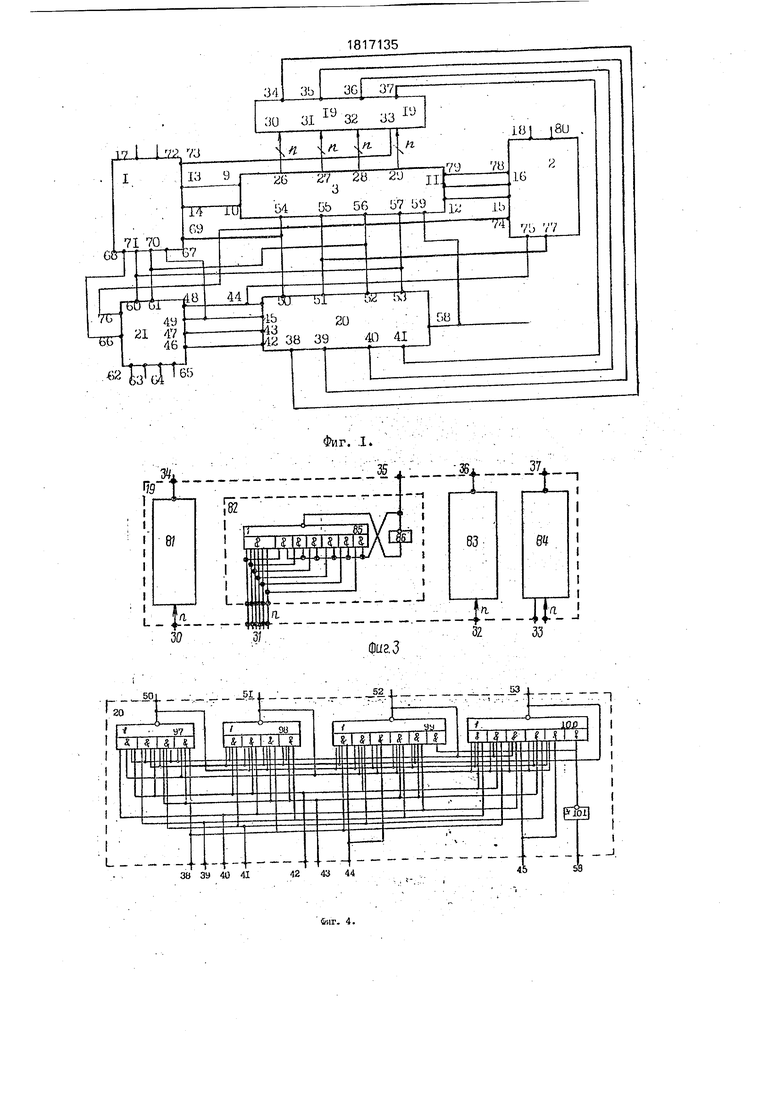

На фиг. 3 показана смешанная схема варианта исполнения блока индикаторов 19, предназначенного для формирования сигналов завершения переходных процессов определенных элементов И-НЕ всех ячеек памяти. Эти сигналы 741,712, 723,734 формируются на выходах 34, 35,36,37 блока индикаторов 19 по сигналам lij, поступающим на входы групп 30, 31, 32, 33 с соответствующих выходов 26, 27, 28, 29 всех ячеек памяти регистра. Каждая из групп указанных входов содержит п связей за исключением группы входов 33, на которую кроме п связей, поступающих с 29 выхода всех ячеек памяти, подается также сигнал с 73 выхода первого блока сопряжения 1. Блок индикаторов состоит из четырех Г-триггеров 81, 82. 83 и 84, выходы которых являются соответственно отдельными группами входов блока индикаторов 30, 31. 32, 33. Выходы Г-триггеров являются соответствующими выходами блока индикаторов 34, 25. 36, 37, при этом выходы блока индикаторов соединены соответственно с первыми четырьмя входа- ми 38, 39, 40, 41 распределителя управляющих сигналов 20. В состав каждого Г-триггера входит элемент И-ИЛИ-НЕ 85 и элемент ИЛИ-НЁ 86. Работает блок индикаторов следующим образом. При любом значении сигнала на выходе каждого Г-триггера его изменение может произойти только при изменении на противоположное значение всех его входных сигналов. Если выходной сигнал Г-триггера равен значению логической единицы, то изменение некоторых входных сигналов lij с 1 на 0 не оказывает влияния на выходной сигнал Г-триггера. Выходной сигнал Г-триггера сбросится в значение логического нуля только при условии, что все сигналы на его входах lij примут значение 0, Установка единичного выходного сигнала Г-триггера происходит аналогичным образом. Это свойство Г-триггеров обеспечивает возможность индикации по значениям сигналов flj моментов окончания

переходных процессов при переключении соответствующих элементов И-НЕ во-всех ячейках памяти по изменению значений всех соответствующих переменных lij. 5

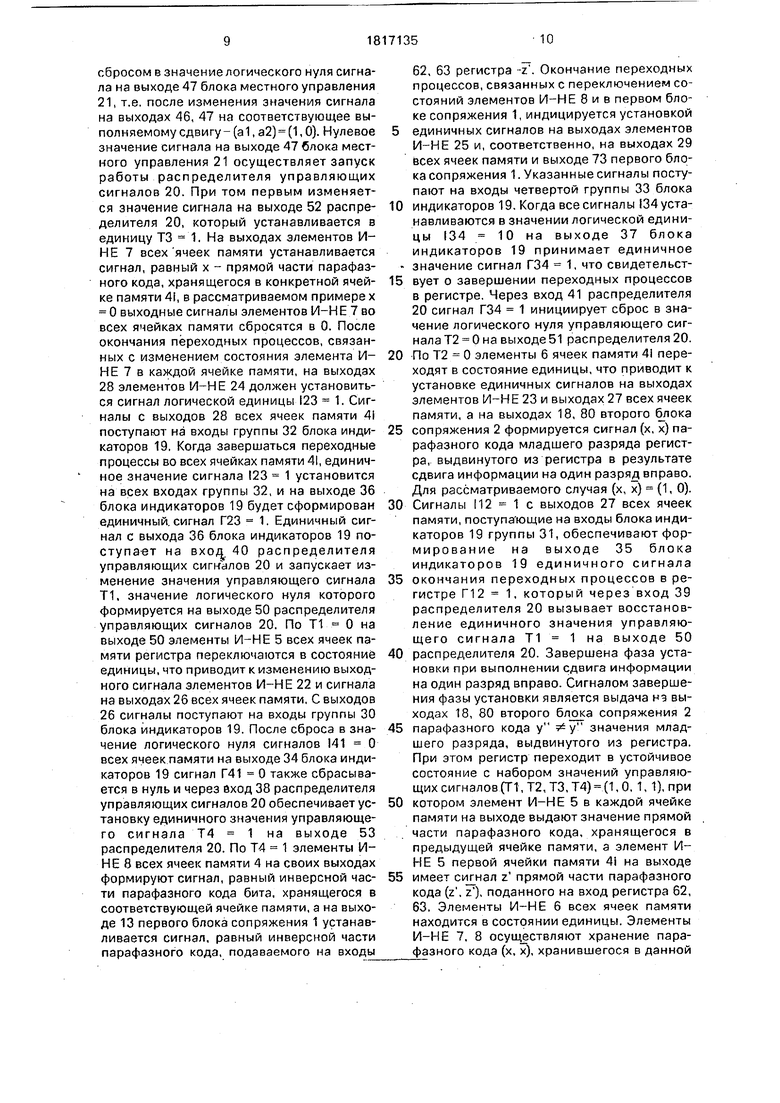

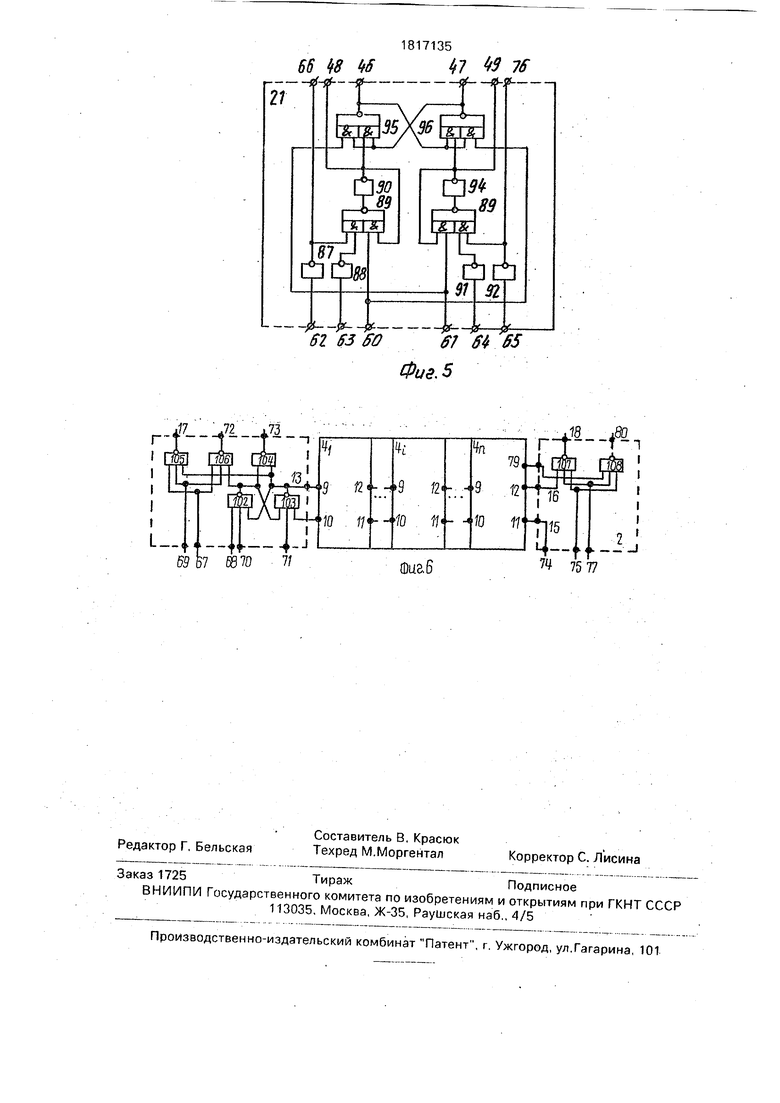

На фиг. 5 приводится функциональная схема одного из возможных вариантов выполнения блока местного управления 21, В состав блока местного управления, пред0 назначенного для формирования значений фазовых переменных запуска сдвига вправо г и влево I, парафазией переменной направления сдвига (а1, а2),. а также инверсной части входного сигнала z и прямой части

5 входного сигнала z, входят элементы И-НЕ 87, 88, элемент И-ИЛИ-НЕ 89 и элемент И-НЕ 90, которые обеспечивают формирование значений фазовой переменной запуска сдвига вправо г и инверсной части

0 входного сигнала z , и выдачу их значений на выходах 48 и 66 блока местного управления соответственно. Кроме того, в состав блока местного управления 21 входят элементы И-НЕ 91, 92, элемент И-ИЛИ-НЕ 93

5 и элемент И-НЕ 94, которые формируют и выдают на выходы 79 и 76 значения фазовой переменной запуска сдвига влево I и прямой части входного сигнала z, а также два элемента И-ИЛИ-НЕ 95 и 96, реализующих

0 триггер для формирования и хранения значения парафазной переменной направления сдвига (а1, а2), значения которой выдаются на выходах 46, 47 блока местного управления 21. Работа блока местного уп5 равления происходит следующим образом, В исходном состоянии хранения информации регистром на входах 60, 61 подан нулевой сигнал с выходов 53, 52 распределителя управляющих сигналов 20, что соответству0 ет нулевым значениям управляющих сигналов Т4 ТЗ 0. На входах 62, 63 и 64, 65 нулевые сигналы соответствуют отсутствию входных - сигналов на регистр. Соответственно на выходах элементов И-НЕ

5 87, 88 и 91, 92 сигналы имеют значение логической единицы, Эти единичные сигналы с выходов элементов И-НЕ 87 и 92 подаются соответственно на выходы 66 и 76 блока местного управления. Выходные

0 сигналы элементов И-ИЛИ-НЕ 89 и 93 имеют значение логического нуля, и, следовательно, с выходов элементов Й-НЕ 90, 94 на выходы 48 и 49 передается единичное значение фазовых переменных г и I. Эле5 менты И-ИЛИ-НЕ 95, 96 триггера находятся в произвольном устойчивом состоянии (1, 0) либо (0, 1), соответствующие сигналы с выходов указанных элементов передаются на выходы 46, 47 блока местного управления.

Положим, что на вход 62 подан единичный сигнал. При этом произойдет сброс в значение нуля выходного сигнала элемента И-НЕ 87 и на выходе 66 блока местного управления. Изменение выходного сигнала элемента 87 вызывает установку в единицу выходного сигнала элемента И-ИЛИ--НЕ 89, что приводит к сбросу в нуль выходного сигнала элемента И-НЕ 90 и сигнала на выходе 48 блока местного управления. Таким рбразом, подача входного сигнала z на входы 62. 63 регистра вызывает сброс в значение логического нуля фазовой переменной запуска сдвига вправо г на выходе 48 блока местного управления 21. Очевидно, что сигнал (z , z ) (0, 1) на входах 62, 63 регистра дает тот же самым результат. Сигнал с выхода элемента И-НЕ 90 поступает также на одну из групп входов элемента И-ИЛИ-НЕ 95, и сброс его в значение нуля вызывает переключение состояния триггера на элементах И-ИЛИ-НЕ 95, 96 через транзитное состояние (1, 1) в состояние (1, 0), что соответствует значению парафазией переменной (а1, а2) (1, 0) - сдвиг вправо. Если состояние триггера на элементах И-ИЛИ-НЕ 95, 96 было (а1. а2) (1, 0) - сдвиг вправо, сброс в значение нуля выходного сигнала элемента И-НЕ 90 только подтверждает это состояние. Нулевой сигнал на выходе 48 либо на выходе 47, если происходит изменение состояния триггера направления сдвига на элементах И-ИЛИ-НЕ 95, 96, осуществляют запуск фазы установки состояния сдвига вправо. В состоянии фазы установки на входах 60, 61 блока местного управления 21 происходит изменение значений управляющих (сигналов Т4 и ТЗ, но изменения этих сигналов не оказывают влияния на состояние элементов блока местного управления. Состояние блока местного управления остается неизменным до окончания фазы установки и запуск фазы гашения, В момент окончания фазы установки на входах 60, 61 устанавливаются сигналы логической единицы. Запуск фазы гашения возможен только при сбросе в нуль входного сигнала на входах 62, 63. Сброс в нулевое значение сигнала на входах 62, 63 приводит к восстановлению единичного сигнала на выходе элемента И-НЕ 87 либо И-НЕ 88. В любом случае сбрасывается в нулевое значение сигнал на выходе элемента Й-ИЛИ- НЕ 89 и восстанавливается единичное значение сигнала на выходе элемента И-НЕ 90 и на выходе 48 блока местного управления. Запускается фаза гашения. Завершение фазы гашения в блоке .местного управления не индицируется, и поэтому после сброса входного сигнала на лкЗЬом из

входов регистра существует принципиальная возможность появления нового входного сигнала до восстановления в регистре исходного состояния хранения информации. Для блока местного управления возврат регистра в исходное состояние индицируется: при сдвиге вправо - сбросом в значение нуля сигнала на ходе 60, при сдвиге влево - сбросом в значение нуля

0 сигнала на входе 61. Пусть после сброса в нулевое значение сигналов на входах 62, 63 и запуска фазы гашения на эти же входы 62, 63 выставляется новый входной сигнал (z , z1) (0, 1). При этом на входе 60 сигнал

5 имеет единичное значение: Т4 1 - регистр завершил фазу гашения, но не возвратился в исходное состояние. Единичный сигнал на входе 63 вызывает сброс выходного сигнала элемента И-НЕ 88 в значение нуля, однако

0 это не приводит к изменению выходного сигнала элемента И-ИЛИ-НЕ 89, так как единичные сигналы с выхода элемента И- Н Е 90 и с входа 60 удерживаются его выходной сигнал в значение нуля, Значение

5 сигнала на выходе 48 блока местного управления не изменяет своего единичного значения и запуск новой фазы установки не происходит. Запуск нового сдвига произойдет только после возвращения регистра в

0 исходное состояние по сбросу в значение нуля сигнала на входе 60. Возможен другой вариант, когда регистр не возвратился в исходное состояние после выполнения сдвига вправо и поступает новый сигнал на входы

5 64, 65. При этом сбрасывается в значение

нуля выходной сигнал элемента И-НЕ 91

или 92. Сигнал на выходе элемента И-ИЛИ.НЕ 93 принимает единичное значение и

сбрасывается в нуль сигнал на выходе эле0 мента И-НЕ 94 и на выходе 49 блока местного управления. Однако запуска фазы установки не происходит, так как триггер управления сдвига находится в состояние (а1, а2) (1, 0) -- сдвиг вправо, и нулевой

5 сигнал с выхода элемента И-Н Е 94 не может изменить состояние элемента И-ИЛИ-НЕ 96 и всего триггера в целом, поскольку элемент И-ИЛИ-НЕ 96 удерживается в нулевом состоянии единичными сигналами,

0 поступающими на одну из групп его входов с выхода элемента И-ИЛИ-НЕ 95 и с входа 60 блока местного управления. Запуск фазы установки сдвига влево произойдет только после возвращения регистра в исходное со5 стояние, когда сбросится в значение нуля сигнал на входе 60 блока местного управления. Последний вариант при выполнении сдвига влево и поступлении сигнала г & г на входы 62, 63. При этом через последовательные изменения сигналов на выходах

элементов И-НЕ 87 или 88, элемента 1/1- ИЛ И-НЕ 89, элемента И-НЕ 90 происходит в нулевое значение сигнала на выходе 48 блока местного управления, однако триггер направления сдвига остается в состоянии сдвига влево, так как элемент И-ИЛИ-НЕ 95 удерживается в состоянии нуля единичными сигналами с выхода элемента И- ИЛИ-НЕ 96 и с входа 61 блока местного управления. Запуск фазы установки сдвига вправо произойдет после возвращения регистра в исходное состояние, когда сигнал на входе 61 примет значение логического нуля. Работа блока местного управления 21 при выполнении регистром сдвига влево происходит аналогичным образом с точностью до номеров логических элементов.

Блоки индикаторов 19 и местного управления 21 обеспечивают запуск и работу в фазах установки и гашения распределите- ля управляющих сигналов 20, функциональная схема которого приведена на фиг. 4. Распределитель управляющих сигналов 20 предназначен для формирования последовательности значений управляющих сигна- лов Т1-Т4, обеспечивающих определенный порядок изменения состояний элементов И-НЕ ячеек памяти регистра 4, приводящий к сдвигу информации в определен- ном направлении, и обеспечивать набор значений управляющих сигналов (Т1, Т2, ТЗ, Т4) (1, 1, 0, 0) в состоянии хранения информации регистром. Распределитель управляющих сигналов 20 состоит из четырех элементов И-ИЛИ-НЕ 97, 98, 99, 100, выхо- ды которых являются выходами распределителя 50, 51, 52, 53 соответственно. Кроме того, в состав распределителя входит элемент И-НЕ 101, соединенный входом с девятым входом распределителя 58. Каждый элемент И-ИЛИ-Н Е 97-100 реализует уравнение для значения одного управляющего сигнала Т1, Т2, ТЗ, Т4 из системы управле- ий, указанной выше, поэтому отдельные группы входов элементов И-ИЛИ-НЕ 97- 100 соединены с соответствующими входами распределителя 38-41, на которые поступают сигналы П с выходов 34-37 блока индикаторов 19, 42 и 43, на которые с выходов 46 и 47 блока местного управления 21 поступают значения парафазной переменной (а1, а2) направление сдвига, и с входами распределителя 44 и 45, на которые с выходов 48 и 49 блока местного управления 21 поступают значения фазовых перемен- ных запуска сдвига г - вправо и I - влево. Кроме того, входы отдельных групп входов элементов И-ИЛИ-НЕ 97-100 соединены с выходами соответствующих элементов И-ИЛИ-НЕ 97-100, что сформировать на каждой группе входов конкретную конъюнкцию, отрицание дизъюнкции которых на выходах элементов И-ИЛИ-НЕ 97-100 дают значение соответствукж его управляющего сигнала Т1-Т4. Последняя группа входов элементов И-ИЛИ-НЕ 99 и 100 имеет один вход, соединенный с выходом элемента И- НЕ 101. Сброс в значение нуля входного сигнала элемента И-НЕ. 101 обеспечивает переключение элементов И-ИЛИ-НЕ 99, 100 в состояние нуля и всего распределителя 20 в устойчивое состояние с набором сигналов на его выходах 50, 51, 52, 53 (Т1, Т2, ТЗ, Т4) (1. 1, 0. 0). а всего регистра в исходное состояние. В дальнейшем при непрерывной работе реверсивного регистра сдвига сигнал на входе элемента И-НЕ 101, который является входом начальной установки регистра 58, должен сохранять значение логической единицы. Сигнал с входа 58 подается также на четвертый вход элемента И-НЕ 6 каждой ячейки памяти, и при начальной установки регистра сбросом в нуль сигнала на входе 58 осуществляется переключение элементов И-НЕ 6 всех ячеек памяти в единичное состояние, что при наборе управляющих сигналов (Т1, Т2, ТЗ, Т4) (1, 1, 0, 0) обеспечивает исходное состояние элементов И-НЕ 5-8 всех ячеек памяти (О, 1, 1, соответственно.

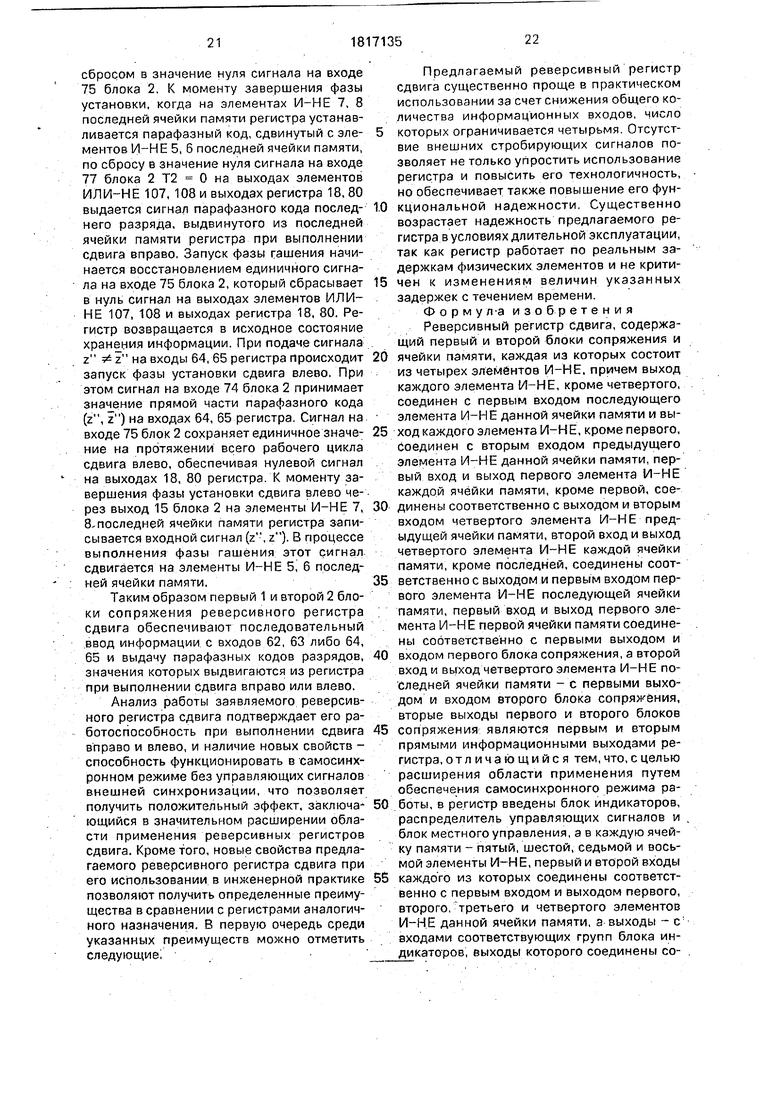

На фиг. 6 показана схема ячеек памяти регистра и варианта схем первого 1 и второго 2 блоков сопряжения. Блоки сопряжения 1 и 2 предназначены для осуществления связи при обмене информацией реверсивного регистра сдвига с внешней средой. При этом при выполнении вправо сдвига первый блок сопряжения 1 выполняет запись входного сигнала с входов 62, 63 регистра в первую ячейку памяти, хранящую старший разряд слова информации регистра, а второй блок сопряжения 2 обеспечивают вывод парафазного кода младшего разряда из последней ячейки памяти регистра. При сдвиге влево второй блок сопряжения 2 выполняет запись сигнала с входа 65, 64 в качестве младшего разряда в последнюю ячейку памяти регистра, а первый блок сопряжения 1 осуществляют вывод парафазного кода старшего разряда из первой ячейки памяти регистра.

Первый блок сопряжения 1 состоит из трех элементов И-НЕ 102, 103, 104 и двух элементов ИЛИ-НЕ 105, 106. Элементы И- НЕ 102 и 103 образуют триггер, и выполняют функции, аналогичные функциям элементов И-НЕ 7 и 8 ячеек памяти регистра, Выходами элементы И-НЕ 102, 103 соединены с входами элемента И-НЕ 104, который осуществляет функции индикатора окончания

переходных процессов при переключении элементов И--НЕ 102 и 103, формируя на выходе 73 первого блока сопряжения сигнал I34, передаваемый на последний вход группы 33 блока индикаторов 19. Кроме того, элементы И-НЕ 102, 103 выходами соединены соответственно с входами элементов ИЛ И-НЕ 105, 106, остальные два входа которых соединены с 69 и 67 входами первого блока сопряжения 1,соединённого этими входами с 50 выходом распределителя 20 и 49 выходом блока местного управления 21. Выход элемента И-НЕ 103 соединен также с первым выходом 13 блока сопряжения 1. Входы элемента И-НЕ 102 соединены с входами 68 и 70 блока сопряжения 1. На эти входы блока сопряжения 1 подаются сигналы соответственно с выхода 66 блока местного управления 21 и выхода 52 распределителя управляющих сигналов 20. Входы элемента И-НЕ 103 соединены с первым входом 14 и шестым входом 71 блока сопряжения 1, на которые поступают сигналы со- ответственно с выхода первой ячейки памяти 10 и с выхода 53 распределителя управляющих сигналов 20. Выходы элементов ИЛИ-НЕ 105, 106 являются первыми прямым и инверсным выходами регистра 17 и 72 соответственно.

В исходном состоянии хранения информации регистром на входах 70, 71 блока сопряжения-1 сигналы имеют значение логического нуля, что соответствует нулевым значениям управляющих сигналов ТЗ Т4 - 0 и обеспечивает единичные значения сигналов на выходах элементов И-НЕ 102, 103, На входах 67 и 69 сигналы имеют единичное значение: I 0 и Т1 1 - фазовая переменная сдвига влево и управляющий сигнал Т1, что удерживает выходные сигналы элементов ИЛИ-НЕ 105, 106 в нулевом значении, На выходе элемента И- НЕ 104 нулевой сигнал I34 0. При подаче сигнала z z на входы 62, 63 регистра происходит запуск фазы установки сдвига вправо. Начинается последовательное изменение значений управляющих сигналов Т1, ТЗ, Т4 на входах 69, 70, 71 блока сопряжения 1. Притом на протяжении всего рабочего цикла сдвига вправо нулевой сигнал на выходах 17, 72 остается неизменным, поскольку в единичном значении остается сигнал на входе 67 I 1. На входе 68 при запуске фазы установки вправо формируется сигнал г - инверсной части сигнала на входах 62, 63 регистра. К моменту завершения фазы установки при значениях сигналов на входах 69, 70, 71 (Т1, ТЗ, Т4) - (1, 1, 1) на цементах И-НЕ 102,103 оказывается запи- сйнным входной сигнал (z , z ) с входов 62,

63 регистра. В процессе выполнения фазы гашения этот сигнал через выход 13 блока сопряжения 1 переписывается на элементы И-НЕ 5, 6 первой ячейки памяти. При вы- полнении сдвига влево на входе 67 блока

I сигнал сбрасывается в нулевое значение одновременно с запуском фазы установки. К моменту завершения фазы установки при единичных сигналах на входах 70, 71,

0 73 74 1 на элементах И-НЕ 102, 103 оказывается записанным сигнал (х, х), хранившийся на элементах И-НЕ 5, 6 первой ячейки памяти регистра. При окончании фазы установки сдвига влево сигнал на входе

5 69 блока 1 сбрасывается в нулевое значение и на выходах элементов ИЛИ-НЕ 103, 106 формируется парафазный код сигнала, выдвинутого при сдвиге влево из .регистра, и этот код выдается на выходы регистра 17 и

0 72. При завершении фазы гашения сигнал на входе 67 восстанавливается в единичном значении и это приводит к сбросу в нулевое значение сигналов на выходах элементов ИЛИ-НЕ 105, 106 и-выходах регистра 17, 72.

5 Регистр возвращается в исходное состояние хранения информации.

Второй блок сопряжения 2 состоит из двух элементов ИЛИ-НЕ 107 и 108. Выходы этих элементов являются вторыми прямым

0 и инверсным выходами регистра 18 и 80. Двумя входами элементы ИЛИ-НЕ 107, 108 соединены с входами 75, 77 блока 2, на которые поступают сигналы с выходов 48 блока местного управления 21 и 51 распре5 делителя управляющих сигналов 20, на которых формируются значения фазовой переменной г запуска сдвига вправо и управляющего сигнала Т2. Третьими входами элементы ИЛИ-НЕ 107 и 108 соединены со0 ответственно с входом 16 и входом 78 блока 2, на которые поступают сигналы с выхода 12 последней ячейки памяти и с выхода элемента И-НЕ Г последней ячейки памяти. На вход 74 блока 2 с. выхода 76 блока местного

5 управления 21 поступает значение прямой части входного сигнала с входов 64, 65 регистра. Выход 15 блока 1 соединен с входом

II последней ячейки памяти регистра. В исходном состоянии хранения информации

0 регистров на входах 74, 75, 77 блока 1 поданы единичные сигналы z, r, T2. На входах 78, 16 также сигналы имеют значение единицы с выходов элементов И-НЕ 7, 8 последней ячейки памяти регистра. На

5 выходах элементов ИЛИ-НЕ 107. 108 и регистра 18, 80 сигнал имеет значение логического нуля.

При подаче сигнала z на входы регистра 62, 63 происходит запуск фазы установки сдвига вправо, что сопровождается

сбросом в значение нуля сигнала на входе 75 блока 2. К моменту завершения фазы установки, когда на элементах И-НЕ 7, 8 последней ячейки памяти регистра устанавливается парафазный код, сдвинутый с элементов И-НЕ 5, 6 последней ячейки памяти, по сбросу в значение нуля сигнала на входе 77 блока 2 Т2 0 на выходах элементов ИЛ И-НЕ 107, 108 и выходах регистра 18, 80 выдается сигнал парафазного кода последнего разряда, выдвинутого из последней ячейки памяти регистра при выполнении сдвига вправо, Запуск фазы гашения начинается восстановлением единичного сигнала на входе 75 блока 2, который сбрасывает в нуль сигнал на выходах элементов ИЛИ- НЕ 107, 108 и выходах регистра 18, 80. Регистр возвращается в исходное состояние хранения информации. При подаче сигнала z & z на входы 64, 65 регистра происходит запуск фазы установки сдвига влево. При этом сигнал на входе 74 блока 2 принимает значение прямой части парафазного кода (z, z) на входах 64, 65 регистра. Сигнал на входе 75 блок 2 сохраняет единичное значение на протяжении всего рабочего цикла сдвига влево, обеспечивая нулевой сигнал на выходах 18, 80 регистра. К моменту завершения фазы установки сдвига влево че- рез выход 15 блока 2 на элементы И-НЕ 7, 8хпоследней ячейки памяти регистра записывается входной сигнал (z, z). В процессе выполнения фазы гашения этот сигнал сдвигается на элементы И-НЕ 5 6 последней ячейки памяти.

Таким образом первый 1 и второй 2 блоки сопряжения реверсивного регистра сдвига обеспечивают последовательный .ввод информации с входов 62, 63 либо 64, 65 и выдачу парафазных кодов разрядов, значения которых выдвигаются из регистра при выполнении сдвига вправо или влево.

Анализ работы заявляемого реверсивного регистра сдвига подтверждает его работоспособность при выполнении сдвига вправо и влево, и наличие новых свойств - способность функционировать в самосинхронном режиме без управляющих сигналов внешней синхронизации, что позволяет получить положительный эффект, заключа ющийся в значительном расширении области применения реверсивных регистров сдвига. Кроме того, новые свойства предлагаемого реверсивного регистра сдвига при его использовании в инженерной практике позволяют получить определенные преимущества в сравнении с регистрами аналогичного назначения. В первую очередь среди указанных преимуществ можно отметить следующие.

Предлагаемый реверсивный регистр сдвига существенно проще в практическом использовании за счет снижения общего количества информационных входов, число 5 которых ограничивается четырьмя. Отсутствие внешних стробирующих сигналов позволяет не только упростить использование регистра и повысить его технологичность, но обеспечивает также повышение его фун.0 кциональной надежности. Существенно возрастает надежность предлагаемого регистра в условиях длительной эксплуатации, так как регистр работает по реальным задержкам физических элементов и не крити5 чен к изменениям величин указанных задержек с течением времени.

Форму л-а изобретения Реверсивный регистр сдвига, содержащий первый и второй блоки сопряжения и

0 ячейки памяти, каждая из которых состоит из четырех элементов И-НЕ, причем выход каждого элемента И-НЕ, кроме четвертого, соединен с первым входом последующего элемента И-НЕ данной ячейки памяти и вы5 ход каждого элемента И-НЕ, кроме первого, соединен с вторым входом предыдущего элемента И-НЕ данной ячейки памяти, первый вход и выход первого элемента И-НЕ каждой ячейки памяти, кроме первой, сое0 динены соответственно с выходом и вторым входом четвертого элемента И-НЕ предыдущей ячейки памяти, второй вход и выход четвертого элемента И-НЕ каждой ячейки памяти, кроме последней, соединены соот5 ветственно с выходом и первым входом первого элемента И-НЕ последующей ячейки

; памяти, первый вход и выход первого элемента И-НЕ первой ячейки памяти соединены соответственно с первыми выходом и

0 входом первого блока сопряжения, а второй вход и выход четвертого элемента И-НЕ по- следней ячейки памяти - с первыми выходом и входом второго блока сопряжения, вторые выходы первого и второго блоков

5 сопряжения являются первым и вторым прямыми информационными выходами регистра, отличающийся тем, что, с целью расширения области применения путем обеспечения самосинхронного режима ра0 боты, в регистр введены блок индикаторов, распределитель управляющих сигналов и блок местного управления, а в каждую ячейку памяти - пятый, шестой, седьмой и восьмой элементы И-НЕ, первый и второй входы

5 каждого из которых соединены соответственно с первым входом и выходом первого, второго, третьего и четвертого элементов И-НЕ данной ячейки памяти, а выходы - с входами соответствующих групп блока индикаторов, выходы которого соединены со- .

ответственно с первым, вторым, третьим и четвертым входами распределителя управляющих сигналов, пятый, шестой, седьмой и восьмой входы которого соединены соответственно с первым, вторым, третьим и четвертым .выходами блока местного управления, первый, второй, третий и четвертый выходы распределителя управляющих сигналов соединены с третьими входами соответствующих элементов И- .НЕ каждой ячейки памяти, девятый вход распределителя управляющих бигналов соединен с четвертым входом второго элёмен- та И-НЕ каждой ячейки памяти И является ; входом, начальной установки регистра, чет- вертый и третий выходы распределителя управляющих сигналов соединены собтвет- ственно с первым и вторым входами блока местного управлений, третий, четвертый, пятый и шестой входы которого являются первыми прямым и инверсным и вторыми

прямым и цнверсным входами регистра, четвертый и пятый выходы блока местного управления соединены с вторым и третьим входами первого блока сопряжения, четвертый, пятый и шестой входы которого соединены соответственно с первым, третьим и четвертым выходами распределителя управляющих сигналов, третий выход первого блока сопряжения является первым инверсный выходом регистра, а четвертый выход соединен с последним, входом четвертой группы блока индикаторов, второй и третий входы второго блока сопряжения соединены; с шестым и третьим выходами блока меёТного управления, четвертый вход;- с вторым выходом распределителя управляющих сигналов; атгятый вход - с выходом третьего элемента И-НЁ последней ячейки памяти, третий выход второго блока Сопряжения является вторым инверсным выходом регистра.. ;; :.; .. л :;:;.;,- ,.

Та б л и Ц а 1

Таблица 2

Фиг. 1.

Л

82

L

.3/.

I fa

. - - - -. - .. - - - -. - -Ј.

Фиг.З

32

33

50)

5I.

35

36

37

±

. - .. - - - -. - -Ј

Фиг.З

32

33

52

53

1Физ.5

| Букреев И.Н., Мансуров В.М., Горячев В.И | |||

| Микроэлектронные схемы цифровых устройств | |||

| - М,: Советское радио, 1973, с | |||

| Ударно-долбежная врубовая машина | 1921 |

|

SU115A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Реверсивный сдвигающий регистр | 1977 |

|

SU734809A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1993-05-23—Публикация

1989-06-16—Подача