Изобретение относится к вычислительной технике и может быть использовано в системах числового программного управления.

Цель изобретения - сокращение аппаратурных затрат и объема постоянной памяти.

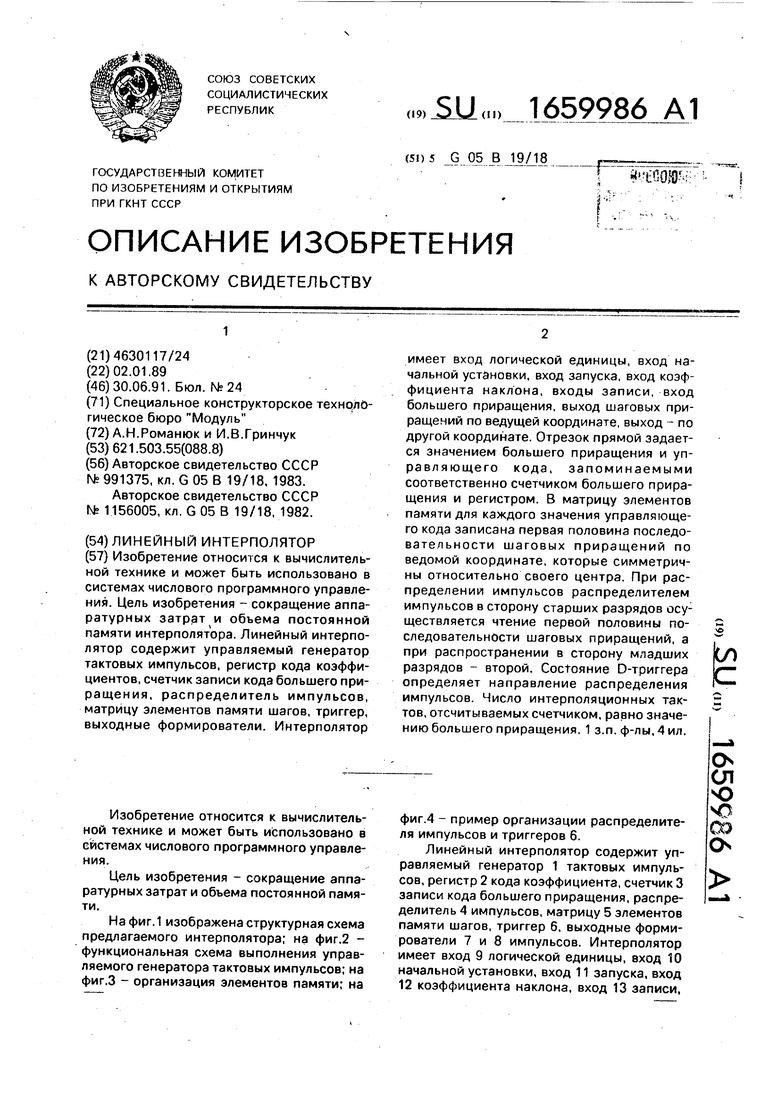

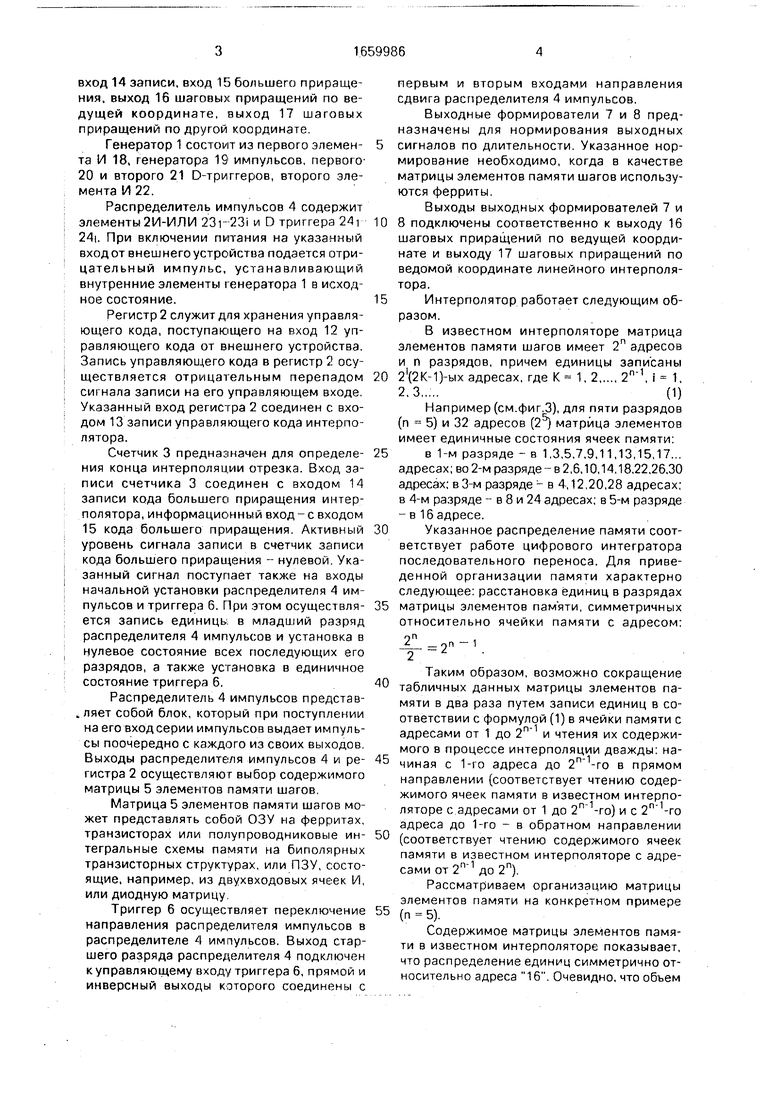

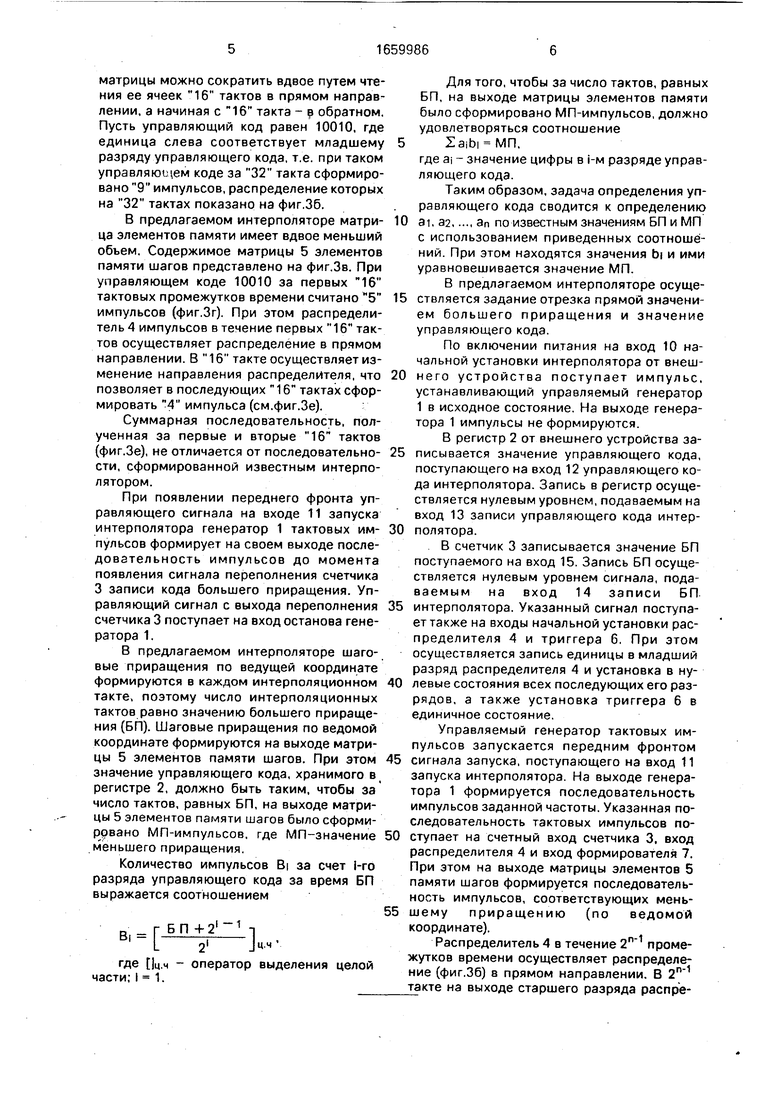

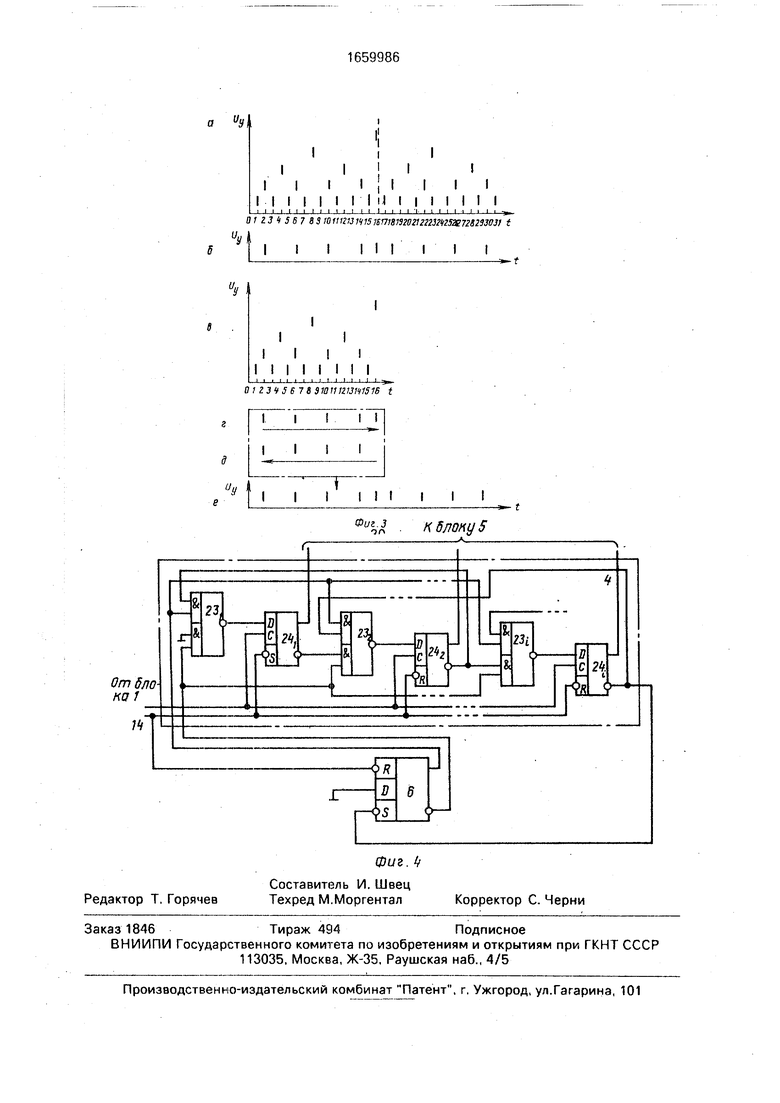

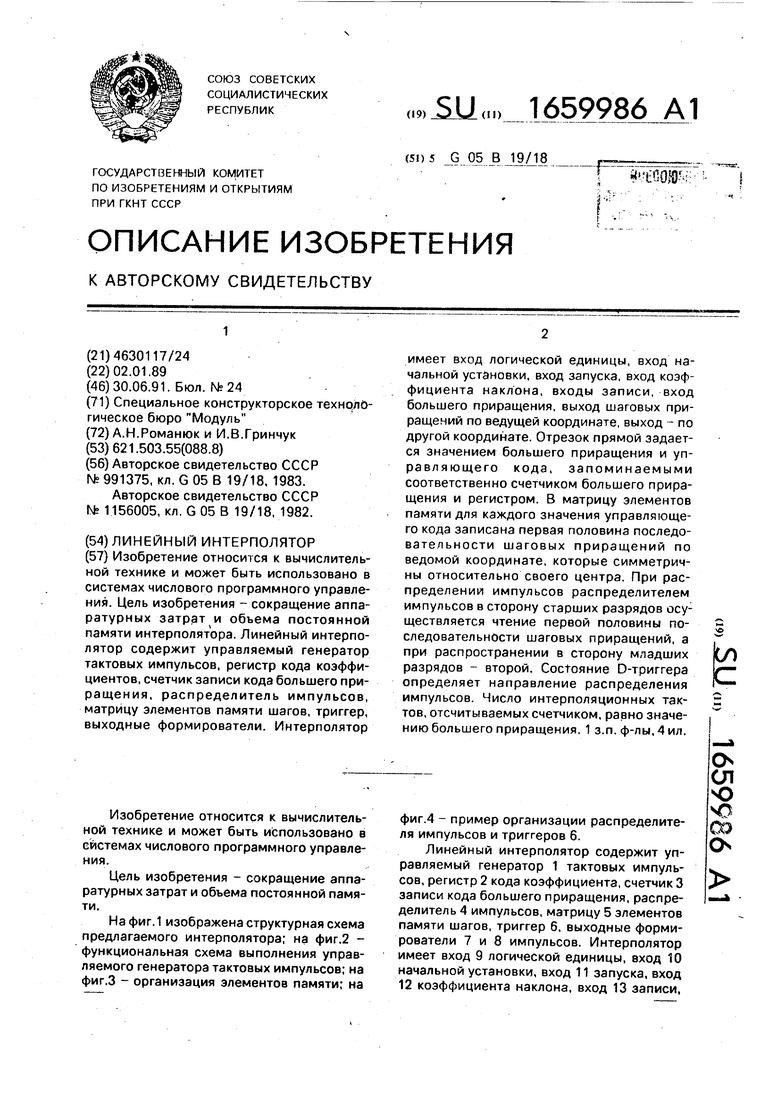

На фиг.1 изображена структурная схема предлагаемого интерполятора; на фиг.2 - функциональная схема выполнения управляемого генератора тактовых импульсов; на фиг.З - организация элементов памяти; на

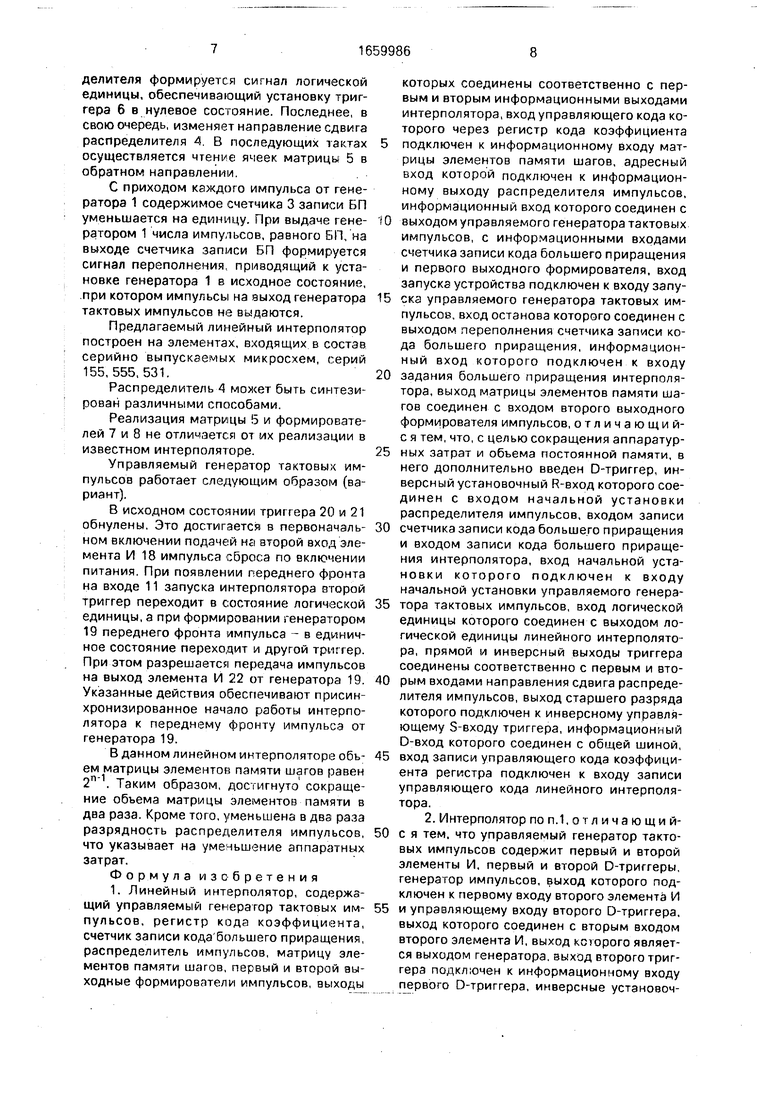

фиг.4 - пример организации распределителя импульсов и триггеров 6.

Линейный интерполятор содержит управляемый генератор 1 тактовых импульсов, регистр 2 кода коэффициента, счетчик 3 записи кода большего приращения, распределитель 4 импульсов, матрицу 5 элементов памяти шагов, триггер 6, выходные формирователи 7 и 8 импульсов. Интерполятор имеет вход 9 логической единицы, вход 10 начальной установки, вход 11 запуска, вход 12 коэффициента наклона, вход 13 записи.

Os

сл ю

ч со о

вход 14 записи, вход 15 большего приращения, выход 16 шаговых приращений по ведущей координате, выход 17 шаговых приращений по другой координате.

Генератор 1 состоит из первого элемента И 18, генератора 19 импульсов, первого- 20 и второго 21 D-триггеров, второго элемента И 22.

Распределитель импульсов 4 содержит элементы 2И-ИЛИ и D триггера 24i 24|. При включении питания на указанный вход от внешнего устройства подается отрицательный импульс, устанавливающий внутренние элементы генератора 1 в исходное состояние.

Регистр 2 служит для хранения управляющего кода, поступающего на вход 12 управляющего кода от внешнего устройства. Запись управляющего кода в регистр 2 осуществляется отрицательным перепадом сигнала записи на его управляющем входе. Указанный вход регистра 2 соединен с входом 13 записи управляющего кода интерполятора.

Счетчик 3 предназначен для определения конца интерполяции отрезка. Вход записи счетчика 3 соединен с входом 14 записи кода большего приращения интерполятора, информационный вход-с входом 15 кода большего приращения. Активный уровень сигнала записи в счетчик записи кода большего приращения - нулевой. Указанный сигнал поступает также на входы начальной установки распределителя 4 импульсов и триггера 6. При этом осуществляется запись единицы в младший разряд распределителя 4 импульсов и установка в нулевое состояние всех последующих его разрядов, а также установка в единичное состояние триггера 6.

Распределитель 4 импульсов представ- ,. ляет собой блок, который при поступлении на его вход серии импульсов выдает импульсы поочередно с каждого из своих выходов Выходы распределителя импульсов 4 и регистра 2 осуществляют выбор содержимого матрицы 5 элементов памяти шагов.

Матрица 5 элементов памяти шагов может представлять собой ОЗУ на ферритах, транзисторах или полупроводниковые интегральные схемы памяти на биполярных транзисторных структурах, или ПЗУ, состоящие, например, из двухвходовых ячеек И, или диодную матрицу.

Триггер 6 осуществляет переключение направления распределителя импульсов в распределителе 4 импульсов. Выход старшего разряда распределителя 4 подключен к управляющему входу триггера 6, прямой и инверсный выходы которого соединены с

первым и вторым входами направления сдвига распределителя 4 импульсов.

Выходные формирователи 7 и 8 предназначены для нормирования выходных

сигналов по длительности. Указанное нормирование необходимо, когда в качестве матрицы элементов памяти шагов используются ферриты.

Выходы выходных формирователей 7 и

8 подключены соответственно к выходу 16 шаговых приращений по ведущей координате и выходу 17 шаговых приращений по ведомой координате линейного интерполятора.

Интерполятор работает следующим образом.

В известном интерполяторе матрица элементов памяти шагов имеет 2П адресов и п разрядов, причем единицы записаны

2(2К-1)-ых адресах, где К 1, 22П 1, 1 1,

2,3(1)

Например (см.фиг.3), для пяти разрядов (п 5) и 32 адресов (2 матрица элементов имеет единичные состояния ячеек памяти:

в 1-м разряде - в 1,3,5,7,9,11,13,15,17...

адресах; во 2-м разряде-в2,6,10,14,18,22,26.30 адресах; в3-м разряде- в 4,12,20,28 адресах; в 4-м разряде - в 8 и 24 адресах; в 5-м разряде - в 16 адресе.

Указанное распределение памяти соответствует работе цифрового интегратора последовательного переноса. Для приведенной организации памяти характерно следующее: расстановка единиц в разрядах

матрицы элементов памяти, симметричных относительно ячейки памяти с адресом:

/ч Ј-

Таким образом, возможно сокращение

табличных данных матрицы элементов памяти в два раза путем записи единиц в соответствии с формулой (1) в ячейки памяти с адресами от 1 до 2 и чтения их содержимого в процессе интерполяции дважды: начиная с 1-го адреса до 2П -го в прямом направлении (соответствует чтению содержимого ячеек памяти в известном интерполяторе с адресами от 1 до ) и с адреса до 1-го - в обратном направлении

(соответствует чтению содержимого ячеек памяти в известном интерполяторе с адресами от до 2П).

Рассматриваем организацию матрицы элементов памяти на конкретном примере

(п 5).

Содержимое матрицы элементов памяти в известном интерполяторе показывает, что распределение единиц симметрично относительно адреса 16. Очевидно, что объем

матрицы можно сократить вдвое путем чтения ее ячеек 16 тактов в прямом направлении, а начиная с 16 такта - в обратном. Пусть управляющий код равен 10010, где единица слева соответствует младшему разряду управляющего кода, т.е. при таком управляю.1 $ем коде за 32 такта сформировано 9 импульсов, распределение которых на 32 тактах показано на фиг.36.

В предлагаемом интерполяторе матрица элементов памяти имеет вдвое меньший объем. Содержимое матрицы 5 элементов памяти шагов представлено на фиг.Зв. При управляющем коде 10010 за первых 16 тактовых промежутков времени считано 5 импульсов (фиг.Зг). При этом распределитель 4 импульсов в течение первых 16 тактов осуществляет распределение в прямом направлении. В 16 такте осуществляет изменение направления распределителя, что позволяет в последующих 16 тактах сформировать 4 импульса (см.фиг.Зе).

Суммарная последовательность, полученная за первые и вторые 16 тактов (фиг.Зе), не отличается от последовательности, сформированной известным интерполятором.

При появлении переднего фронта управляющего сигнала на входе 11 запуска интерполятора генератор 1 тактовых импульсов формирует на своем выходе последовательность импульсов до момента появления сигнала переполнения счетчика 3 записи кода большего приращения. Управляющий сигнал с выхода переполнения счетчика 3 поступает на вход останова генератора 1.

В предлагаемом интерполяторе шаговые приращения по ведущей координате формируются в каждом интерполяционном такте, поэтому число интерполяционных тактов равно значению большего приращения (БП), Шаговые приращения по ведомой координате формируются на выходе матрицы 5 элементов памяти шагов. При этом значение управляющего кода, хранимого в регистре 2, должно быть таким, чтобы за число тактов, равных БП, на выходе матрицы 5 элементов памяти шагов было сформировано МП-импульсов, где МП-значение меньшего приращения.

Количество импульсов В| за счет 1-го разряда управляющего кода за время БП выражается соотношением

-

БП +2

I -1

il

ц.ч

где |ц.ч - оператор выделения целой части; 1 1.

Для того, чтобы за число тактов, равных БП, на выходе матрицы элементов памяти было сформировано МП-импульсов, должно удовлетворяться соотношение 52aibj Mn,

где ai - значение цифры в i-м разряде управляющего кода.

Таким образом, задача определения управляющего кода сводится к определению

10 ai, 32an по известным значениям БП и МП

с использованием приведенных соотношений. При этом находятся значения bi и ими уравновешивается значение МП.

В предлагаемом интерполяторе осуще- 15 ствляется задание отрезка прямой значением большего приращения и значение управляющего кода.

По включении питания на вход 10 начальной установки интерполятора от внеш- 0 него устройства поступает импульс, устанавливающий управляемый генератор 1 в исходное состояние. На выходе генератора 1 импульсы не формируются.

В регистр 2 от внешнего устройства за- 5 писывается значение управляющего кода, поступающего на вход 12 управляющего кода интерполятора. Запись в регистр осуществляется нулевым уровнем, подаваемым на вход 13 записи управляющего кода интер- 0 полятора.

В счетчик 3 записывается значение БП поступаемого на вход 15. Запись БП осуществляется нулевым уровнем сигнала, подаваемым на вход 14 записи БП 5 интерполятора. Указанный сигнал поступает также на входы начальной установки распределителя 4 и триггера 6. При этом осуществляется запись единицы в младший разряд распределителя 4 и установка в ну- 0 левые состояния всех последующих его разрядов, а также установка триггера 6 в единичное состояние.

Управляемый генератор тактовых импульсов запускается передним фронтом 5 сигнала запуска, поступающего на вход 11 запуска интерполятора. На выходе генератора 1 формируется последовательность импульсов заданной частоты. Указанная последовательность тактовых импульсов по- 0 ступает на счетный вход счетчика 3, вход распределителя 4 и вход формирователя 7. При этом на выходе матрицы элементов 5 памяти шагов формируется последовательность импульсов, соответствующих мень- 5 шему приращению (по ведомой координате).

Распределитель 4 в течение 2 промежутков времени осуществляет распределение (фиг.Зб) в прямом направлении. В такте на выходе старшего разряда распределителя формируется сигнал логической единицы, обеспечивающий установку триггера 6 в нулевое состояние. Последнее, в свою очередь, изменяет направление сдвига распределителя 4. В последующих тактах осуществляется чтение ячеек матрицы 5 в обратном направлении.

С приходом каждого импульса от генератора 1 содержимое счетчика 3 записи БП уменьшается на единицу. При выдаче генератором 1 числа импульсов, равного БП, на выходе счетчика записи БП формируется сигнал переполнения, приводящий к установке генератора 1 в исходное состояние, при котором импульсы на выход генератора тактовых импульсов не выдаются.

Предлагаемый линейный интерполятор построен на элементах, входящих в состав серийно выпускаемых микросхем, серий 155,555,531.

Распределитель 4 может быть синтезирован различными способами.

Реализация матрицы 5 и формирователей 7 и 8 не отличается от их реализации в известном интерполяторе.

Управляемый генератор тактовых импульсов работает следующим образом (вариант).

В исходном состоянии триггера 20 и 21 обнулены. Это достигается в первоначальном включении подачей на второй вход элемента И 18 импульса сброса по включении питания. При появлении переднего фронта на входе 11 запуска интерполятора второй триггер переходит в состояние логической единицы, а при формировании генератором 19 переднего фронта импульса - в единичное состояние переходит и другой триггер. При этом разрешается передача импульсов на выход элемента И 22 от генератора 19. Указанные действия обеспечивают присин- хронизированное начало работы интерполятора к переднему фронту импульса от генератора 19.

В данном линейном интерполяторе объем матрицы элементов памяти шагов равен . Таким образом, достигнуто сокращение объема матрицы элементов памяти в два раза. Кроме того, уменьшена в два раза разрядность распределителя импульсов, что указывает на уменьшение аппаратных затрат.

Формула изобретения 1. Линейный интерполятор, содержащий управляемый генератор тактовых импульсов, регистр кода коэффициента, счетчик записи кода болыиего приращения, распределитель импульсов, матрицу элементов памяти шагов, первый и второй выходные формирователи импульсов, выходы

которых соединены соответственно с первым и вторым информационными выходами интерполятора, вход управляющего кода которого через регистр кода коэффициента

подключен к информационному входу матрицы элементов памяти шагов, адресный вход которой подключен к информационному выходу распределителя импульсов, информационный вход которого соединен с

0 выходом управляемого генератора тактовых импульсов, с информационными входами счетчика записи кода большего приращения и первого выходного формирователя, вход запуска устройства подключен к входу запу5 ска управляемого генератора тактовых импульсов, вход останова которого соединен с выходом переполнения счетчика записи кода большего приращения, информационный вход которого подключен к входу

0 задания большего приращения интерполятора, выход матрицы элементов памяти шагов соединен с входом второго выходного формирователя импульсов, отличающий- с я тем, что, с целью сокращения аппаратур5 ных затрат и объема постоянной памяти, в него дополнительно введен D-триггер, инверсный установочный R-вход которого соединен с входом начальной установки распределителя импульсов, входом записи

0 счетчика записи кода большего приращения и входом записи кода большего приращения интерполятора, вход начальной установки которого подключен к входу начальной установки управляемого генера5 тора тактовых импульсов, вход логической единицы которого соединен с выходом логической единицы линейного интерполятора, прямой и инверсный выходы триггера соединены соответственно с первым и вто0 рым входами направления сдвига распределителя импульсов, выход старшего разряда которого подключен к инверсному управляющему S-входу триггера, информационный D-вход которого соединен с общей шиной,

5 вход записи управляющего кода коэффициента регистра подключен к входу записи управляющего кода линейного интерполятора.

2. Интерполятор по п.1, от л ича ю щи й0 с я тем, что управляемый генератор тактовых импульсов содержит первый и второй элементы И, первый и второй D-триггеры, генератор импульсов, выход которого подключен к первому входу второго элементе И

5 и управляющему входу второго D-триггера, выход которого соединен с вторым входом второго элемента И, выход которого является выходом генератора, выход второго триггера подключен к информационному входу первого D-триггера, инверсные установочные входы второго и первого D-триггеров соединены с выходом первого элемента И, первый и второй входы которого являются соответственно входом останова генератора тактовых импульсов и входом его начальной установки, информационный вход второго триггера подключен к входу логической единицы генератора тактовых импульсов, а управляющий вход соединен с входом запуска.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой линейный интерполятор | 1989 |

|

SU1631518A1 |

| Линейный интерполятор | 1982 |

|

SU1156005A1 |

| Линейный интерполятор | 1986 |

|

SU1423984A1 |

| Линейный интерполятор | 1986 |

|

SU1413603A1 |

| Линейный интерполятор | 1987 |

|

SU1439532A1 |

| Линейный интерполятор | 1991 |

|

SU1809421A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Многокоординатный цифровой линейный интерполятор | 1987 |

|

SU1522154A1 |

| Анализатор гистограммы отклонений напряжения | 1982 |

|

SU1104530A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1709269A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах числового программного управления. Цель изобретения - сокращение аппаратурных затрат и объема постоянной памяти интерполятора. Линейный интерполятор содержит управляемый генератор тактовых импульсов, регистр кода коэффициентов, счетчик записи кода большего приращения, распределитель импульсов, матрицу элементов памяти шагов, триггер, выходные формирователи. Интерполятор имеет вход логической единицы, вход начальной установки, вход запуска, вход коэффициента наклона, входы записи, вход большего приращения, выход шаговых приращений по ведущей координате, выход - по другой координате. Отрезок прямой задается значением большего приращения и управляющего кода, запоминаемыми соответственно счетчиком большего приращения и регистром. В матрицу элементов памяти для каждого значения управляющего кода записана первая половина последовательности шаговых приращений по ведомой координате, которые симметричны относительно своего центра. При распределении импульсов распределителем импульсов в сторону старших разрядов осуществляется чтение первой половины последовательности шаговых приращений, а при распространении в сторону младших разрядов - второй. Состояние D-триггера определяет направление распределения импульсов. Число интерполяционных тактов, отсчитываемых счетчиком, равно значению большего приращения. 1 з.п. ф-лы, 4 ил. сл с

/4 15

Фиг.1

КЗ,Ч,7

фиг. 2

| Цифровой линейный интерполятор с оценочной функцией | 1981 |

|

SU991375A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Линейный интерполятор | 1982 |

|

SU1156005A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-06-30—Публикация

1989-01-02—Подача