Uy(t + f) - + r,x(t)jii:(t + с. x(t)

вj

J i( -f Г, x(t)(i

(11)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для допускового контроля амплитудно-частотной характеристики четырехполюсников | 1989 |

|

SU1608591A1 |

| Устройство для оптимального приема сигналов с угловой манипуляцией | 1988 |

|

SU1525936A1 |

| ДЕМОДУЛЯТОР ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2008 |

|

RU2393641C1 |

| Формирователь однополосного сигнала | 1985 |

|

SU1356183A1 |

| Устройство для обработки фазоманипулированного псевдослучайного сигнала | 1975 |

|

SU595869A1 |

| Квазикогерентный демодулятор сигналов манипуляции с минимальным сдвигом | 1987 |

|

SU1561214A1 |

| Адаптивный корректор многоканального сигнала с ортогональными составляющими | 1990 |

|

SU1807571A1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ СТРУКТУРНЫХ ПОМЕХ | 2010 |

|

RU2450445C2 |

| ФОРМИРОВАТЕЛЬ СИГНАЛА ТРЕУГОЛЬНОЙ ФОРМЫ | 2013 |

|

RU2536387C1 |

| Цифровое устройство селекции движущихся целей | 1984 |

|

SU1841294A1 |

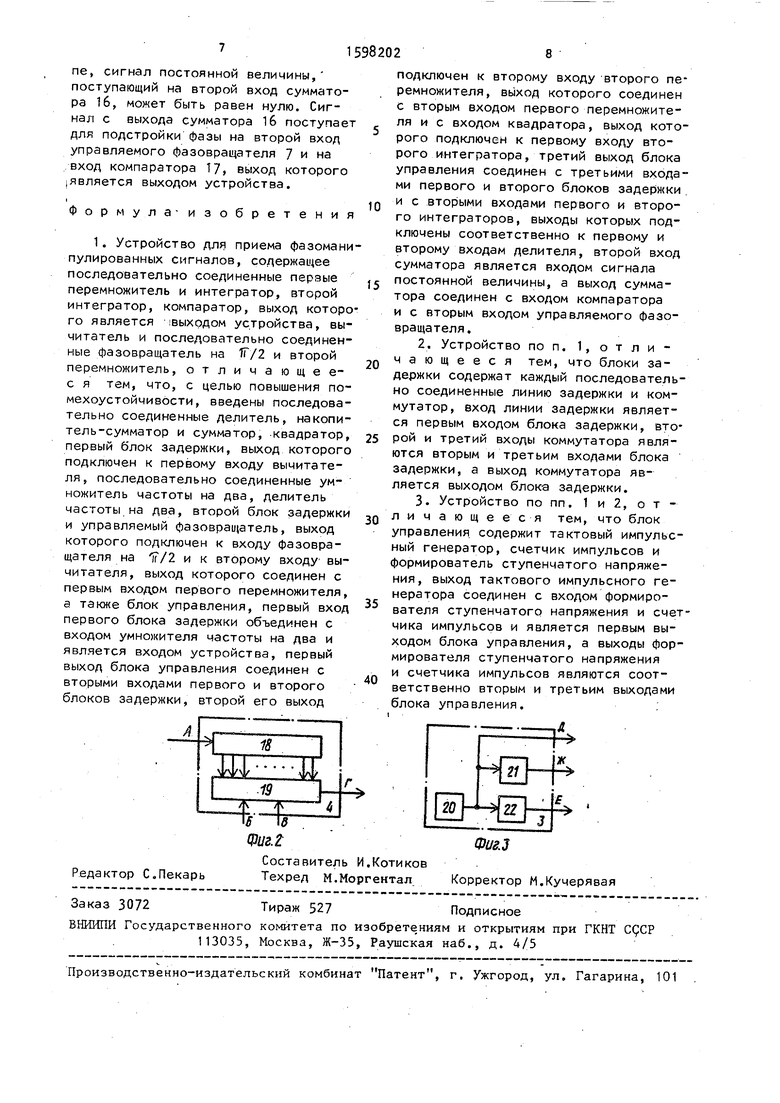

Изобретение относится к технике радиосвязи и может использоваться при построении приемников фазоманипулированных сигналов. Целью изобретения является повышение помехоустойчивости. Для достижения цели в устройство, содержащее перемножители 9, 10, интеграторы 11, 13, компаратор 17, вычитатель 6 и фазовращатель 8 на φ/2, введены умножитель 1 частоты на два, делитель 2 частоты на два, блок 3 управления, блоки 4,5 задержки, фазовращатель 7 на φ/2, квадратор 12, делитель 14, накопитель-сумматор 15, сумматор 16. 2 з.п. ф-лы, 3 ил.

Выражение (11) позволяет синтезировать структурную схему оптимального приемника. Для этого запишем принимаемый сигнал более конкретно:

y(t) t + V(t)J +n(t),(l2)

где if(t) - фаза, удовлетворяющая

условию (2) ,, тогда согласно (7)

fCt + c,x(t) 3sinC t + (f(t.)3

ax(t)

+ V(t) .

5v(t)

(13)

Таким образом, для реализации устройства необходимо иметь опорный сигнал, который формируется из принимаемого путем умножения частоты на два с последующим ее делением на два. Следовательно, на вход А первого блока поступает сигнал с манипу- лированной фазой, а на аналогичный вход второго блока 5 поступает сигнал,, у которого частота совпадает с частотой принимаемого сигнала, но манипуляция фазы отсутствует и ее значение будет постоянным.

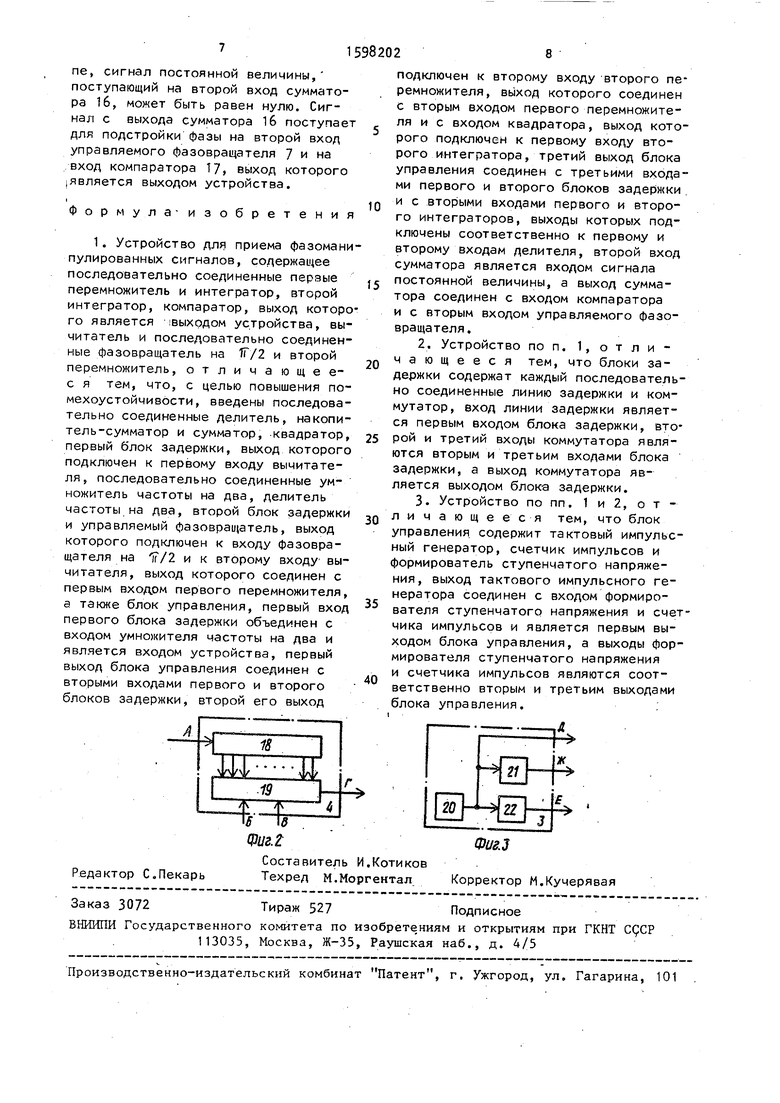

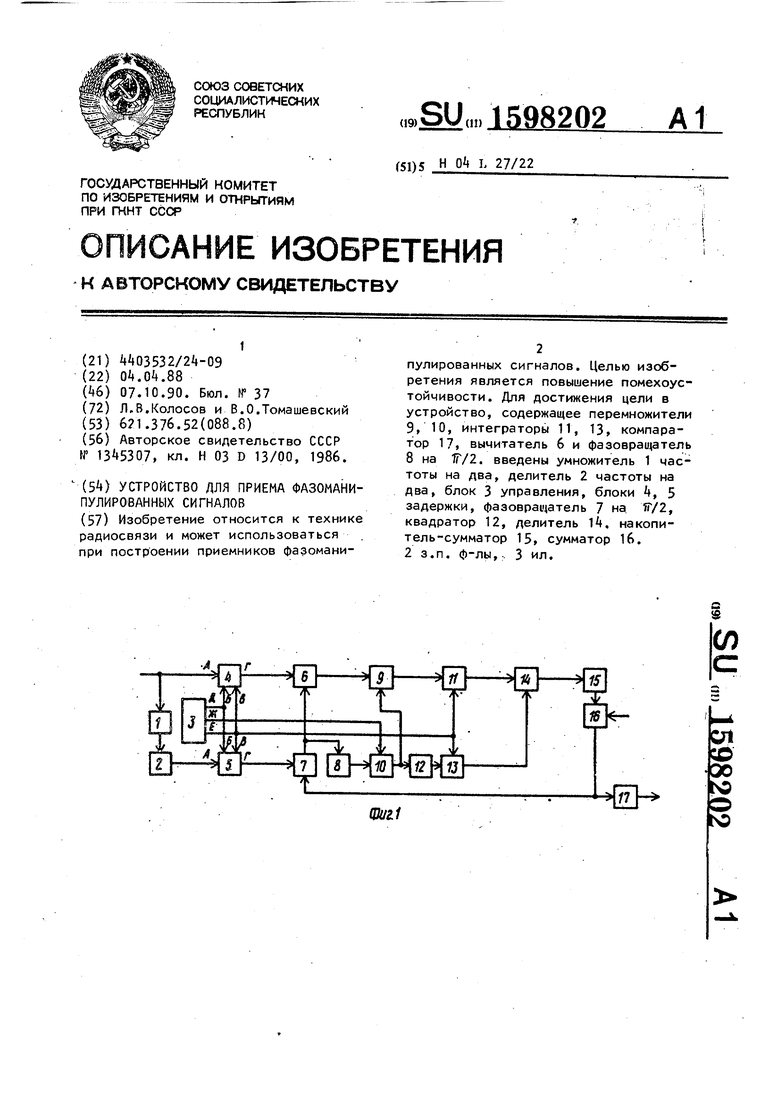

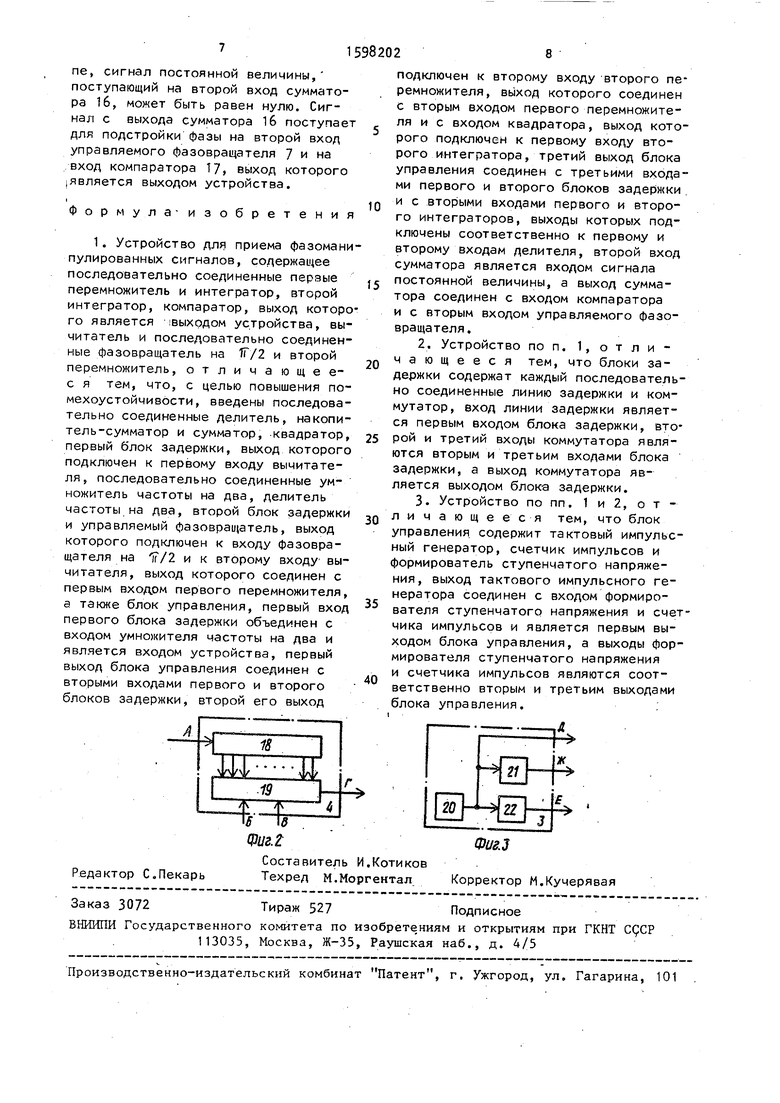

Блоки 4 и 5 управляются блоком 3, осуществляется коммутация каждым импульсом генератора 20 соответствующего отвода линии 18 на выход коммутатора 19. В блоке 3 имеется счетчик 22, который вырабатывает импульс сброса для переключения коммутатора с первого отвода на п-й отвод, т.е. сметчик 22 должен отсчитывать число импульсов генератора 20, равное чис30 3. На выходе перемножителя 10 будет сформирован сигнал

-С .q)t + f,x(t)J,

(15)

jc который поступает на квадратор 12 для формирования сигнала

.t +C,x(t)3}

(16)

40 и на второй вход перемножителя 9 где формируется сигнал

45

y(t + С) - + C,x(t) + + b,x(t)J.(17)

Сигналы (16) и (17) поступают на интеграторы 13 и 11 соответственно.

50 Таким образом будут сформированы сигналы, соответствующие знаменателю и числителю в выражении (11). На выходе делителя будет сформирована оценка ip (t) , которая накапливается

лу отводов линии 18. Сигнал с выхода накопителем-сумматором 15, формируюблока поступает на первый вход вычитателя 6, на второй вход которого подается сигнал с выхода блока 5 через управляемый фазовращатель 7. На

щим оценку непосредственно фазы Xt). Сумматор 16 служит для обеспечения начальных условий работы управ ляемого фазовращателя 7 и, в принци

выходе вычитателя 6 формируется нал

y(t + ) - fft +f,x(t)J. .(k}

Сигнал + (t)Jпоступает на фазовращатель 8, на выходе которого формируется сигнал производной по фазе (13) изменением фазы на 90°,

25 т.е. + С, x(t)J. Cигнaл( +. + ,(),x(t) поступает на перемножитель 10, на второй вход которого поступает ступенчатое напряжение, соответствующее ГеСОДЗс выхода блока

30 3. На выходе перемножителя 10 будет сформирован сигнал

-С .q)t + f,x(t)J,

(15)

jc который поступает на квадратор 12 для формирования сигнала

.t +C,x(t)3}

(16)

40 и на второй вход перемножителя 9 где формируется сигнал

45

y(t + С) - + C,x(t) + + b,x(t)J.(17)

Сигналы (16) и (17) поступают на интеграторы 13 и 11 соответственно.

50 Таким образом будут сформированы сигналы, соответствующие знаменателю и числителю в выражении (11). На выходе делителя будет сформирована оценка ip (t) , которая накапливается

накопителем-сумматором 15, формируюнакопителем-сумматором 15, формирующим оценку непосредственно фазы Xt). Сумматор 16 служит для обеспечения начальных условий работы управ ляемого фазовращателя 7 и, в принципе, сигнал постоянной величины, поступающий на второй вход сумматора 16, может быть равен нулю. Сигнал с выхода сумматора 16 поступает для подстройки фазы на второй вход управляемого фазовращателя 7 и на вход компаратора Т7, выход которого |Является выходом устройства.

I

Формула- изобретения

А

В

18

Х±±.

LZIf К

.19

I

А

ZH

If б Фиг. г

Составитель И.Котиков

Фи&З

хред М.Моргентал Корректор М.Кучерявая

Заказ 3072Тираж 527 подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ С(С 113035, Москва, Ж-35, Раушская наб., д. 4/5

0

5

0

5

0

5

0

подключен к второму входу второго перемножителя, вЫход которого соединен с вторым входом первого перемножителя и с входом квадратора, выход которого подключен к первому входу второго интегратора, третий выход блока управления соединен с третьими входами первого и второго блоков задержки и с вторыми входами первого и второго интеграторов, выходы которых подключены соответственно к первому и второму входам делителя, второй вход сумматора является входом сигнала постоянной величины, а выход сумматора соединен с входом компаратора и с вторым входом управляемого фазовращателя.

и счетчика импульсов являются соответственно вторым и третьим выходами

блока управления. I

А

ZH

Фи&З

| Авторское свидетельство СССР fJ° , кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-10-07—Публикация

1988-04-04—Подача