Изобретение относится к вычислительной технике и может быть исполь зовано в матричном накопителе для постоянного запоминающего устройства на МДП-транзисторах с различной дпи- ной канала, программируемой технологически.

Целью изобретения является повышение надежности элемента.памяти

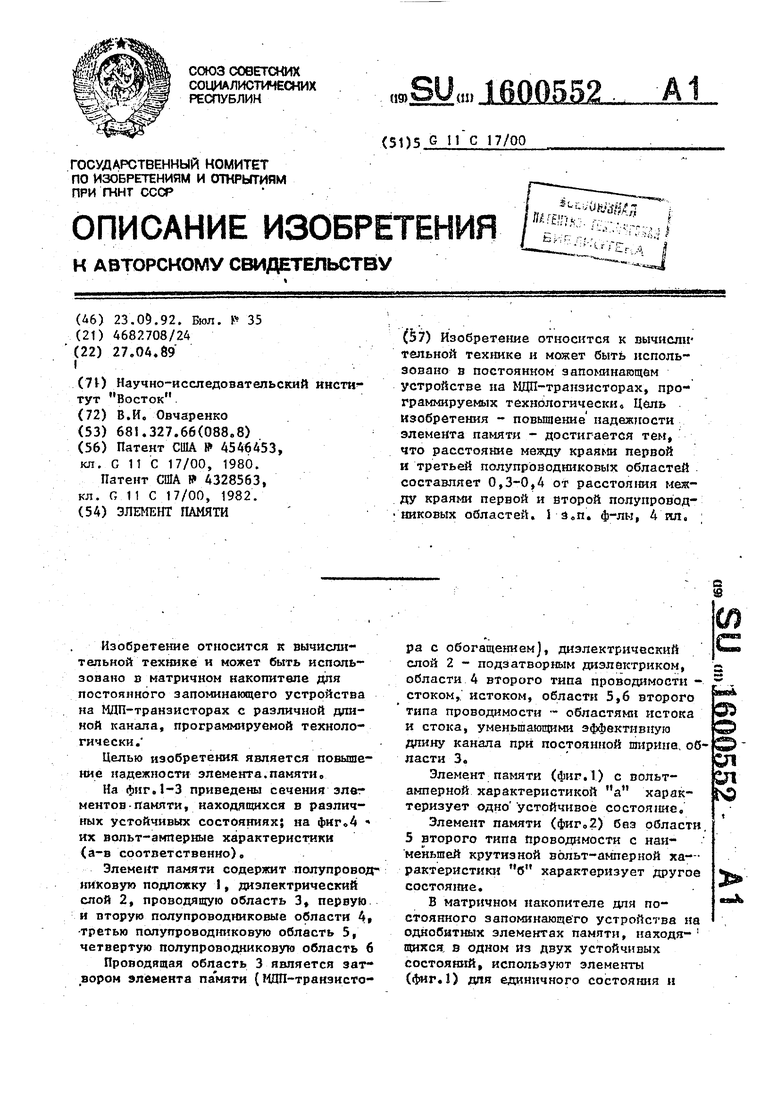

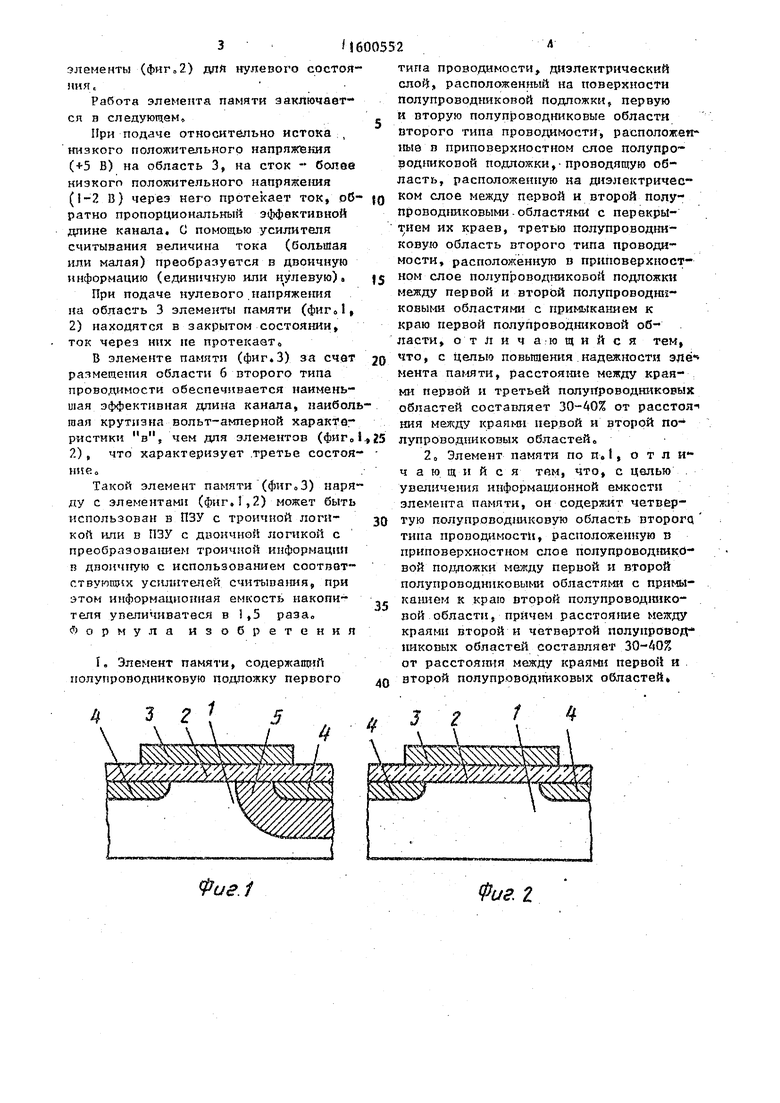

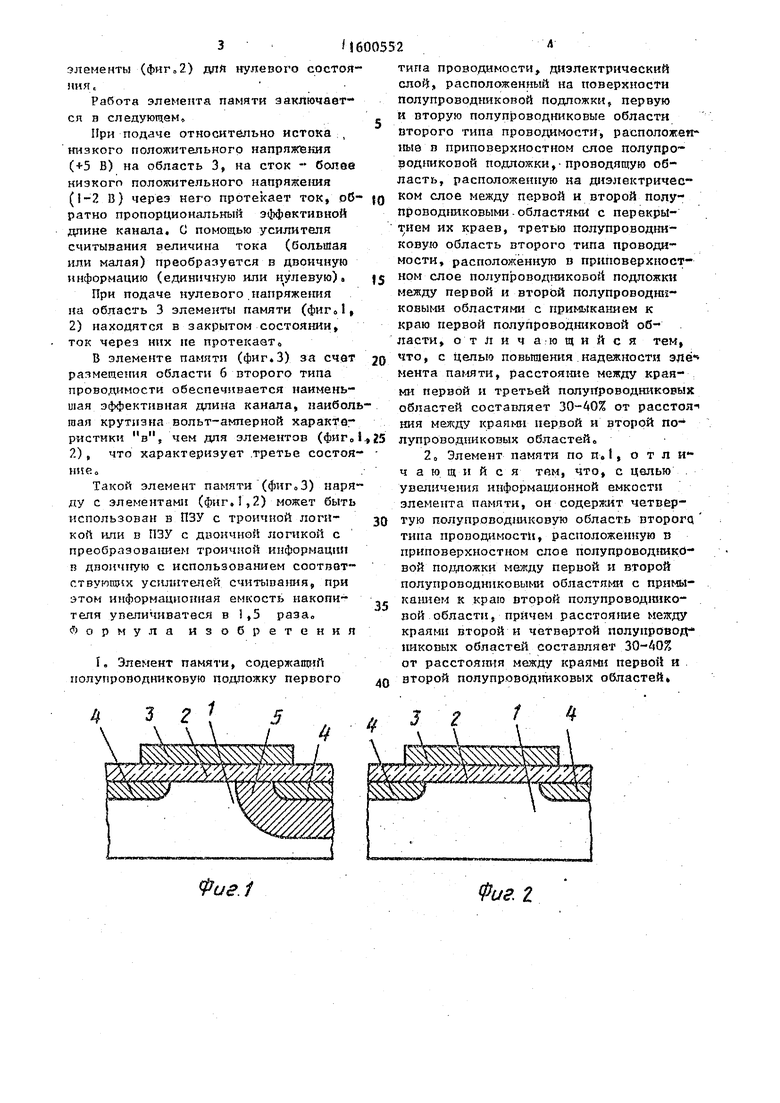

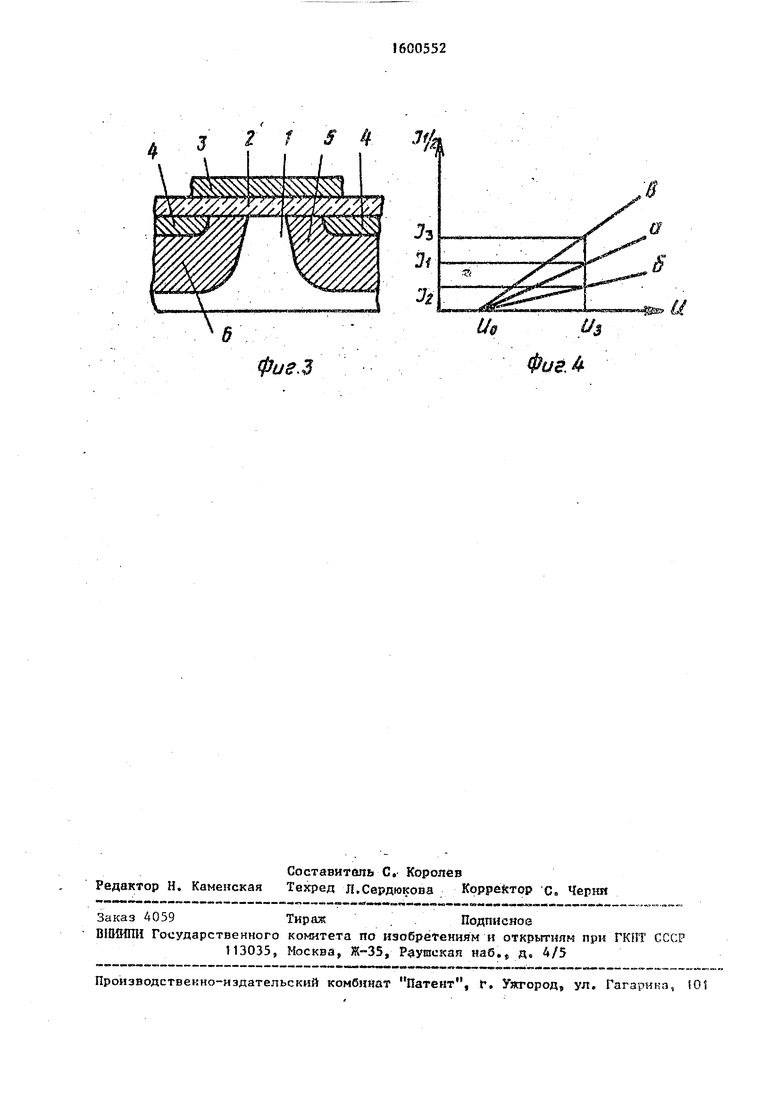

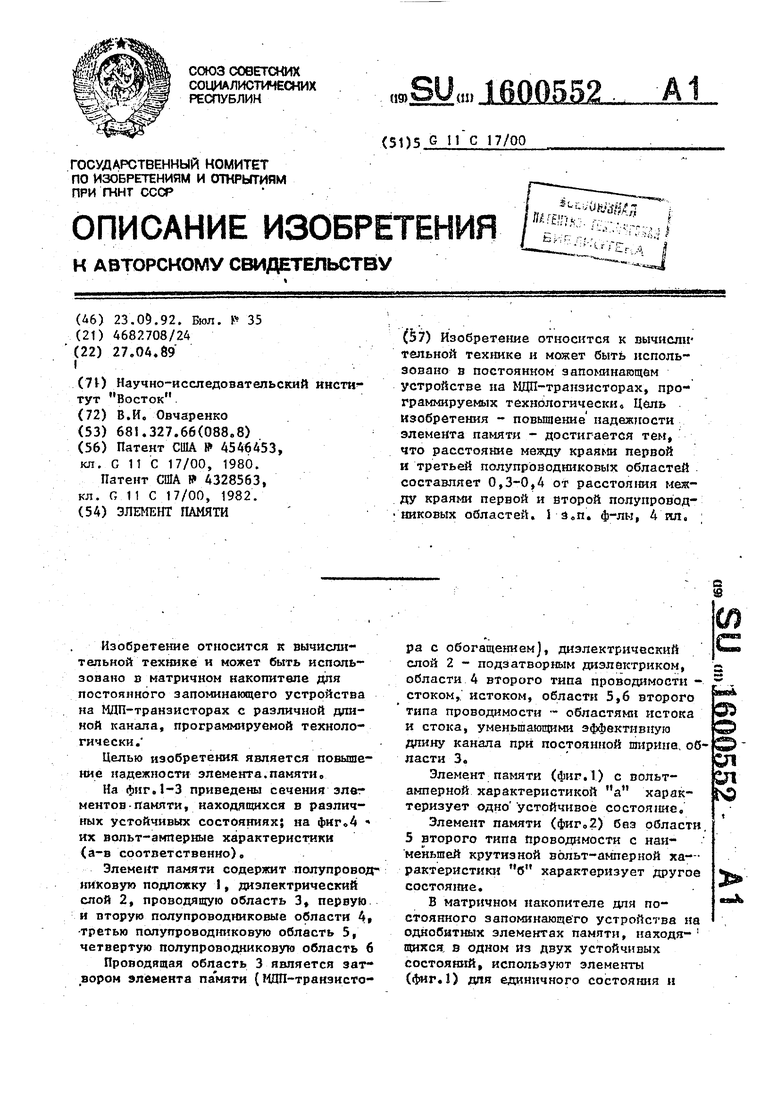

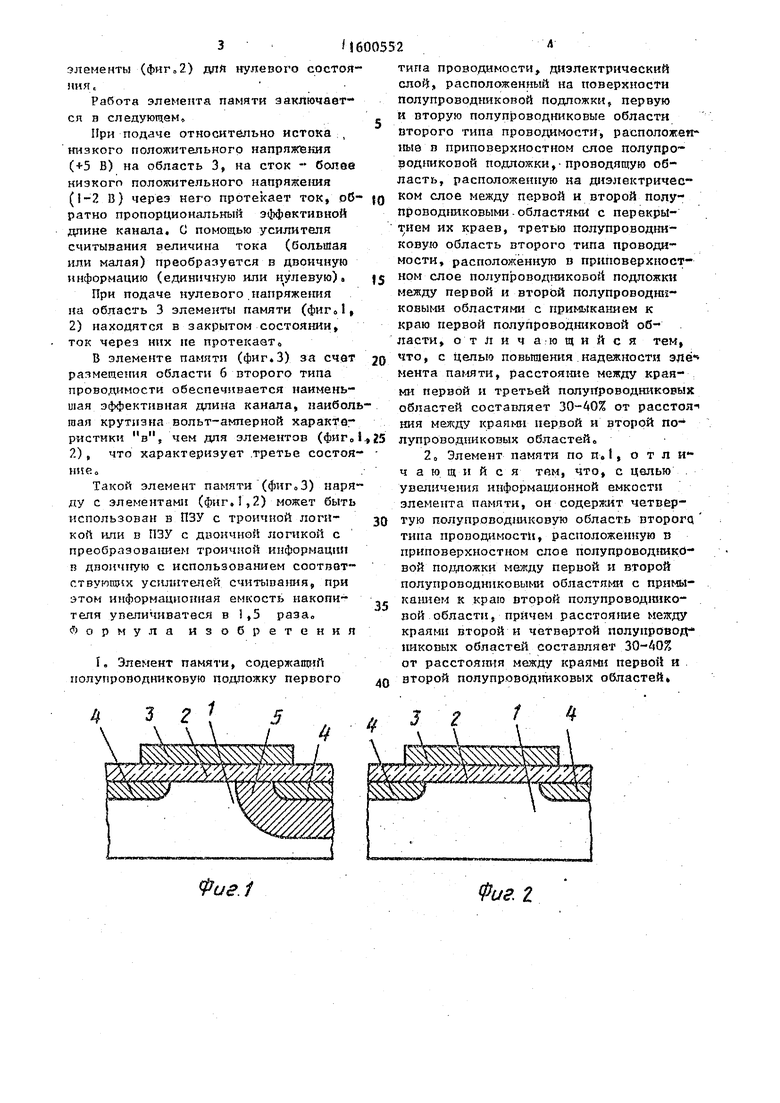

На фиг.1-3 приведены сечения элвг ментов-памяти, находящихся в различных устойчивых состояниях} на фиг«4 их вольт-амперные характеристики (а-в соответственно)в

Элемент памяти содержит полупроводниковую подложку I, диэлектрический слой 2, проводящую область 3 первую и вторую полупроводниковые области 4, третью полупроводниковую область 5, четвертую полупроводниковую область 6

Проводящая область 3 является затвором элёмеита па мяти (1 ЦШ-тракзистора с обогащением, диэлектрический слой 2 - подзатворным диэлектриком, области 4 второго типа проводимости - стоком, истоком, области 5,6 второго типа проводимости областям1г истока и стока, уменьшающими эффективную длину канала при постоянной шфипа, области 3.

Элемент памяти (фиг.1) с вольт- амперной характеристикой а характеризует одно устойчивое состояние.

Элемент памяти (фиг) без области, 5 второго типа проводимости с наименьшей крутизной вольт-амперной характеристики б характеризует другое состояние..

В матричном накопителе для постоянного запоминающе го устройства на однобитных элементах памяти, находя- щихся, в одном из двух устойчивых состояний, испольэуют элементы (фиг.1) для единичного состоягшя и

|мэ4

О5

ел

ел

ш.

3/1600

элементы (фиг,2) дпй нулевого состояния.

Работа элемента памяти заключает- сл в следующем

При подаче относительно истока , низкого положительного напряжения ( В) на область 3, на сток более низкого положительного напряжения

типа проводимости, диэлектрический cлo, расположений на поверхности полупровод шковой подложки, первую и вторую полупроводниковые области второго типа проводимости, расположен ныв в приповерхностном слое полупроводниковой подложки,-проводящую область, расположенную на диэлектричес

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный накопитель для постоянного запоминающего устройства | 1989 |

|

SU1669307A1 |

| Инвертор | 1987 |

|

SU1494214A1 |

| ЭЛЕМЕНТ ПАМЯТИ | 1992 |

|

RU2032945C1 |

| Элемент памяти и способ его изготовления | 1989 |

|

SU1767535A1 |

| ЯЧЕЙКА ПАМЯТИ СО СТРУКТУРОЙ ПРОВОДЯЩИЙ СЛОЙ-ДИЭЛЕКТРИК-ПРОВОДЯЩИЙ СЛОЙ | 2007 |

|

RU2376677C2 |

| ИНТЕГРАЛЬНЫЙ ПОЛЕВОЙ ТРАНЗИСТОР С РАЗМЕРНЫМ КВАНТОВАНИЕМ ЭНЕРГИИ | 2004 |

|

RU2257642C1 |

| Оптоэлектронный элемент памяти | 1979 |

|

SU797406A1 |

| МДП-ТРАНЗИСТОР | 1986 |

|

SU1507145A1 |

| Динамический элемент памяти | 1988 |

|

SU1571675A1 |

| ГЕТЕРОСТРУКТУРНЫЙ МОДУЛИРОВАНО-ЛЕГИРОВАННЫЙ ПОЛЕВОЙ ТРАНЗИСТОР | 2013 |

|

RU2534437C1 |

Изобретение относится к вычислительной технике и может быть использовано в постоянном 3 aпo инaroщeм устройстве на МДП-транзисторах, программируемых технологически. Цель изобретения повьпиение надежности элемента памяти - достигается тем, что расстояние между краями первой и третьей полупроводниковых областей составляет 0,3-0,4 от расстошшя между краями первой и второй полупроводниковых областей, i йвП. ф-лы, 4 ил.

(1-2 В) через него протекает ток, об- jg ° слое между первой и второй полуратно пропорциональный эффективной длине канала, С помощью усилителя считывания величина тока (большая или малая) преобразуется в двоичную информацию (единичную или и улевую) 15

При подаче нулевого напряжения на область 3 элементы памяти (фигЛ 2) находятся в закрытом состоянии, ток через них не протекает

В элементе памяти (фиг.З) за счет 20 размещения области 6 второго типа прово,димости обеспечивается наименьшая эффективная длина канала, наиболь- гаая крутизна вольт-амперной характепроводниковыми-областями с перекрытием их краев, третью полупроводниковую область второго типа проводимости, расположенную в приповерхностном слое полупроводниковой подлож5а1 между первой и второй полупроводшг- ковыми областями с примыканием к краю первой полупровод1шковой области, отличающийся тем, что, с целью повышения надежности эл мента памяти, расстояние между краями первой и третьей полулроводниковы областей составляет 30-40% от рассто ния между краями первой и второй пористики в,

чем дпя элементов (фиГо1 г5 лупроводпиковых областей.

что характеризует .третье состоя2). ни во

Такой элемент памяти (фиго 3) наряду с элементами (фиг.1,2) может быть использован в ПЗУ с троичной логикой или в ПЗУ с двоичной логикой с преобразованием троичной информации в ДВОИЧ1ГУЮ с использованием соотват- ствуюпз х усилителей считывания, при этом информационная емкость накопителя увеличиватеся в ,5 раза. Формула изобретения

I, Элемент памяти, содержащий полупроводниковую подложку первого

2о Элемент памяти по п. чающийся тем, что, увеличения информащ онной элемента памяти, он содерж

30 тую подупровод11иковую обла типа проводимости, располо приповерхностном слое полу вой подаожки между первой полупроводниковыми областя кавшем к краю второй полуп вой области, причем рассто краями второй и четвертой {шкопых областей составля от расстоя1шя между крапьш

40 второй полупроводниковых о

35

ue.f

° слое между первой и второй полупроводниковыми-областями с перекрытием их краев, третью полупроводниковую область второго типа проводимости, расположенную в приповерхностном слое полупроводниковой подлож5а1 между первой и второй полупроводшг- ковыми областями с примыканием к краю первой полупровод1шковой области, отличающийся тем, что, с целью повышения надежности эле мента памяти, расстояние между края ми первой и третьей полулроводниковых областей составляет 30-40% от расстояния между краями первой и второй по2о Элемент памяти по п.1, о т л и- чающийся тем, что, с целью увеличения информащ онной емкости элемента памяти, он содержит четвертую подупровод11иковую область второго типа проводимости, расположенную в приповерхностном слое полупроводниковой подаожки между первой и второй полупроводниковыми областями с примыкавшем к краю второй полупроводш1ко- вой области, причем расстояние между краями второй и четвертой полупровод {шкопых областей составляет 30-40% от расстоя1шя между крапьш первой я

второй полупроводниковых областей.

Фие. г

j г 1 s

шш

Тх/Т х/

7 ZjLt,

фие.Ъ

Д

ASSES ii

| Патент США № 4546453, кл | |||

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

| Патент США №4328563, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-09-23—Публикация

1989-04-27—Подача