Фиг. 5

Изобретение относится вычислительной техники и использовано в

10

15

1669307

к области может быть

постоянном запоминающем устройстве на МДИ-трянзисторах, программируемых технологически.

Целью изобретения является упрощение накопителя.

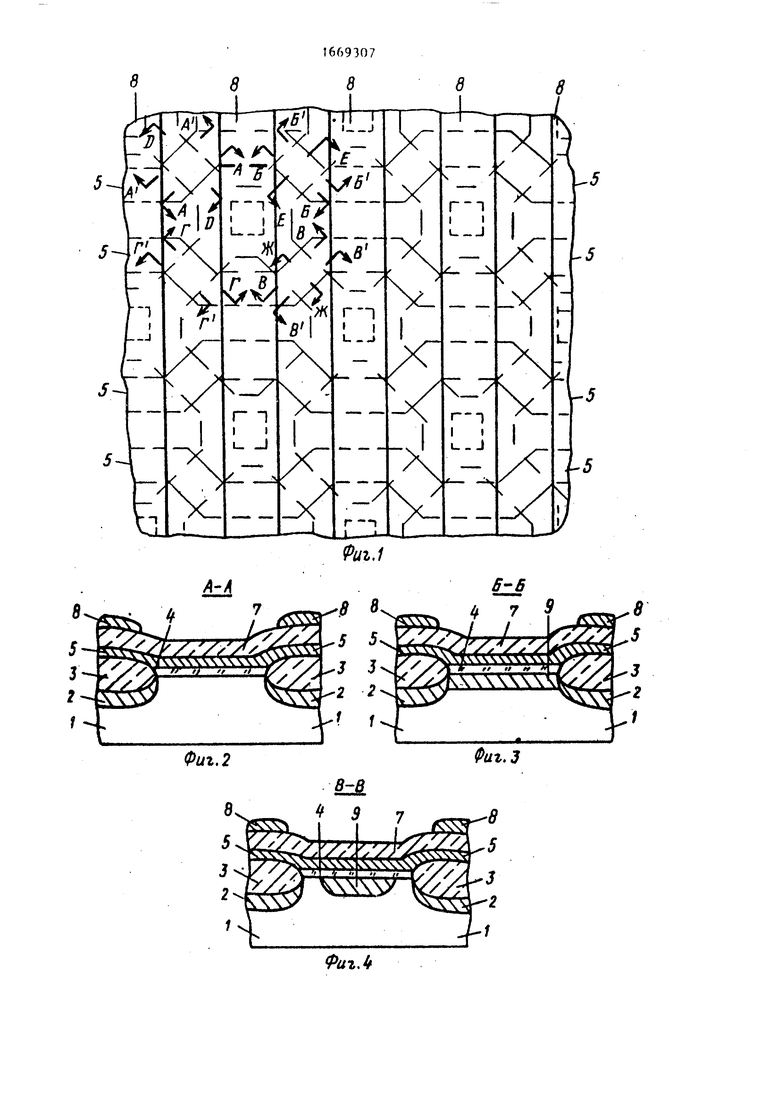

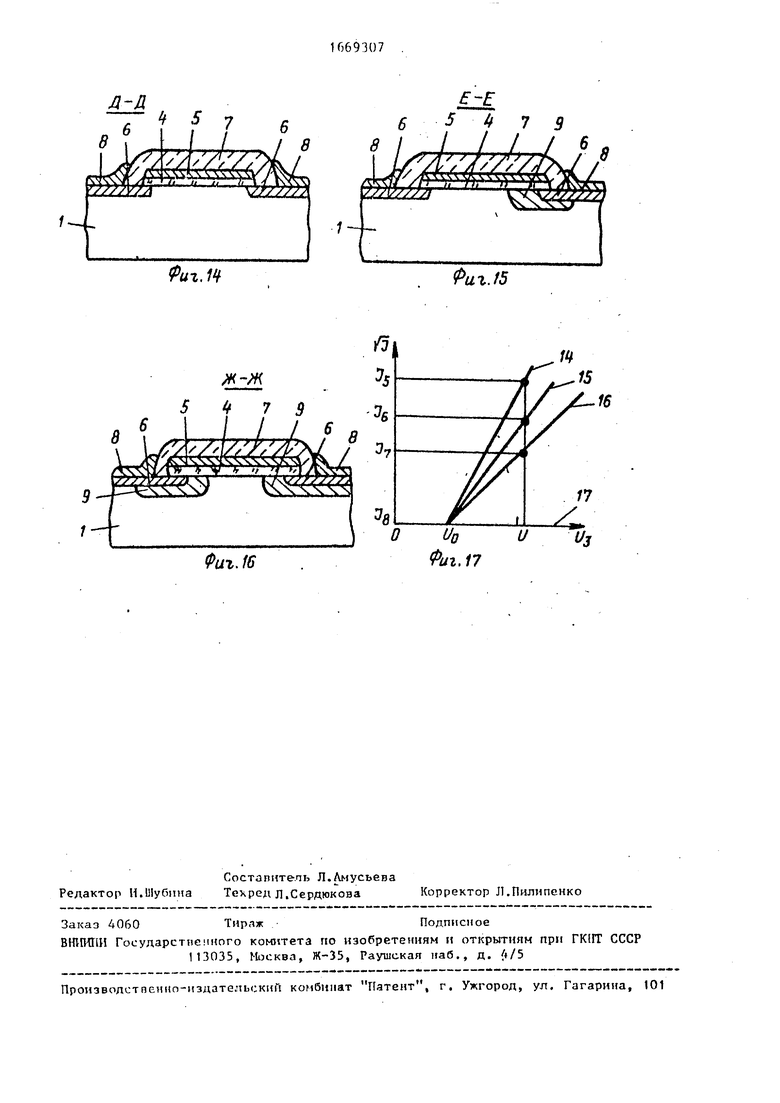

На фиг.1 приведен фрагмент матричного накопителяj на фиг.2-8 - сечения по А-А, Б-Б, В-В, Г-Г, Д-Д, Е-Е, Ж-Ж соответственно для элементов памяти, находящихся в одном из четырех устойчивых состояний; на фиг.9 приведены вольт-амперные характеристики двухбитных элементов памяти матричного накопителя; на фиг.Ю-17 - сечения и вольт-амперные характеристики четырехбитных элементов матричного накопителя.

Матричный накопитель содержит полупроводниковую подложку t первого, типа проводимости с углублениями в ней, первый диффузионный слой 2 первого типа проводимости, первый диэлектрический слой 3 ИЗ двуокиси кремния, второй диэлектрический слой

4из двуокиси кремния, адресные тины

5из поликремния, второй диффузионный слой 6 второго типа проводимости, тре тин диэлектрический слой 7 из фосфо- рб-снликатного стекла, разрядные шины 8 из металла, третий диффузионный слой 9 первого типа проводимости.

В местах пересечения адресных шин 5 и разрядных шин 8 образованы двухбитные элементы памяти матричного накопителя (фиг.1).

Адресные шины 5 являются затворами МДП-транзисторов элементов памяти этого матричного накопителя, программируемых технологически, второй диэлектрический слой 4 - их подзатвор- ным диэлектриком.

Второй диффузионный слой 6 является стоками и истоками МДП-транэйсто- ров, первый диффузионный слой 2 - аи- тилараэитньм. Первый диэлектрический слой 3 изолирует адресные шины 5 от полупроводниковой подложки 1, третий

20

25

30

35

40

пропорционален

5.

ширине адре

5, зазор нон шины

Зазор в первом диффузионном слое 2 под адресной шиной 5 определяет ш рину канала МДП-транзистора двухбит ного элемента памяти с состояниями 1,1 (отсутствие перекрытия этого зазора третьим диффузионным слоем 9

Полное перекрытие третьим диффузионным слоем 3 зазора между первым диффузиснным слоем 2 под адресной ш ной 5 предотвращает образование инверсного слоя под адресной шиной 5 (при низком считывающем напря- 7чспии) , t/то эквивалентно нулевой ши рине канала, определяющей состояния 0,0 дпухбитного элемента памяти.

Перекрытие третьим диффузионным слоем 9 10-30% или 40-70Z зазора в первом диффузионном слое 2 под адре ной тиной 5 позволяет уменьшить отн сительное значение эффективной шири канала на 0,1-0,3 и 0,4-0,7 соответ ственно для элементов памяти с состояниями 1,0 и 0,1.

Таким образом, для двухбитных эл

ментов памяти с состояниями 1,1rt;

получены следую

1, 0,1°i 0,0

щие соотношения проводимостей канал относительно нелегированного элемен та памяти с состояниями 1., 1 с мак симальной проводимостью: 1,OJ 0,70,9; о,з-о,б; о:

Работа матричного накопителя заключается в следующем.

В режиме.считывания информации н выбранную поликремниевую адресную ш ну 5 подают низкое положительное на пряжение (3-5 В), на остальные адре ные шины 5 - нулевое напряжение. На выбранные металлические разрядные ш ны 8, к которым подключены истоки МДП-транзисторов, в которых размеще или отсутствует третий диффузионный 4 слой 9„ подают нулевое напряжение, остальные разрядные шины 8 - низкое положительное напряжение.

В зависимости от перекрытия зазо ра третьим диффузионным слоем 9 чер

диэлектрический слой 7 изолирует раз- 50 выбранный элемент памяти протекает

рядные шины 8 от адресных шин 5.

Третий диффузионный слой 9 предотвращает образование инверсного слоя под адресными глинами 5. i

Длина канала МДП-транэисторов определяется эаэором между вторым диффузионньи слоем 6 под адресной тиной

I

0

5

0

5

30

35

40

пропорционален

5.

ширине адрес5, зазор нон шины

Зазор в первом диффузионном слое 2 под адресной шиной 5 определяет ширину канала МДП-транзистора двухбитного элемента памяти с состояниями 1,1 (отсутствие перекрытия этого зазора третьим диффузионным слоем 9).

Полное перекрытие третьим диффузионным слоем 3 зазора между первым диффузиснным слоем 2 под адресной шиной 5 предотвращает образование инверсного слоя под адресной шиной 5 (при низком считывающем напря- 7чспии) , t/то эквивалентно нулевой ширине канала, определяющей состояния 0,0 дпухбитного элемента памяти.

Перекрытие третьим диффузионным слоем 9 10-30% или 40-70Z зазора в первом диффузионном слое 2 под адресной тиной 5 позволяет уменьшить относительное значение эффективной ширины канала на 0,1-0,3 и 0,4-0,7 соответственно для элементов памяти с состояниями 1,0 и 0,1.

Таким образом, для двухбитных элементов памяти с состояниями 1,1rt;

получены следую 1, 0,1°i 0,0

щие соотношения проводимостей каналов относительно нелегированного элемента памяти с состояниями 1., 1 с максимальной проводимостью: 1,OJ 0,70,9; о,з-о,б; о:

Работа матричного накопителя заключается в следующем.

В режиме.считывания информации на выбранную поликремниевую адресную шину 5 подают низкое положительное напряжение (3-5 В), на остальные адресные шины 5 - нулевое напряжение. На выбранные металлические разрядные шины 8, к которым подключены истоки МДП-транзисторов, в которых размещен или отсутствует третий диффузионный 4 слой 9„ подают нулевое напряжение, на остальные разрядные шины 8 - низкое положительное напряжение.

В зависимости от перекрытия зазора третьим диффузионным слоем 9 через

50 выбранный элемент памяти протекает

ток 10-12 (фиг.9) или не протекает ток 13. Такая величина тока регистрируется усилителем считывания как соответствующие состояния 1,1, 1,0, 0,1, 0,0 двухбитного элемента памяти. ii

Через выбранные разрядные шины ток

от остальных элементов памяти не протекаст из-за нулепого напряжения нл адресных шинах 3, D результате чего КПП-транзисторы находятся закрытом состоянии

Для увеличения информационной емкости в дпа раза матричный накопител может быть выполнен на четырехбитных элементах памяти вместо двухбитных. Для этого третий диффузнойньгй слой 9 с соответствующими перекрытиями зазора между первым диффузионным слоем 2 под поликремниевой адресной шиной 5 размещен с разных сторон полнкремние- вой адресной шины 5 с большим перекрытием, чем вторым диффузионным слоем 6.

При считывании информации из таких элементов памяти величина тока определяется зазором третьего диффузионного слоя 9, находящегося в истоке выбранного КДП-транэистора. Поэтому первые два бита информации считываются при прямом включении элемента памяти, другие два бита - в инверсном включении этого же элемента памяти.

Формула изобретения 1. Матричный накопитель для постоянного запоминающего устройства, содержащий полупроводниковую подложку первого типа проводимости, в которой выполнены углубления, первый диэлектрический слой из двуокиси кремния, расположенный в углублениях в полупроводниковой подложке, первый диффузионный слой первого типа проводимости, расположенный в приповерхностном слое полупроводниковой подложки под первым диэлектрическим слоем, второй диэлектрический слой из двуокиси кремния, расположенный на поверхности полупроводниковой подложки, адресные шины из поликремния, расположенные

10

5

0

на поверхности первого и г;тгрого диэлектрических слоев, второй диффузионный слой второго типа проводимости, расположенный в приповерхностном слое полупроводниковой подложки под вторым диэлектрическим слоем с частичным перекрытием краен адресных шин, третий диэлектрический слой из фосфоросилнкатиого стекла, расположенный на поверхностях первого и второго диэлектрических слоев и адресных шин, во втором и третьем диэлектрических слоях над вторым диффузионным слоем второго типа проводимости выполнены отверстия, разрядные шины из металла, расположенные на поверхности третьего диэлектрического слоя и на поверхности полупроводниковой подложки в отверстиях во втором и третьем диэлектрических слоях, отличающийся тем, что, с целью упрощения накопителя, он содержит третий диффузионный слой первого 5 типа проводимости, расположенный в приповерхностном слое полупроводниковой подложки с примыканием к краю второго диффузионного слоя со стороны первых краев адресных шин с перекрытием 10-30%, 40-70% или 100% расстояния между соседними углублениями в полупроводниковой подложке в соответствии с хранимой информацией.

2. Накопитель по п.1, отличающийся тем, что, с целью увеличения информационной емкости, третий диффузионный слой расположен с примыканием к краю второго диффузионного слоя со стороны вторых краев адресных шин с перекрытием 10-30%, 40-70% или 100% расстояния между соседними углублениями в полупроводниковой подложке в соответствии с хранимой информацией.

0

5

0

9-9

Изобретение относится к области вычислительной техники и может быть использовано в постоянном технологически программируемом запоминающем устройстве на МДП-транзнсторах. Целью изобретения является упрощение и сокращение длительности изготовления матричного накопителя для ПЗУ. Поставленная цель достигается размещением в приповерхностном слое полупроводниковой подложки 1 под вторым диэлектрическим слоем 4 и одним краем адресной поликремниевой тины Ъ третьего диффузионного слоя 9 первого типа проводимости. Наличие слоя 9 уменьшает эффективную ширину канала запоминающего транзистора. Транзисторы с разной шириной канала соответствуют различной информации, хранимой накопителем. В результате один элемент памяти может хранить два или четыре бита информации. 1 з.п. ф-лы. 17 ил. § (Л

9

I lfy

9

.

о

г- ОчСчС

0

«- см

N Oi

ъ «м .

д -д

it 5

Фиг.Щ

8

Фиг. 16

E-Jj 5 4 7 В

I / б

Л ////1//,

S

Pu.fi

| Самоцентрирующийся лабиринтовый сальник | 1925 |

|

SU423A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Электроника, К° 6, J983, с | |||

| Приспособление для автоматической односторонней разгрузки железнодорожных платформ | 1921 |

|

SU48A1 |

Авторы

Даты

1992-09-23—Публикация

1989-07-11—Подача