у 65 VI

Фм.1

со

4

to

Изобретение относится к микроэлектронике и может быть использовано для создания полупроводниковых статических запоминающих устройств с высокой плотностью записи информации.

Цель изобретения - уменьшение площади инвертора.

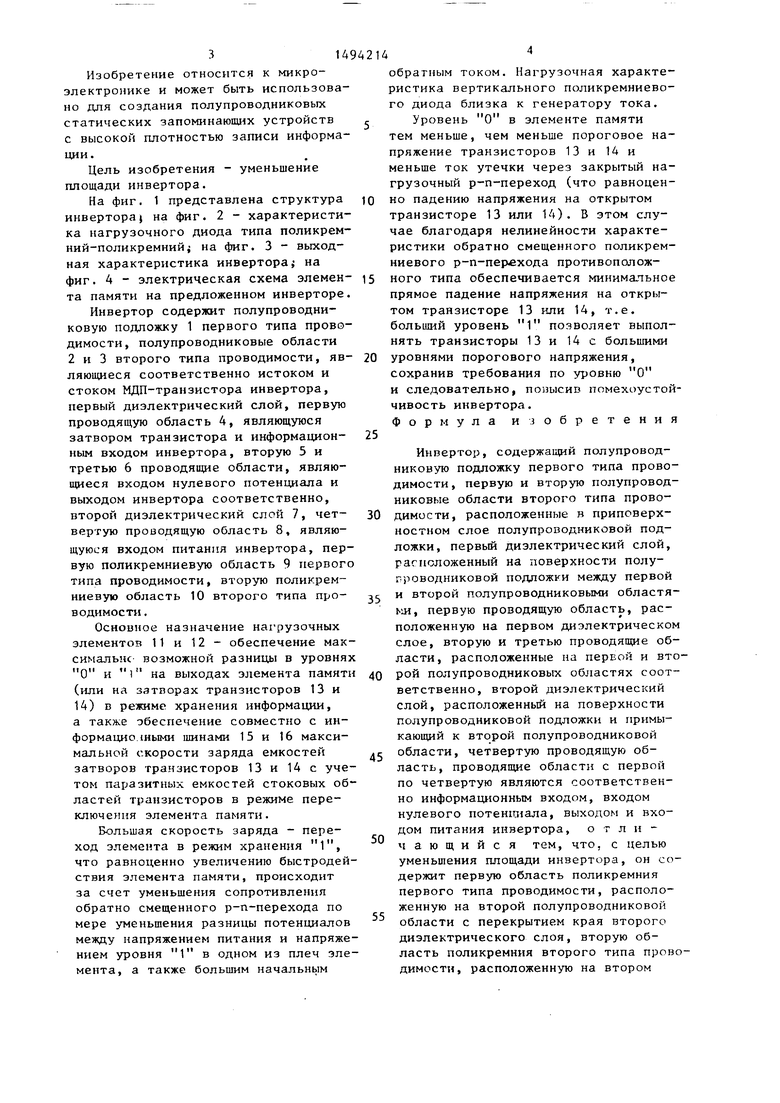

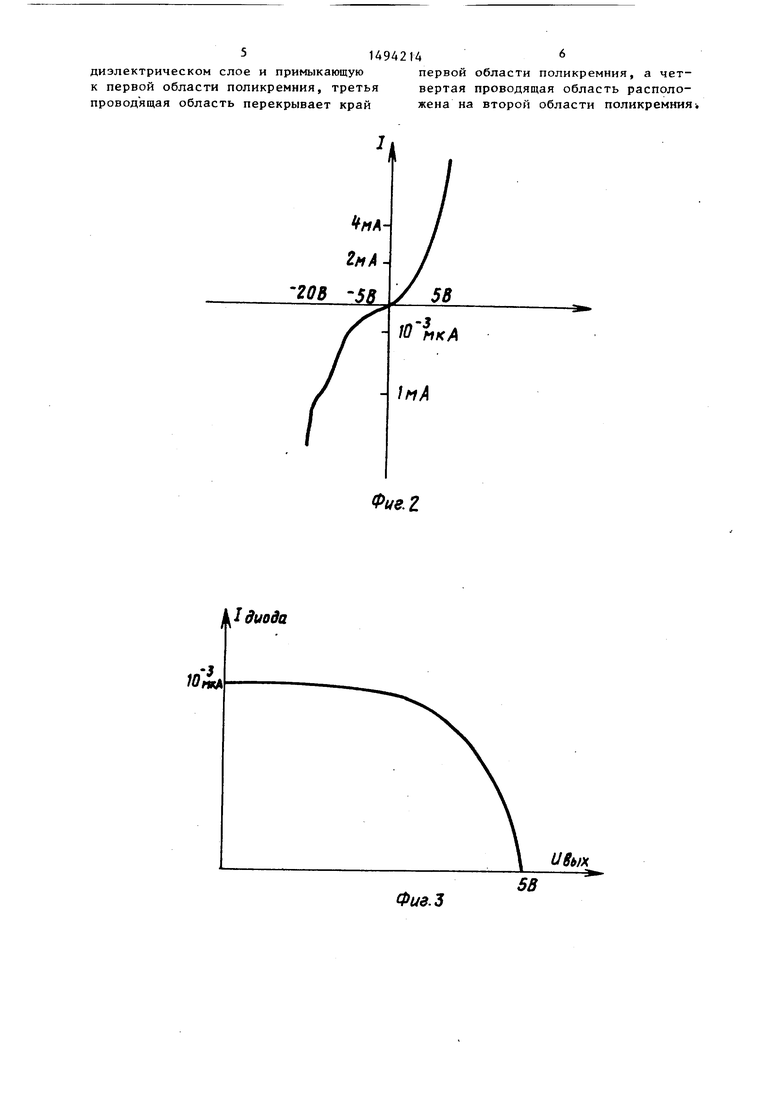

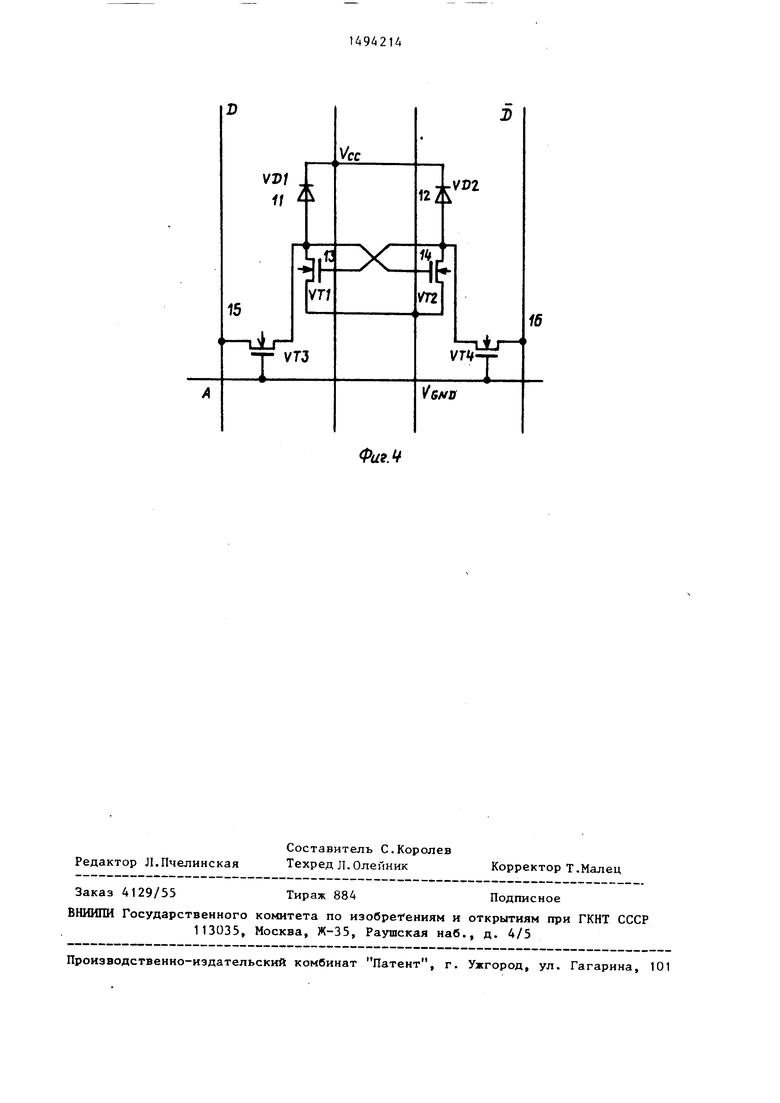

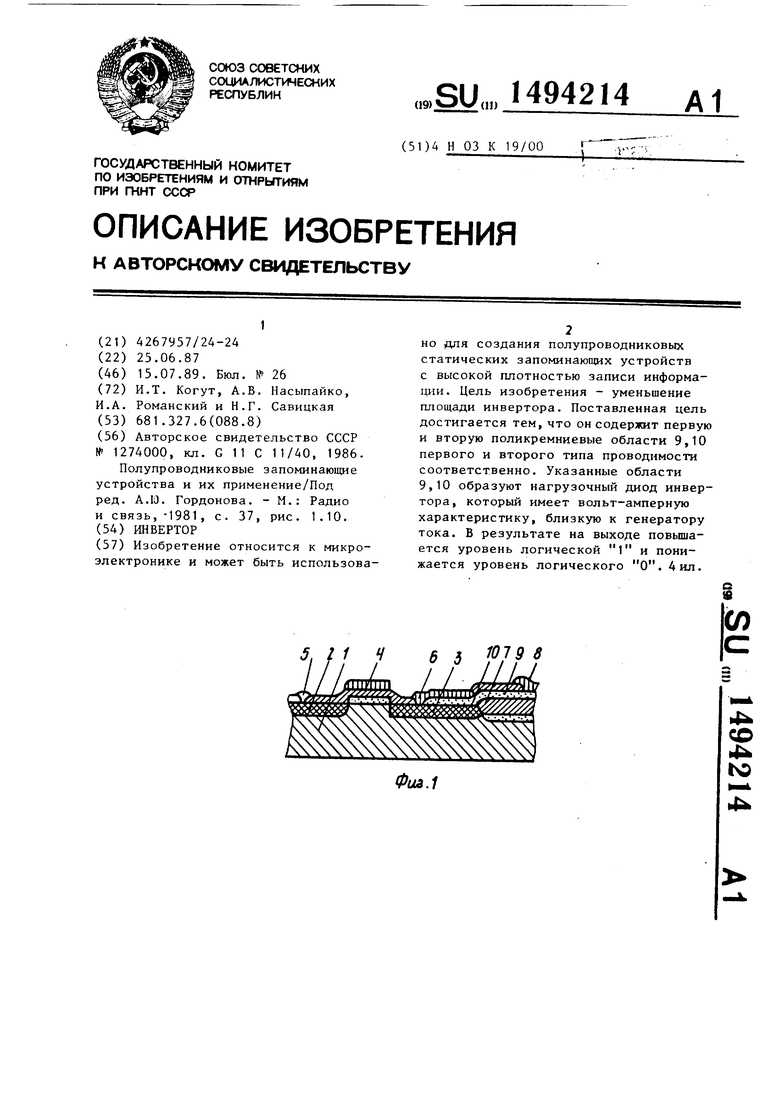

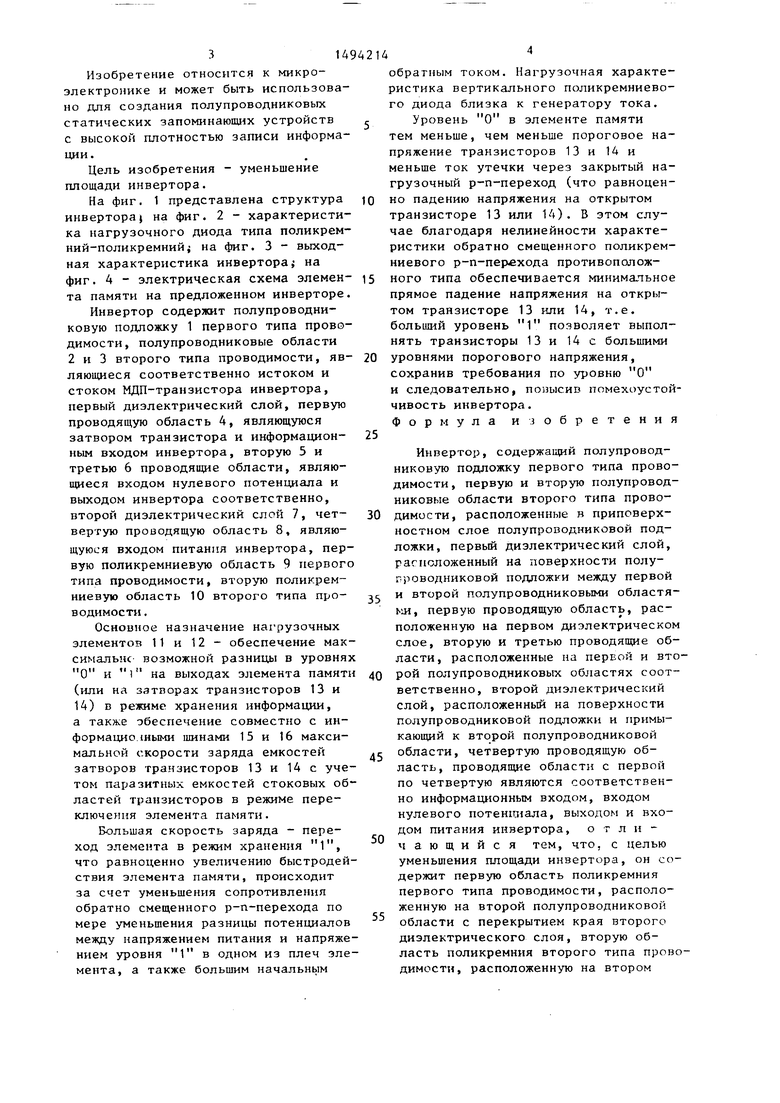

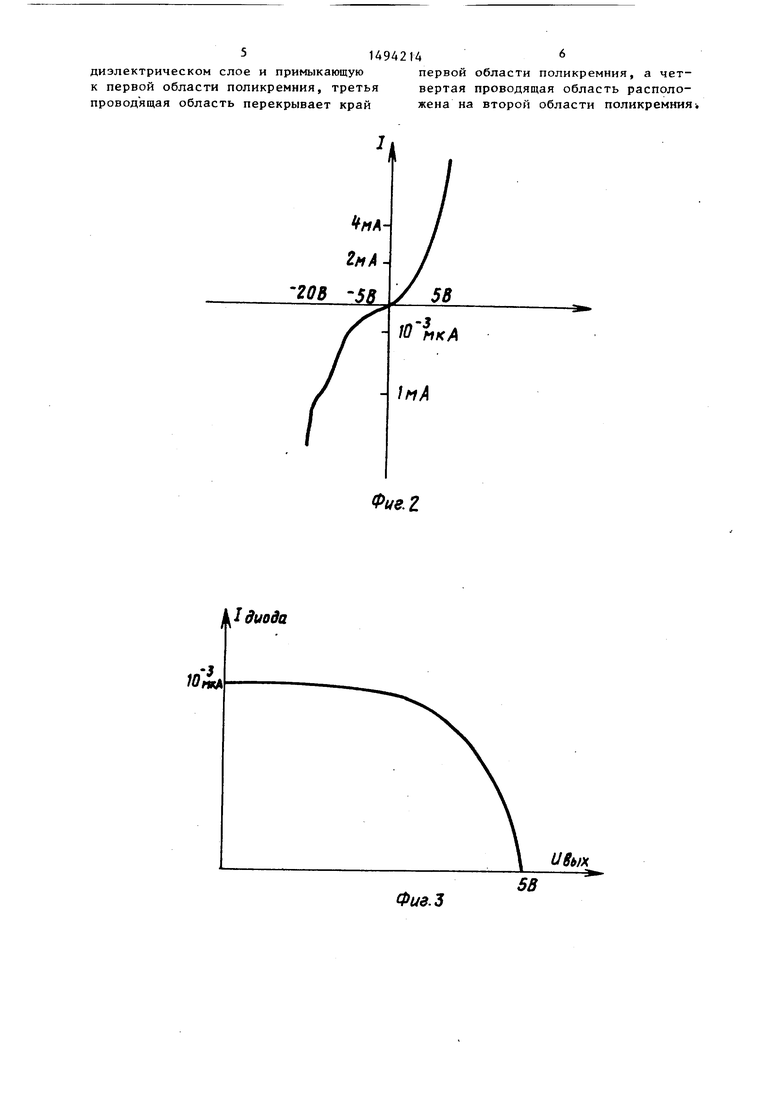

На фиг. 1 представлена структура инвертора на фиг. 2 - характеристика нагрузочного диода типа поликрем- ний-поликремнийj на фиг. 3 - выходная характеристика инвертора; на фиг. 4 - электрическая схема элемен- та памяти на предложенном инверторе.

Инвертор содержит полупроводниковую подложку 1 первого типа проводимости, полупроводниковые области 2 и 3 второго типа проводимости, являющиеся соответственно истоком и стоком МДП-транзистора инвертора, первый диэлектрический слой, первую проводящую область 4, являющуюся затвором транзистора и информационным входом инвертора, вторую 5 и третью 6 проводящие области, являющиеся входом нулевого потенциала и выходом инвертора соответственно, второй диэлектрический слой 7, четвертую проводящую область 8, являющуюся входом питания инвертора, первую поликремниевую область 9 первого типа проводимости, вторую поликремниевую область 10 второго типа проводимости.

Основное назначение нагрузочных элементов 11 и 12 - обеспечение мак- симальнс- возможной разницы в уровнях О и i на выходах элемента памяти (или на затворах транзисторов 13 и 14) в режиме хранения информации, а также обеспечение совместно с ин- формацио.шыми шинами 15 и 16 максимальной скорости заряда емкостей затворов транзисторов 13 и 14 с учетом паразитных емкостей стоковых областей транзисторов в режиме переключения элемента памяти.

Большая скорость заряда - переход элемента в режим хранения 1, что равноценно увеличению быстродействия элемента памяти, происходит за счет уменьщения сопротивления обратно смещенного р-п-перехода по мере уменьшения разницы потенциалов между напряжением питания и напряжением уровня 1 в одном из плеч элемента, а также большим начальным

0

5

5

0

5

0

5

0

5

обратным током. Нагрузочная характеристика вертикального поликремниевого диода близка к генератору тока.

Уровень О в элементе памяти тем меньше, чем меньше пороговое напряжение транзисторов 13 и 14 и меньше ток утечки через закрытый нагрузочный р-п-переход (что равноценно падению напряжения на открытом транзисторе 13 или 14). В этом случае благодаря нелинейности характеристики обратно смещенного поликремниевого р-п-пер хода противоположного типа обеспечивается минимальное прямое падение напряжения на открытом транзисторе 13 или 14, т.е. больший уровень 1 позволяет выполнять транзисторы 13 и 14 с большими уровнями порогового напряжения, сохранив требования по уровню О и следовательно, понысив помехоустойчивость инвертора. Формула изобретения

Инвертор, содержащий полупроводниковую подложку первого типа проводимости, первую и вторую полупроводниковые области второго типа проводимости, расположенные в приповерхностном слое полупроводниковой подложки, первый диэлектрический слой, parположенный на поверхности полупроводниковой подложки между первой и второй полупроводниковыми областями, первую проводящую область, расположенную на первом диэлектрическом слое, вторую и третью проводящие области, расположенные на первой и второй полупроводниковых областях соответственно, второй диэлектрический слой, расположенный на поверхности полупроводниковой подложки и примыкающий к второй полупроводниковой области, четвертую проводящую область, проводящие области с первой по четвертую являются соответственно информационным входом, входом нулевого потенциала, выходом и входом питания инвертора, отличающийся тем, что, с целью уменьшения площади инвертора, он содержит первую область поликремния первого типа проводимости, расположенную на второй полупроводниковой области с перекрытием края второго диэлектрического слоя, вторую область поликремния второго типа проводимости, расположенную на втором

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИНАМИЧЕСКАЯ ЯЧЕЙКА ПАМЯТИ | 1990 |

|

RU2029393C1 |

| ЭЛЕМЕНТ ПАМЯТИ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1989 |

|

RU1604054C |

| Элемент памяти для постоянного запоминающего устройства и способ его изготовления | 1989 |

|

SU1642888A1 |

| Элемент памяти для постоянного запоминающего устройства и способ его изготовления | 1989 |

|

SU1655242A1 |

| ВЕРТИКАЛЬНЫЙ МДП-ТРАНЗИСТОР ИНТЕГРАЛЬНОЙ СХЕМЫ | 1997 |

|

RU2108641C1 |

| ЭЛЕМЕНТ ПАМЯТИ ДЛЯ ДОЛГОВРЕМЕННОГО ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1990 |

|

RU2006965C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОНОП-ЯЧЕЙКИ ПАМЯТИ, ЯЧЕЙКА ПАМЯТИ И МАТРИЧНЫЙ НАКОПИТЕЛЬ НА ЕЕ ОСНОВЕ | 1996 |

|

RU2105383C1 |

| КОНСТРУКЦИЯ ЯЧЕЙКИ ПАМЯТИ С ВЕРТИКАЛЬНО РАСПОЛОЖЕННЫМИ ДРУГ НАД ДРУГОМ ПЕРЕСЕЧЕНИЯМИ | 1997 |

|

RU2156013C2 |

| Элемент памяти | 1980 |

|

SU881860A1 |

| ВЫСОКОВОЛЬТНЫЙ САМОСОВМЕЩЕННЫЙ ИНТЕГРАЛЬНЫЙ ДИОД | 2012 |

|

RU2492552C1 |

Изобретение относится к микроэлектронике и может быть использовано для создания полупроводниковых статических запоминающих устройств с высокой плотностью записи информации. Цель изобретения - уменьшение площади инвертора. Поставленная цель достигается тем, что он содержит первую и вторую поликремниевые области 9, 10 первого и второго типа проводимости соответственно. Указанные области 9, 10 образуют нагрузочный диод инвертора, который имеет вольт-амперную характеристику, близкую к генератору тока. В результате на выходе повышается уровень логической "1" и понижается уровень логического "0". 4 ил.

Jдиода

Фие.г

Фие.З

Фаг.

| Элемент памяти | 1984 |

|

SU1274000A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Полупроводниковые запоминающие устройства и их применение/Под ред | |||

| А.Ю | |||

| Гордонова | |||

| - М.: Радио и связь, -1981, с | |||

| Пишущая машина | 1922 |

|

SU37A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-07-15—Публикация

1987-06-25—Подача