Изобретение относится к автоматике и вычислительной технике и может быть использовано в автоматизированных устроствах управления в качестве буферного .устройства памяти.

Цель изобретения - повьш1ение быстродействия обмена информации между источником и приемником информации.

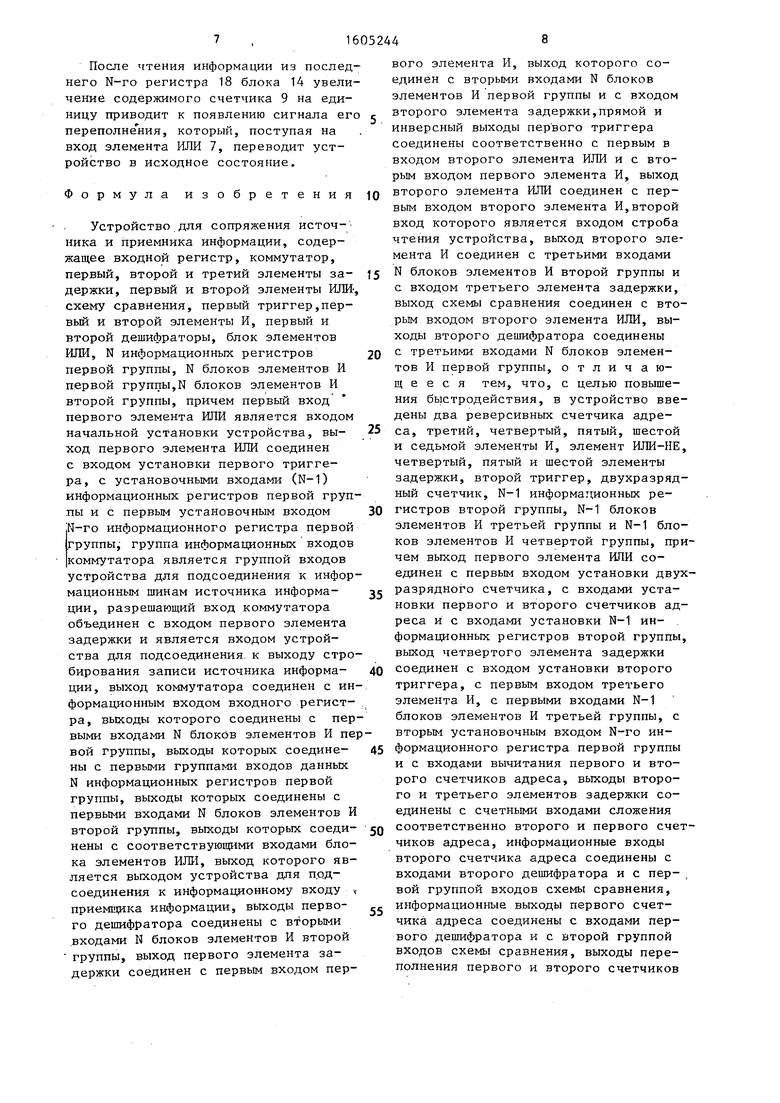

На чертеже приведена структурная схема устройства.

Устройство содержит входной регистр 1, коммутатор 2, первый элемент 3 задержки, третий элемент 4 задержки, второй элемент 5 за- . держки, второй 6 и первый 7 элементы ИЛИ, схему 8 сравнения, первый 9 и второй 10 реверсивные счетчики адреса, первый триггер 11, первый 12 и второй 13 элементы И, блок 14 памяти, содержащий второй дешифратор 15, первый дешифратор 16, блок 17 элементов ИЛИ, N информационных регистров 18 первой группы, N блоков 19

элементов И первой группы, N блоков 20 элементов И второй группы. Устройство также содержит третий элемент И 21, четвертый элемент И 22, пятый элемент И 23, шестой элемвйт И 24, седьмой элемент И 25, элемент ИЛИ-FIE 26, четвертый элемент 27 задержки, пятый элемент 28 задержки, шестой элемент 29 задержки, второй триггер 30. двухразрядный счетчик 31,. В блоке 14 памяти сдвиг информации производится с помощью (N-1) информационных регистров 32 второй группы, (N-I) блоков 33 элементов И четвертой группы, (N-1) блоков 34 элементов И третьей группы.

Кроме того, на схеме обозначены: информационный вход 35 устройства, вход 36 стробирования записи устройства, вход 37 стробирования чтения устройства, вход Началььгая установка 38 устройства, информационный выход 39 устройства, выход 40 готов(Л

О5

ности записи, выход 41 устройства готовности чтения, вход Синхронизация А2 устройства.

Устройство работает следующим образом.

Код, установленный на счетчике 10, определяет адрес регистра 18 блока 14, в который записывается информация при очередном обращении к устройству в режиме записи. Выбор i-ro регистра 18 блока 14 в этом режиме производится разрешающим потенциалом на i-M выходе дешифратора 15.

Код, установленный на счетчике 9, определяет адрес регистра 18 блока 14, из которого считывается информация при очередном обращении к устройству в режиме чтения. Выбор i-ro регистра 18 блока 14 в этом режиме производится разрешающим потенциалом на i-M выходе дешифратора 16.

Запись (чтение) информации в i-й регистр 18 блока 14 производится последовательно, в порядке возрастания адресов регистров 18 блока 14. При этом после записи (чтения) в i-й регистр 18 блока 14 к содержимому счетчика 10 (9) добавляется единица и, таким образом, устанавливается код, соответствующий адресу (i+1)-ro регистра 18 блока 14,

Запросы на запись и чтение информации поступают в устройство асинхро но, поэтому в процессе работы устройства обеспечивается чтение информации только из тех регистров 18 блока 14, в которые была произведена запись. Это достигается при выполнении условия непревьшения содержимьм счетчика 9 содержимого счетчика 10. Если содержимое счетчика 9 стало равным содержимому счетчика 10, то на выходе несравнения схемы 8 сравнения устанавливается нулевой уровень, который через элемент ИЛИ 6 поступает на элемент И 13 и через элемент И 24 на выход 41 устройства и запрещает чтение информации , Чтение информации становится возможным после увеличения содержимого счетчика 10, т.е„ после следующей записи в устройство .

При записи информации во все N регистров 18 блока 14 и отсутствии сигналов чтения счетчик 10 оказывается обнуленным при переполнении по- .сле записи информации в N-й регистр 18 блока 14, В этом случае сигнал.

5

0

5

0

5

0

5

0

5

разрешающий чтение информации из устройства, вырабатывается при появлении сигнала переполнения счетчика 10, который переводит в единичное состояние триггер 11. Единичный потенциал на прямом выходе триггера поступает через элемент ИЛИ 6 и элемент И 24 на выход 41 устройства и разрешает прохождение управляющего сигнала чтения.

Сброс триггера 11 в исходное состояние производится после чтения- информации из последнего регистра 18 блока 14. При этом вырабатывается сигнал переполнения счетчика 9, который, поступая на элемент ИЛИ 7, производит действия, аналогичные сигналу начальной установки.

Запись в устройство блокируется с момента переполнения счетчика 10 до момента переполнения счетчика 9 (т.е., между записью в последний N-й регистр 18 и чтением информации из него). Для снижения потерь времени, связанных.с этой блокировкой, в устройстве осуществляется сдвиг информации, содержащейся в N регистрах 18 блока 14, в направлении регистров 18 блока 14 с меньшими адресами после чтения информации из последних. Сдвиг информации производится с использованием регистров 32 блока 14 при отсутствии запросов на чтение и запись в устройство, В режиме сдвига устанавливается в единичное состояние триггер 30, что приводит к запреще- . нию чтения и записи в устройство на время сдвига и к запуску счетчика 31, управляющего процессом сдвига.

При завершении двух тактов сдвига ( такт - запись информации из i-ro регистра 18 блока 14 в (i-1)-й регистр 32 блока 14 (i 1,N), 2-й такт - запись информации из j-го регистра 32 блока 14 в j-и регистр 18 блока 14, 3 1 N-1) из содержимого счетчиков 9 и 10.вычитается единица и сбрасывается триггер 30. Операция сдвига повторяется до момента появления высокого потенциала на первом выходе дешифратора 16, что свидетельствует о выборе для чтения первого регистра 18 блока 14 и, следовательно, об отсутствии регистров 18 блока 14, из которых уже была считана информация.

При частом во времени следовании запросов на чтение и запись инфорнацин в устройство и, следовательно,

прн затруднении проведения сдвига информации возможно переполнение счечика 10, В этом случае проведение сдвигов блокируется до момента сброса триггера 11.

Перед началом работы с помощью импульсного сигнала на входе 38 начальной установки устройства производитс сброс двухразрядного счетчика, счетчиков 9 и 10, регистров 18 или 32 блока 14 и установка в исходное состояние триггера 11, что формирует на выходе 40 устройства готовность записи. При сбросе в счетчики 9 и 10 заносятся нулевые коды и вследствие равенства содержимого этих счетчков устанавливается нулевой уровень на выходе несравнения схемы 8 сравнения, который приводит к запрету чтения информации из устройства.

При вводе информации управляющий сигнал записи подается на вход 36 устройства и разрешает прохождение информации с входа 35 устройства через коммутатор 2 в регистр 1 данных, С регистра 1 информационный сигнал поступает на вход блоков 19 элементов И, Кроме того, сигнал записи после задержки на элементе 3 задержки на входе элемента И 12 поступает с выхода этого элемента на вход блоков 19 элементов И. Запись информации в соответствующий регистр 18 блока 14 производится при наличии разрешающего сигнала на соответствующем выходе дешифратора 15, После задержки на элементе 5 задержки на время записи информации в регистр 18 сигнал записи увеличивает содержимое счетчика 10 на единицу, вследствие чего с помощью дешифратора 15 может быть выбран следующий регистр 18 блока 14,

Увеличение содержимого счетчика 10. в процессе записи информации приводит к появлению единичного уровня на выходе несравнения схемы 8 сравнения, который через элемент ИЛИ поступает на элементы И 13 и разрешает прохождение управляющего сигнала чтения на входы элементов И блоков 20,

Чтение информации производится при поступлении на вход 37 устройства управляющего сигнала чтения. При этом чтение осуществляется последовательно из регистров 18 блока 14, Информационный сигнал с регистра 18 через блок 17 элементов ИЛИ поступает на ин6052446

формационный выход 39 устройства. Кроме того, управляющий сигнал чтения после задержки на элементе 4 задержки на время чтения из регистра 18 увели чивает содержимое счетчика 9 на единицу, вследствие чего с помощью дешифратора 16 выбирается для чтения следующий регистр 18,

Q Сдвиг информации производится следующим образом. При отсутствии управляющих сигналов записи и чтения, высоких потенциалов на прямом выходе триггера 11 и первом выходе де15 шифратора 16 на выходе элемента ИЛИ-НЕ 26 появляется высокий потенциал, который через элемент И 24, предназначенный для исключения запрещенных комбинаций на входе триггера 30, посту20 пает на единичный вход триггера 30, По приходу синхроимпульса триггер 30 перебрасывается в единичное состояние (фиг,2), что приводит к сбросу готовности записи и чтения на вы25 -ходах 40 и 41 устройства и к разре- щению прохождения задержанных на время перебрасывания триггера 30 синхроимпульсов на счетный вход счетчика 31 ,

30 При установке в единичное состояние первого разряда счетчика 31 производится запись информации из i-ro регистра 18 в (1-1)-й регистр 32 (i 1,N), а при установлении в единичное состояние второго разряда счетчика 31 - запись из j-ro ре- гистра 32 в j-и регистр 18 (j 1,(N-1)), Последний N-й регистр 18

35

при этом обнуляется.

Элементы 27 и 29 задержки, задерживающие сигналы на одинаковое время, предназначены для обеспечения сброса счетчика 31 и триггера 30 следующим синхроимпульсом после синхроимпульса, по которому бьш установлен в единичное состояние второй разряд счетчика 31, Сброс триггера 30 приводит к восстановлению готовности записи и чтения на выходах 40 и 41 устройства.

Если запись информации в последний N-й регистр 18 произведена, то это приводит к переполнению счетчика 10, Сигнал переполнения этого счетчика устанавливает в единичное состояние триггер 11, что приводит к сбросу готовности записи на выходе 40 устройства и к запрету проведения сдвигов.

После чтения информации из последнего N-ro регистра 18 блока 14 увеличение содержимого счетчика 9 на единицу приводит к появлению сигнала его переполне ния, который, поступая на вход элемента ИЛИ 7, переводит устройство в исходное состояние.

Формула изобретения

Устройство для сопряжения источ-- ника и приемника информации, содержащее входной регистр, коммутатор, первый, второй и третий элементы за- держки, первый и второй элементы ИЛИсхему сравнения, первый триггер,первый и второй элементы И, первый и второй дешифраторы, блок элементов ИЛИ, N информационных регистров первой группы, N блоков элементов И перв.ой группы,N блоков элементов И второй группы, причем первый вход первого элемента ИЛИ является входом начальной установки устройства, вы- ход первого элемента ИЛИ соединен с входом установки первого триггера, с установочными входами (N-1) информационных регистров первой группы и с первым установочным входом Н-го информационного регистра первой группы, группа информационных входов коммутатора является группой входов устройства для подсоединения к информационным шинам источника информа- ции, разрешающий вход коммутатора объединен с входом первого элемента задержки и является входом устройства для подсоединения к выходу стро бирования записи источника информа- ции, выход коммутатора соединен с информационным входом входного регистра, выходы которого соединены с первыми входами N блоков элементов И певой группы, выходы которых соедине- ны с первыми группами входов данных N информационных регистров первой группы, выходы которых соединены с первыми входами N блоков элементов И второй группы, выходы которых соеди- нены с соответствующими входами блока элементов ИЛИ, выход которого является выходом устройства для п.од- соединения к информационному входу приемш 1ка информации, выходы перво- го дешифратора соединены с вторыми входами N блоков элементов И второй группы, выход первого элемента задержки соединен с первым входом первого элемента И, выход которого соединен с вторыми входами N блоков элементов И первой группы и с входом второго элемента задержки,прямой и инверсный выходы первого триггера соединены соответственно с первым в входом второго элемента ИЛИ и с вторым входом первого элемента И, выход второго элемента ИЛИ соединен с первым входом второго элемента И,второй вход которого является входом строба чтения устройства, выход второго элемента И соединен с третьими входами N блоков элементов И второй группы и с входом третьего элемента задержки, выход схемы сравнения соединен с вторым входом второго элемента ИЛИ, выходы второго дешифратора соединены с третьими входами N блоков элементов И первой группы, о т л и ч а ю- щ е е с я тем, что, с целью повышения быстродействия, в устройство введены два реверсивных счетчика адреса, третий, четвертый, пятый, шестой и седьмой элементы И, элемент ИЛИ-НЕ четвертый, пятый и шестой элементы задержки, второй триггер, двухразрядный счетчик, N-1 информационных регистров второй группы, N-1 блоков элементов И третьей группы и N-1 блоков элементов И четвертой группы, прчем выход первого элемента ИЛИ соединен с первым входом установки двуразрядного счетчика, с входами установки первого и второго счетчиков адреса и с входами установки N-1 информационных регистров второй группы выход четвертого элемента задержки соединен с входом установки второго триггера, с первым входом третьего элемента И, с первыми входами N-1 блоков элементов И третьей группы, с вторьм установочным входом N-ro информационного регистра первой группы и с входами вычитания первого и второго счетчиков адреса, выходы второго и третьего элементов задержки соединены с счетными входами сложения соответственно второго и первого счечиков адреса, информационные входы второго счетчика адреса соединены с входами второго дешифратора и с первой группой входов схемы сравнения, информационные выходы первого счетчика адреса соединены с входами первого дешифратора и с второй группой входов схемы сравнения, выходы переполнения первого и второго счетчиков

адреса соединены соответственно с вторым входом первого элемента ИЛИ и с входом сброса первого триггера, инверсный йыход первого триггера соединен с первым входом четвертого элемента И, объединенного с вторкм входом первого элемента И,выход четвертого элемента И является выходом готовности записи устройства, вход первого элемента задержки объединен с первым входом элемента ИЛИ-НЕ, выход которого соединен с первым входом пятого элемента И, выход которого соединен с входом сброса второго триггера, инверсный выход которого соединен с вторым входом четвертого элемента И, с первым входом шестого элемента И, выход которого является выходом готовности чтения устройства, выход второго элемента ИЛИ соединен с вторым входом шестого элемента И, второй вход второго элемента И соединен с вторым входом элемента ИЛИ-НЕ, прямой выход первого триггера соединен с третьим входом элемента ИЛИ-НЕ, первый выход первого дешифратора соединен с четвертым входом элемента ШШ-НЕ, синхр обход второго триггера является синхровхо- дом устройства и соединен с входом пятого элемента задержки и с вторым входом третьего элемента И, выход которого соединен с вторым входом установки двухразрядного счетчика, прямой выход второго триггера соединен с первым входом седьмого элемента И, выход которого соединен с счетным входом двухразрядного счетчика, прямой выход первого р азряда которого соединен с первым входом N-1 бл-э- ков элементов И четвертой группы,

0 прямой и инверсный выходы второго разряда двухразрядного счетчика соединены соответственно с входом четвертого элемента задержки и с входом шестого элемента задержки, выход ко5 торого соединен с вторым входом пятого элемента И, выход пятого элемента задержки соединен с вторым входом седьмого элемента И, выходы N-1 блоков элементов И четвертой группы

0 соединены с входами данных N-1 информационных регистров второй группы, выходы которых соединены с вторыми входами N-1 блоков элементов И третьей группы, вторая группа входов

5 данных i-ro информационного регистра первой группы, где i 1...(N-1) соединена- с информационными выходами i-ro блока элементов И третьей группы, где i 1...N-1, вторые входы

0 блока элементов И четвертой группы, где j 1.,.N-1, соединены с второй группой выходов данных (j+1)-ro информационного регистра первой группы.

0 -О

JO о

35

oJ8

33

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство буферной памяти | 1988 |

|

SU1596390A1 |

| Устройство для сопряжения ЦВМ с внешними устройствами | 1989 |

|

SU1784840A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Устройство для сопряжения разноскоростных вычислительных устройств | 1991 |

|

SU1789986A1 |

| МОДУЛЬ ВВОДА-ВЫВОДА СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1991 |

|

RU2032201C1 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1993 |

|

RU2042183C1 |

| Устройство для тестового контроля цифровых узлов | 1987 |

|

SU1425682A1 |

| Устройство для ввода информации | 1989 |

|

SU1695314A1 |

| Логический анализатор | 1987 |

|

SU1476474A1 |

| Устройство для обработки запросов | 1989 |

|

SU1688248A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в автоматизированных устройствах управления в качестве буферного устройства памяти. Целью изобретения является повышение быстродействия обмена информацией между источником и приемником информации. Устройство содержит входной регистр, коммутатор, шесть элементов задержки, семь элементов И, два элемента ИЛИ, элемент ИЛИ-НЕ, два триггера, два дешифратора, два реверсивных счетчика, схему сравнения, двухразрядный счетчик и блок памяти. 1 ил.

| Устройство для определения частот обращения к программам | 1985 |

|

SU1357963A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1488815, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-11-07—Публикация

1988-08-01—Подача