ел ю

о

СА

ю о

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1605244A1 |

| Устройство КЭШ-памяти | 1988 |

|

SU1675881A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1163357A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ИСТОЧНИКА И ПРИЕМНИКА ИНФОРМАЦИИ | 2008 |

|

RU2364923C1 |

| Логический анализатор | 1987 |

|

SU1476474A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ИСТОЧНИКА И ПРИЕМНИКА ИНФОРМАЦИИ | 2010 |

|

RU2428737C1 |

| УСТРОЙСТВО ТЕСТОВОГО КОНТРОЛЯ | 2014 |

|

RU2565474C1 |

| Буферное запоминающее устройство | 1985 |

|

SU1287237A1 |

| Устройство для сопряжения в многотерминальной вычислительной системе | 1984 |

|

SU1166124A1 |

| Устройство для сопряжения ЭВМ | 1987 |

|

SU1418729A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для организации обмена информацией между элементами многопроцессорных вычислительных систем, а также в автоматизированных системах управления в качестве буферного устройства памяти. Цель изобретения - повышение производительности. Устройство содержит первую группу 1 элементов И, входной регистр 2, вторую и третью группы 3 и 4 элементов И, элементы ИЛИ признаков 5 и 6, информационную группу 7 элементов ИЛИ, регистры записи 8 и чтения 9, дешифраторы адреса 10 и 11, М блоков 12 буферной памяти. За счет обеспечения одновременной записи и считывания информации и за счет исключения передачи в устройство и дешифрации им адреса ячейки блока буферной памяти, в которую (из которой) записывается (считывается) информации, так как данный адрес формируется автоматически, повышается производительность обмена в системе. 2 ил.

го

0Ui.1

Изобретение относится к автоматике и вычислительной технике и может быть использовано для организации обмена информацией между элементами многопроцессорных вычислительных систем, а также в автоматизированных системах управления в качестве буферного устройства памяти;

Цель изобретения - повышение производительности устройства.

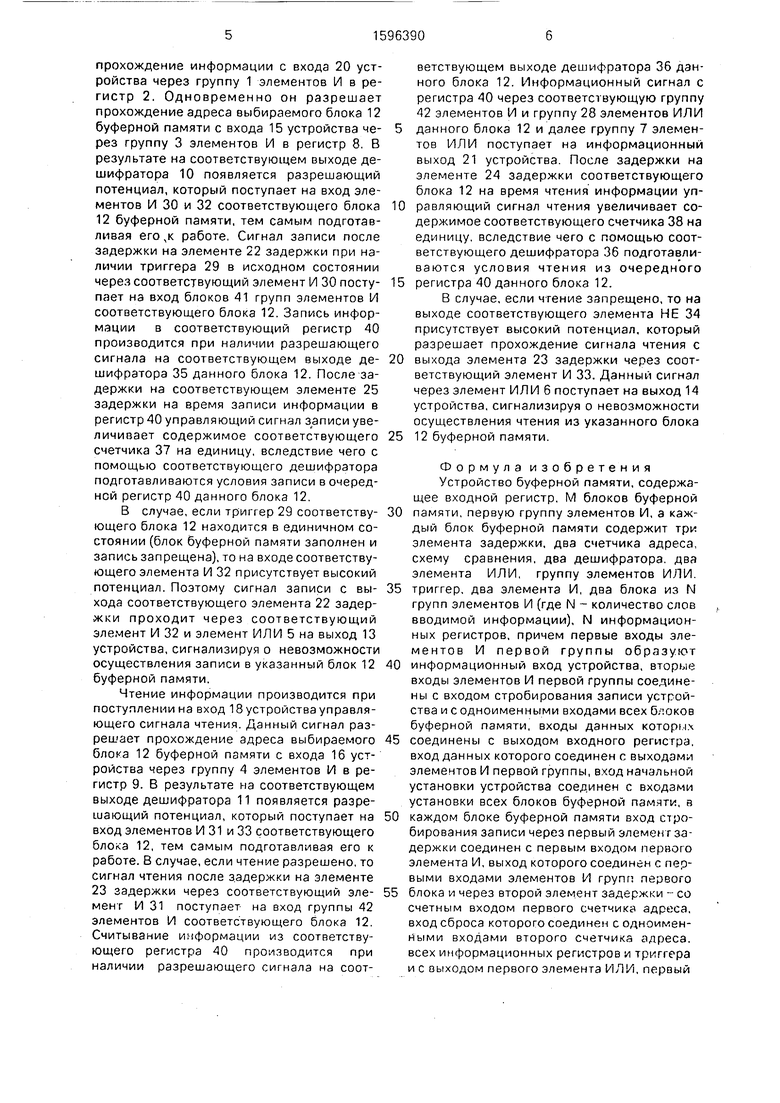

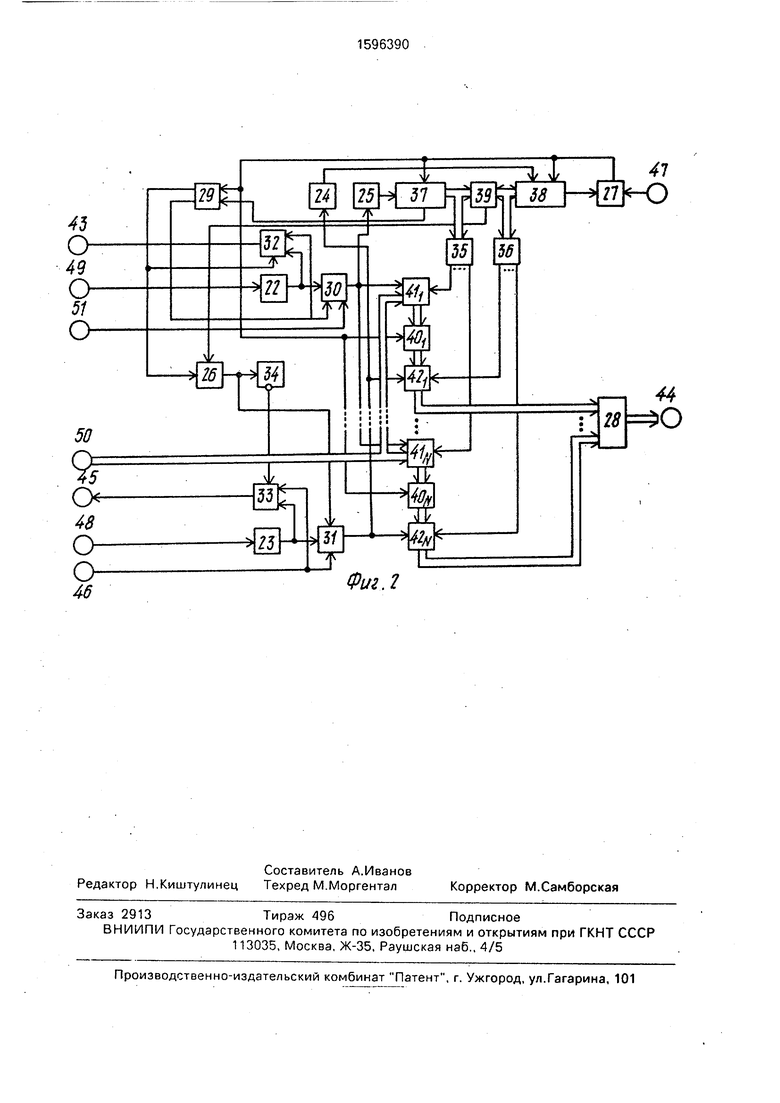

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - функциональная схема блока буферной памяти.

Устройство содержит (фиг. 1) первую группу 1 элементов И, входной регистр 2, вторую 3 и третью 4 группы элементов И, элементы ИЛИ 5 и б признака, информационную группу 7 элементов У1ЛИ, регистры записи 8 и чтения 9, дешифраторы 10 и 11 адреса, М блоков 12 буферной памяти, выходы 13 и 14 признака неготовности устройства, адресные входы 15 и 16 устройства, вход 17 стробирования записи устройства, вход 18 стробирования чтения устройства, вход 19 начальной установки устройства, информационный вход 20 устройства, информационный выход 21 устройства.

Блок 12 буферной памяти содержит (фиг. 2) элементы 22-25 задержки, элементы ИЛИ 26 и 27, группу 28 элементов ИЛИ, триггер 29, элементы И 30-33, элемент НЕ 34, дешифраторы 35 и 36 (адреса), счетчики 37 и 38 адреса, схему 39 сравнения, N информационных регистров 40, N групп 41 элементов И первого блока, N групп 42 элементов И второго блока.

На фиг. 2 также обозначены выход 43 неготовности записи блока буферной памяти, выход данных 44 блока буферной памяти, выход 45 неготовности чтения блока буферной памяти, первый вход 46 выбора блока буферной памяти, вход 47 установки блока буферной памяти, вход 48 стробирования чтения блока буферной памяти, вход 49 стробирования записи блока буферной памяти, вход 50 данных блока буферной памяти, второй вход 51 выбора блока буферной памяти.

Устройство работает следующим образом.

Код, установленный на регистре 8, определяет адрес блока 12 буферной памяти, в который должна быть записана информация при очередном обращении к устройству в режиме записи. Код, установленный на счетч ип е 37 i-ro блока 12 буферной памяти (i 1,М), определяет адрес j-ro (j 1, N) регистра 40, в который записывается информация при очередном обращении к устройству в режиме записи.

Код, установленный на регистре 9, определяет адрес блока 12 буферной памяти, из которого должна быть считана информация при очередном обращении к устройству в

режиме чтения. Код, установленный на счетчике 38 i-ro блока 12 буферной памяти, определяет адрес j-ro регистра 40, из которого считывается информация при очередном обращении к устройству в режиме чтения.

0 Запросы на запись и чтение в устройство поступают асинхронно, поэтому в процессе работы устройства запись информации осуществляется только в незанятые блоки 12 буферной памяти, а чтение

5 информации обеспечивается только из тех регистров 40, в которые была произведена запись. Это достигается следующим. После записи информации в N-й регистр 40 i-ro блока 12 буферной памяти счетчик 37 i-ro

0 блока 12 оказывается обнуленным в результате переполнения, при этом сигнал переполнения переводит триггер 29 1-го блока 12 в единичное состояние. Нулевой потенциал на инверсном выходе данного триггера 29

5 запрещает дальнейшую запись информации в 1-й блок 12. Одновременно высокий потенциал на прямом выходе триггера 29 поступает через элемент ИЛИ 26 i-ro блока 12 на вход элемента И 31 i-ro блока 12,

0 разрешая чтение из 1-го блока 12 независимо от состояния других управляющих элементов данного блока. В остальных случаях чтение из i-ro блока 12 разрешается при выполнении условия непревышения содержимым соответствующего счетчика 38 содержимого соответствующего счетчика 37. Если в 1-м блоке 12 содержимое счетчика 38 стало равным содержимому счетчика 37,-то на выходе несравнения соответствующей

0 схемы 39 сравнения устанавливается нулевой потенциал, который через соответствующий элемент ИЛИ 26 поступает на соответствующий элемент И 31 и запрещает чтение информации из i-ro блока 12.

5 Сброс триггера 29 i-ro блока 12 в исход-, ное состояние произеодится после чтения информации из N-ro регистра 40 1-го блока 12. При этом вырабатывается сигнал переполнения соответствующего счетчика 38,

0 который, поступая на соответствующий элемент ИЛИ 27, производит действия для i-ro блока 12. аналогичные сигналу начальной установки.

Перед началом работы с помощью им5, пульсного сигнала, поступающего на вход 19 устройства, во всех блоках 12 буферной памяти производится сброс счетчиков 37 и 38, регистров 40 и триггера 29,

При вводе и нформации сигнал записи подается на вход 17 устройства и разрешает

прохождение информации с входа 20 устройства через группу 1 элементов И в регистр 2. Одновременно он разрешает прохождение адреса выбираемого блока 12 буферной памяти с входа 15 устройства через группу 3 элементов И в регистр 8. В результате на соответствующем выходе дешифратора 10 появляется разрешающий потенциал, который поступает на вход элементов И 30 и 32 соответствующего блока 12 буферной памяти, тем самым подготавливая его,к работе, Сигнал записи после задержки на элементе 22 задержки при наличии триггера 29 в исходном состоянии через соответствующий элемент И 30 поступает на вход блоков 41 групп элементов И соответствующего блока 12. Запись информации в соответствующий регистр 40 производится при наличии разрешающего сигнала на соответствующем выходе дешифратора 35 данного блока 12. После задержки на соответствующем элементе 25 задержки на время записи информации в регистр 40 управляющий сигнал записи увеличивает содержимое соответствующего счетчика 37 на единицу, вследствие чего с помощью соответствующего дешифратора подготавливаются условия записи в очередной регистр 40 данного блока 12.

В случае, если триггер 29 соответствующего блока 12 находится в единичном состоянии (блок буферной памяти заполнен и запись запрещена), то на входе соответствующего элемента И 32 присутствует высокий потенциал. Поэтому сигнал записи с выхода соответствующего элемента 22 задержки проходит через соответствующий элемент И 32 и элемент ИЛИ 5 на выход 13 устройства, сигнализируя о невозможности осуществления записи в указанный блок 12 буферной памяти.

Чтение информации производится при поступлении на вход 18 устройства управляющего сигнала чтения. Данный сигнал разрешает прохождение адреса выбираемого блока 12 буферной памяти с входа 16 устройства через группу 4 элементов И в регистр 9. В результате на соответствующем выходе дешифратора 11 появляется разрешающий потенциал, который поступает на вход элементов И 31 и 33 соответствующего блока 12, тем самым подготавливая его к работе. В случае, если чтение разрешено, то сигнал чтения после задержки на элементе 23 задержки через соответствующий элемент И 31 поступает на вход группы 42 элементов И соответствующего блока 12. Считывание имформации из соответствующего регистра 40 производится при наличии разрешающего сигнала на соответствующем выходе дешифратора 36 данного блока 12. Информационный сигнал с регистра 40 через соответствующую группу 42 элементов И и группу 28 элементов ИЛИ данного блока 12 и далее группу 7 элементов ИЛИ поступает на информационный выход 21 устройства. После задержки на элементе 24 задержки соответствующего блока 12 на время чтения информации управляющий сигнал чтения увеличивает содержимое соответствующего счетчика 38 на единицу, вследствие чего с помощью соответствующего дешифратора 36 подготавливаются условия чтения из очередного регистра 40 данного блока 12.

В случае, если чтение запрещено, то на выходе соответствующего элемента НЕ 34 присутствует высокий потенциал, который разрешает прохождение сигнала чтения с выхода элемента 23 задержки через соответствующий элемент И 33. Данный сигнал через элемент ИЛИ 6 поступает на выход 14 устройства, сигнализируя о невозможности осуществления чтения из указанного блока 12 буферной памяти.

Формула изобретения Устройство буферной памяти, содержащее входной регистр. М блоков буферной памяти, первую группу элементов И, а каждый блок буферной памяти содержит три элемента задержки, два счетчика адреса, схему сравнения, два дешифратора, два элемента ИЛИ, группу элементов ИЛИ. триггер, два элемента И, два блока из N групп элементов И (где N - количество слов вводимой информации), N информационных регистров, причем первые входы элементов И первой группы образуют информационный вход устройства, вторые входы элементов И первой группы соединены с входом стробирования записи устройства и с одноименными входами всех блоков буферной памяти, входы данных которК1.ч соединены с выходом входного регистра, вход данных которого соединен с выходами элементов И первой группы,вход начальной установки устройства соединен с входами установки всех блоков буферной памяти, в каждом блоке буферной памяти вход стробирования записи через первый элемент задержки соединен с первым входом первого элемента И, выход которого соединен с первыми входами элементов И групп первого блока и через второй элемент задержки - со счетным входом первого счетчикз адреса, вход сброса которого соединен с одноименными входами второго счетчика адреса, всех информационных регистров и триггера и с выходом первого элемента ИЛИ, первый

вход которого является входом установки блока буферной памяти, второй вход первого элемента ИЛИ соединен с выходом переполнения второго счетчика адр.еса. информационный выход которого соединен с входом данных первого дешифратора и первым входом схемы сравнения, второй .вход которой соединен с входом данных второго дешифратора и с информационным выходом первого счетчика адреса, выход переполнения которого соединен с входом установки триггера, инверсный выход которого соединен с вторым входом первого элемента И, прямой выход триггера соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом Не равно схемы сравнения, выход второго элемента ИЛИ соединен с первым входом второго элемента И, выход которого соединен с первыми входами элементов И групп второго блока и через третий элемент задержки - со счетн ым входом второго счетчика адреса, вход данных блока буферной памяти соединен с вторыми входами элементов И групп первого блока, третьи входы которых соединены с соответствующими выходами второго дешифратора, выходы первого дешифратора соединены соответственно с вторыми входами элементов И групп второго блока, выходы элементов И 1-й группы (i 1, N) первого блока соединены с информационным входом 1-го информационного регистра, выход которого соединен с третьими входами элементов И i-й группы второго блока, выходы элементов И всех групп второго блока соединены с соответствующими группами входов элементов ИЛИ группы, отличающееся тем, что, с целью повышения производительности, в устройство введены первый и второй дешифраторы адреса, регистр записи и регистр чтения, вторая и третья группы элементов И, первый и второй элементы ИЛИ признака, информационная группа . элементов ИЛИ, а в каждый блок буферной памяти - четвертый элемент задержки, элемент НЕ, третий и четвертый элементы И, причем вход стробирования записи устройства соединен с первыми входами элементов И второй группы, вторые входы которых соединены с первым адресным входом устройства, а выходы - с разрядами информационного входа регистра записи, выход которого соединен с входом первого дешифратора адреса, выходы которого соединены с первыми входами выбора соответствующих блоков буферной памяти, выходы неготовности записи которых соединены, с входами первого элемента ИЛИ признака, выход которого является первым выходом признака неготовности устройства, вход

стробирования чтения устройства соединен с одноименными входами всех блоков буферной памяти и первыми входами элементов И третьей группы, вторые входы которых соединены с вторым адресным входом устройства, а выходы - с разрядами информационного входа регистра чтения, выход которого соединен с входом второго дешифратора адреса, выходы которого соединены с вторыми входами выбора соответствующих блоков буферной памяти, выходы неготовности чтения которых соединены с входами второго элемента ИЛИ признака, выход которого является вторым выходом яризнака неготовности устройства, выходы

данных каждого блока буферной памяти соединены с соответствующими группами входов элементов ИЛИ информационной группы, выходы которых образуют информационный выход устройства, в каждом

блоке буферной памяти выход данных соединен с выходами элементов ИЛИ группы, вход строба чтения блока буферной памяти через четвертый элемент задержки соединен с вторым входом второго элемента И,

третий вход которого соединен с вторым входом выбора блока буферной памяти, первый вход выбора которого соединен с третьим входом первого элемента И и первым входом третьего элемента И, второй

вход которого соединен с выходом первого элемента задержки, прямой выход триггера соединен с третьим входом третьего элемента И, выход которого является выходом неготовности записи блбка буферной памяти, выход неготовности чтения которого соединен с выходом четвертого элемента И, первый вход которого через элемент НЕ соединен с выходом второго элемента ИЛИ, второй вход четвертого элемента И соединен с третьим входом второго элемента И, второй вход которого соединен с третьим входом четвертого элемента И.

| Буферное запоминающее устройство | 1982 |

|

SU1111202A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-09-30—Публикация

1988-09-26—Подача