(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения дифференциальных уравнений в частных производных | 1989 |

|

SU1675911A1 |

| Устройство для решения дифференциальных уравнений в частных производных | 1982 |

|

SU1096663A1 |

| Аналого-цифровое вычислительное устройство | 1986 |

|

SU1388913A1 |

| Устройство для выделения признаков при распознавании случайных сигналов | 1990 |

|

SU1797134A1 |

| Устройство для решения нелинейных задач теплопроводности | 1986 |

|

SU1363269A1 |

| Устройство для решения задач оптимального управления | 1985 |

|

SU1327135A1 |

| Устройство для обхода узлов сеточной модели | 1985 |

|

SU1322332A1 |

| Устройство для решения нелинейных краевых задач | 1987 |

|

SU1683028A1 |

| Устройство для ввода информации | 1989 |

|

SU1665364A2 |

| Функциональный преобразователь | 1985 |

|

SU1267445A2 |

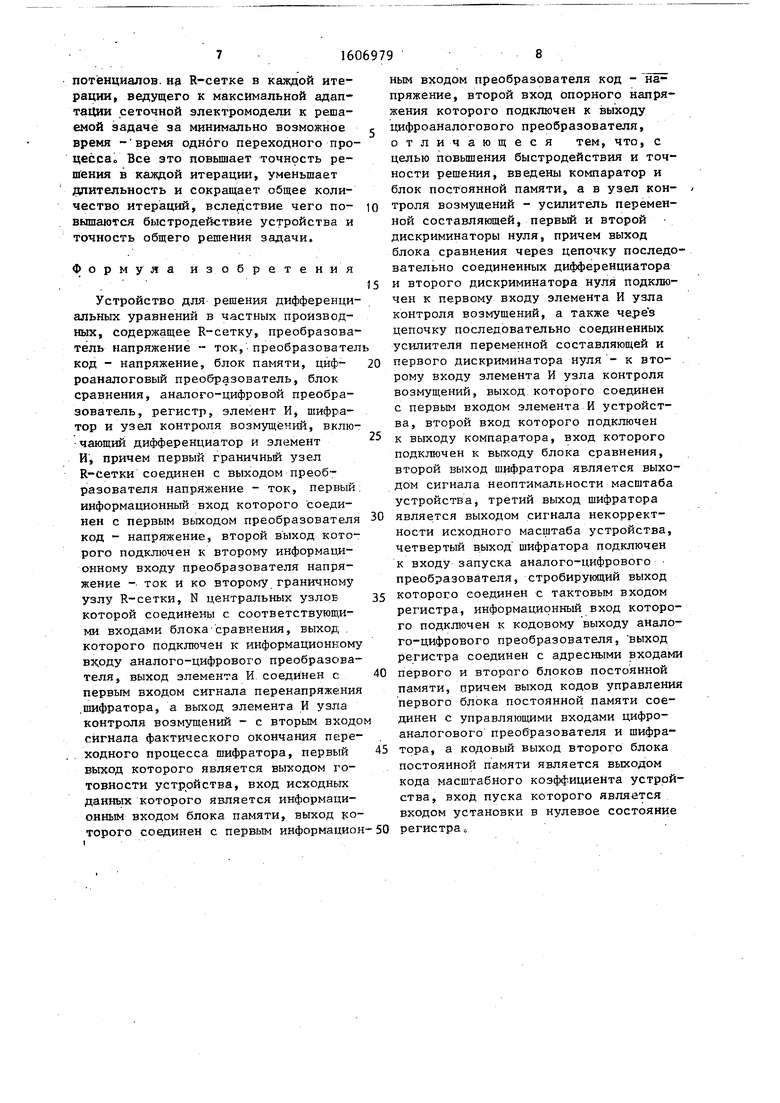

Изобретение относится к аналого-цифровой вычислительной технике и предназначено для решения дифференциальных уравнений в частных производных. Целью изобретения является повышение быстродействия и точности решения. Для этого устройство дополнительно содержит компаратор, два блока постоянной памяти, усилитель переменной составляющей и два дискриминатора нуля. Это дает возможность использовать табличный способ вычисления оптимальных кодов опорного напряжения и масштабных коэффициентов, осуществлять непрерывный аппаратный контроль перенапряжений, а также регистрировать момент фактического окончания переходного процесса распределения узловых потенциалов в каждой итерации. 9 ил.

Изобретение относится к аналого- цифровой вычислительной технике и предназначено для решения дифференциальных уравнений в частных производных .

Целью изобретения является повьше- ние быстродействия устройства и точности-решения.

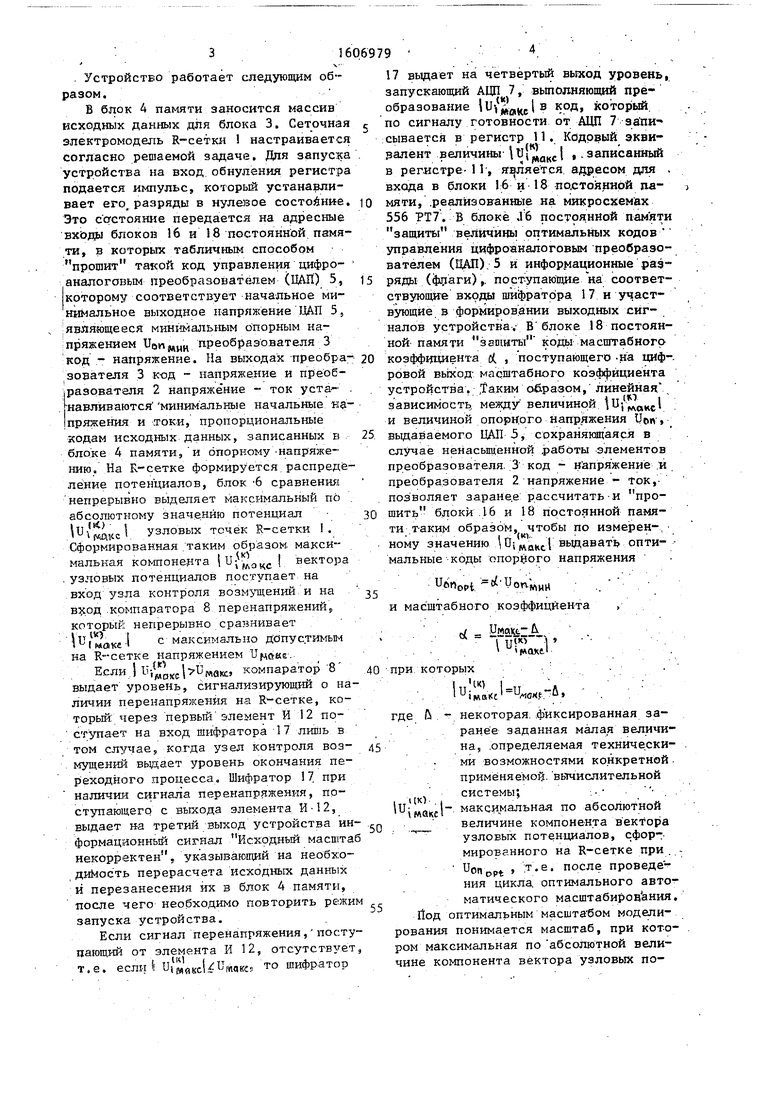

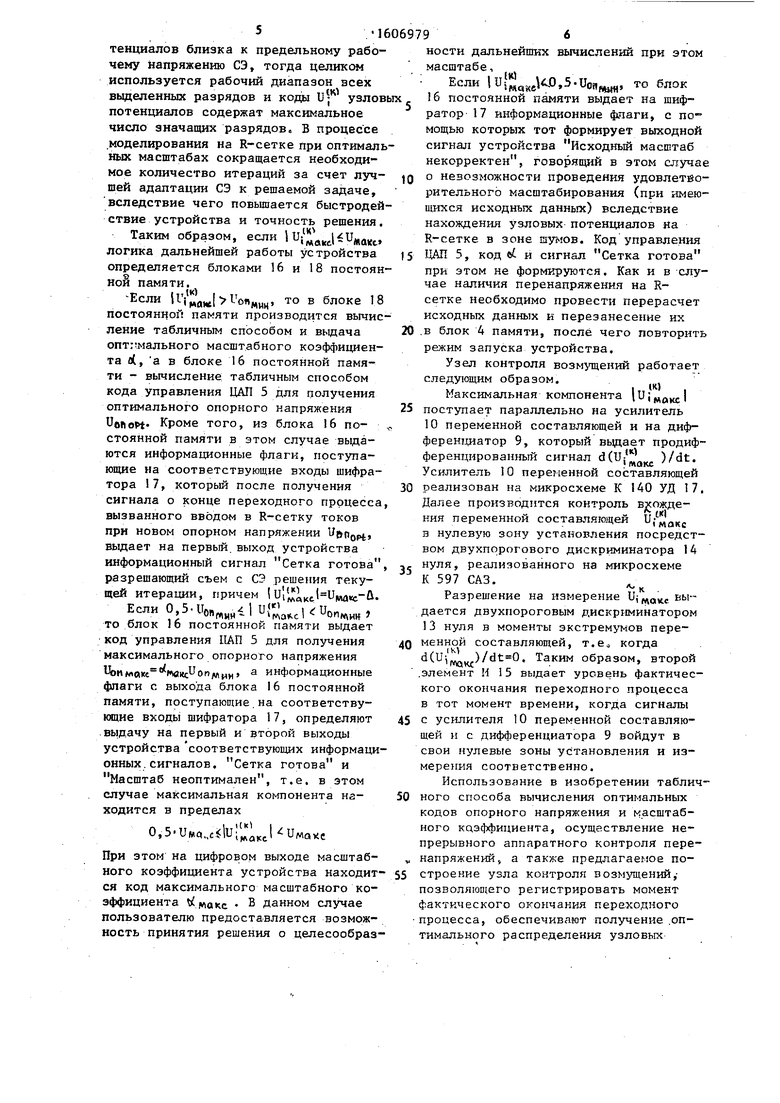

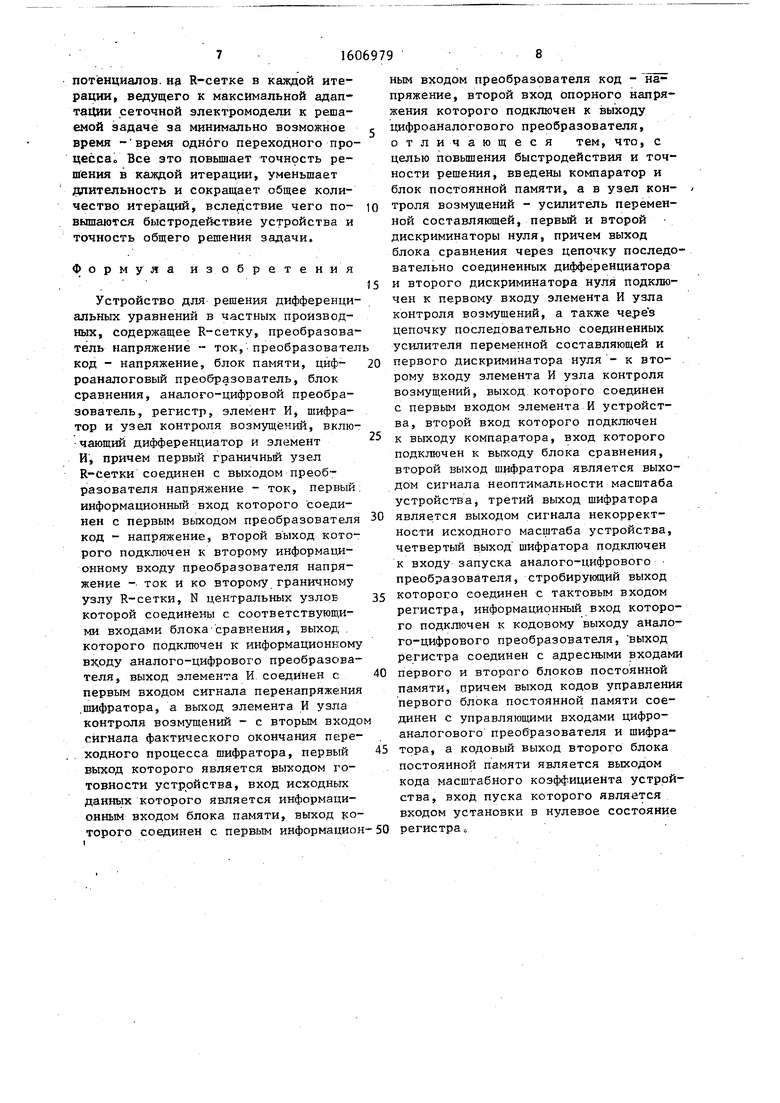

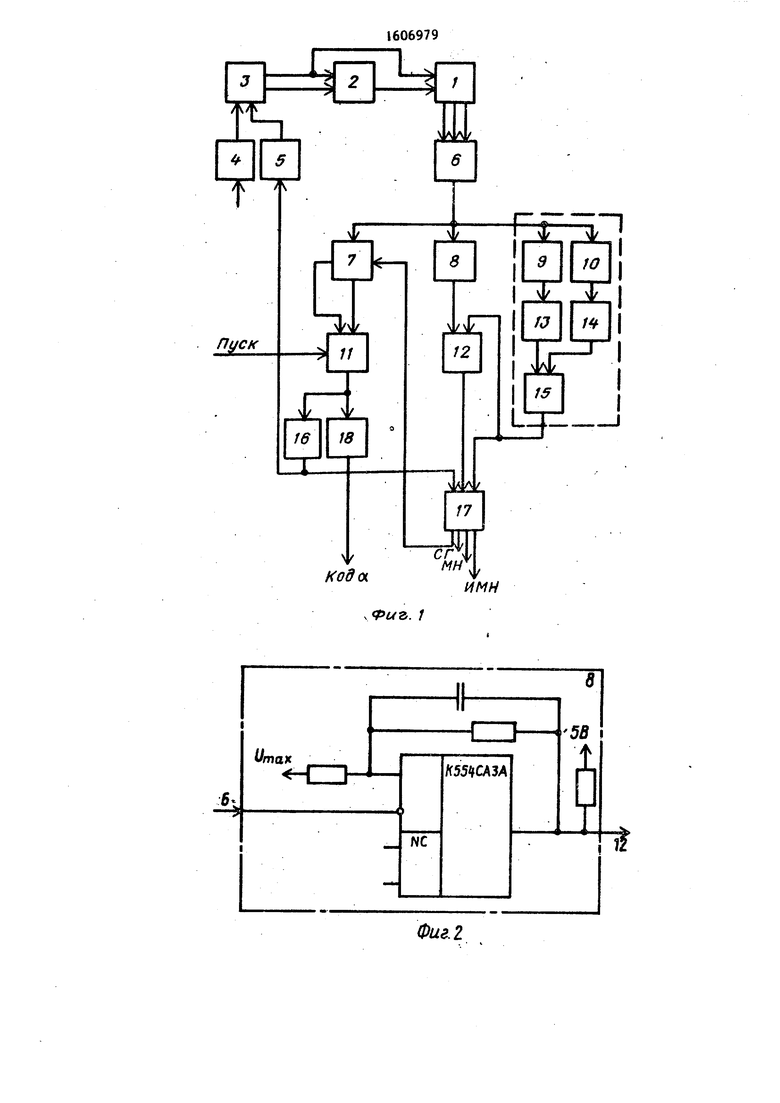

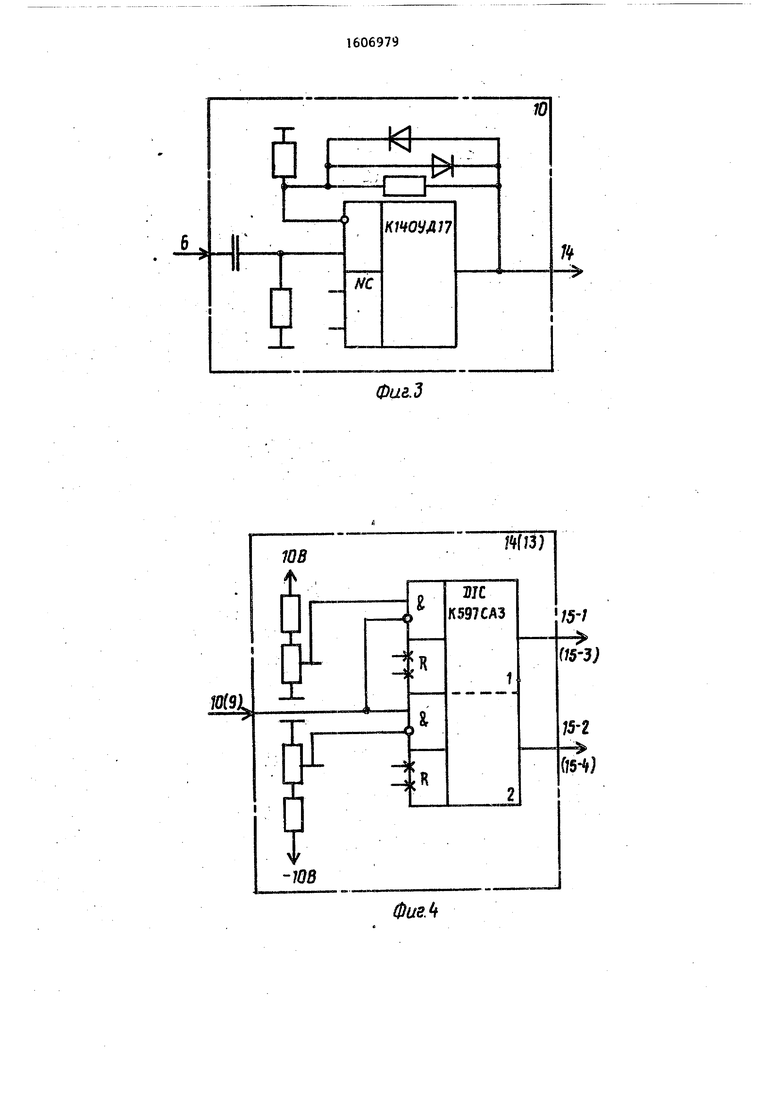

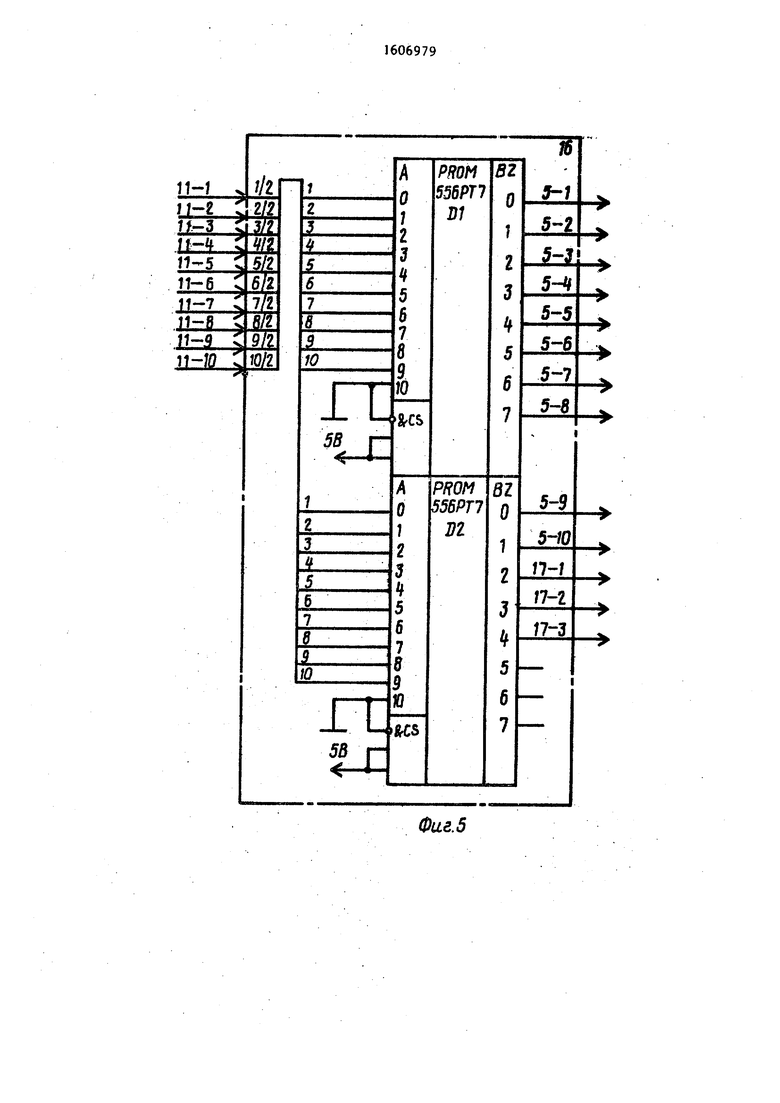

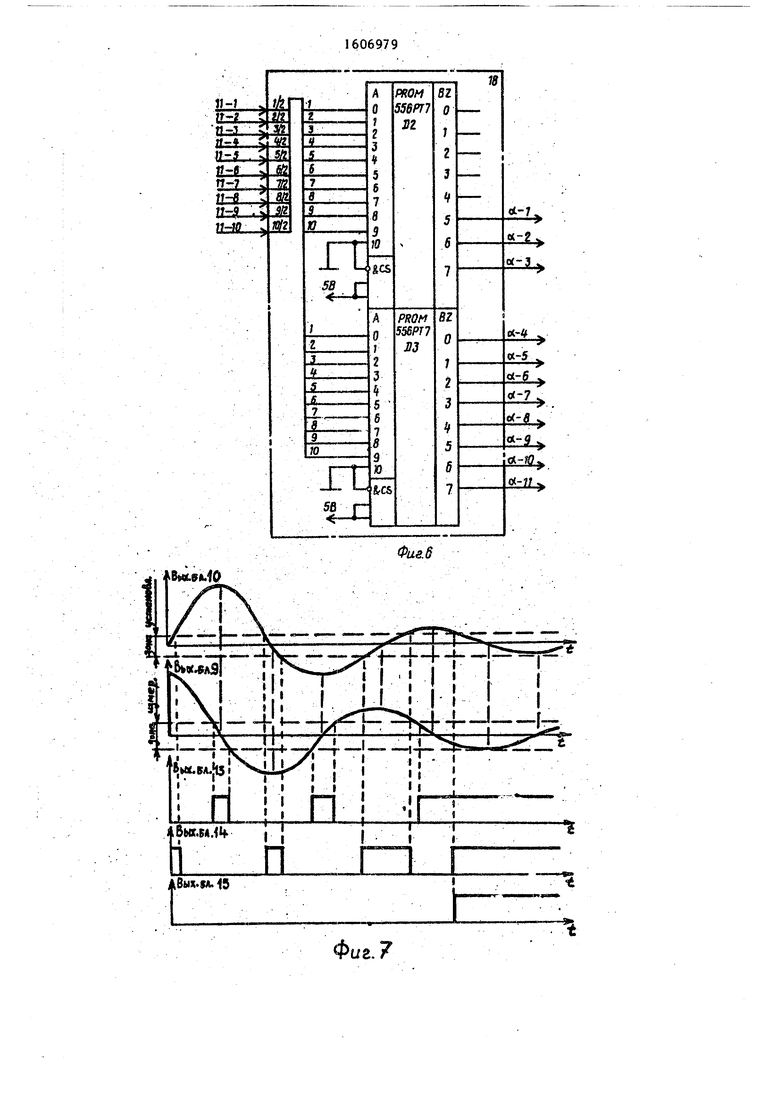

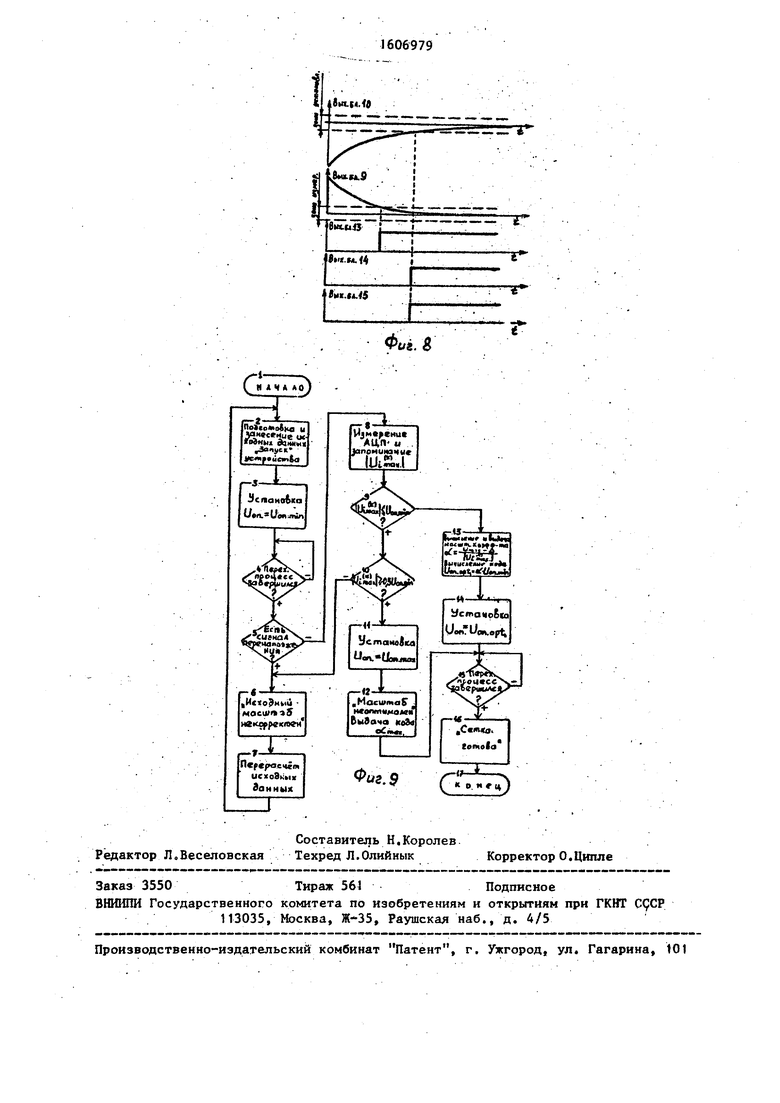

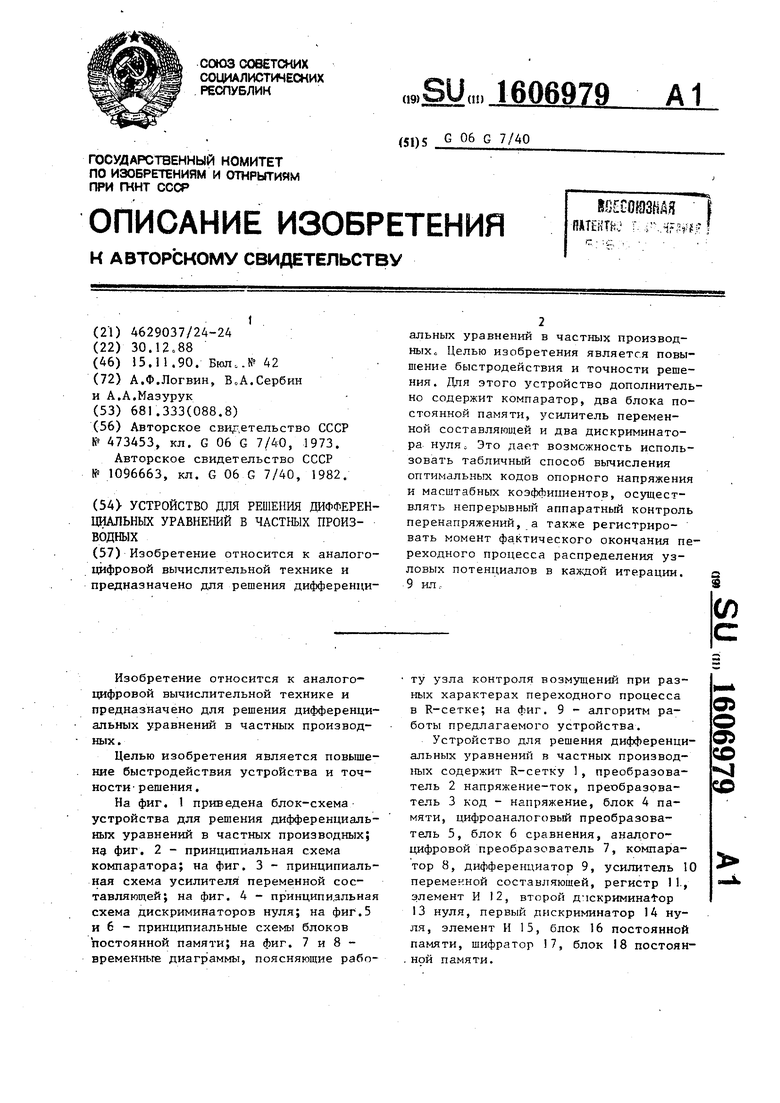

На фиг. 1 приведена блок-схема устройства для решения дифференциальных уравнений в частных производных; Н9 фиг, 2 - принципиальная схема компаратора; на фиг. 3 - принципиальная схема усилителя переменной составляющей; на фиг. 4 - принципиальная схема дискриминаторов нуля; на фиг.5 и б - принципиальные схемы блоков постоянной памяти; на фиг. 7 и 8 - временные диагр1аммы, поясняющие работу узла контроля возмущений при разных характерах переходного процесса в R-сетке; на фиг. 9 - алгоритм работы предлагаемого устройства.

Устройство для решения дифференциальных уравнений в частных производных содержит R-сетку 1, преобразователь 2 напряжение-ток, преобразователь 3 код - напряжение, блок 4 памяти, цифроаналоговый преобразователь 5, блок б сравнения, аналого- цифровой преобразователь 7, компаратор 8, дифференциатор 9, усилитель 10 переменной составляющей, регистр 1 1., элемент И 12, второй д:1скримина ор 13 нуля, первый дискриминатор 14 нуля, элемент И 15, блок 16 постоянной памяти, шифратор 7, блок 18 постоян- .ной памяти.

О)

о

О)

со

vl

со

. УстройстЕЮ работает следующим образом.

В блок 4 памяти заносится массив исходных данных для блока 3. Сеточная электромодель R-сетки настраивается согласно решаемой задаче. Для запуска устройства на вход обнуления регистра подается импульс, который устанавливает его, разряды в нулевое состояние. Это состояние передается на адресные вх оды блоков 16 и 8 постоянной памяти, в которых табличным способом прошит такой код управления цифро- аналоговым преобразоват«шем (ЦАП) 5, которому соответствует начальное ми- Н1шальное выходное напряжение 1ДА.П 5,, явпяк щееся минимальным опорным напряжением Uon преобразователя 3 код - напряжение. На выходах преобразователя 3 к-од напряжение и преоб- |разоват-еля 2 напряжение - ток навливаются миннм альные начальные, на- 1пряжения и ТОКИ, пропорциональные кодам исходных данных, записанных в блоке 4 памяти, и бноркому-напряжению. На Fv-сетке формируется, распределение потенциалов, блок -6 сравнения непрерывно выделяет максимальный по абсолютному значению потенциал узловых точек R-сетки I. Сформированная .таким образом, макси-

вектора

I . К;|

малькая коьшоне 1та ,

узловых потенциалов поступает, на

вход узла контроля возм тцений и на

.компаратора 8 перенапряжений,

который непрерывно сравнивает

U| iMaKC-i с максимально допустимы

на К сетке напряжением и(цсгИ.

Если j (.| Uwaxc. компаратор 8 выдает уровень, сигнализирующий о наличии перенапряжения на R-сетке, который: через первый элемент И 12 поступает на вход шифратора 17 лишь в том случае, ко.гда узел контроля воз- мущений выдает уровень окончания переходного процесса. Шифратор 17 при наличии сигнала перенапряжения, поступающего с вьпсода элемента. И-12, выдает на третий выход устройства ин формационный сигнал Исходный масшта некорректен, указывающий на необхо- дийос ть перерасчета исходных данных и перезанесения их в блок 4 памяти, после чего необходимо повторить режи запуска устройства.

Если сигнал перенапряжения, поступающий от элемента И 12, отсутствз ет т.е. если I U, тк то шифратор

35

17 выдает на четвертый выход уровень, запускающий АЦП 7, вьтолняющий преобразование lU fSoKcl который.

по сигналу готовности от АЦП 7 aatiH- сывается в регистр 11. Кодовый эквивалент величины lUJ JI g jl ..записанный в регистре-11, является адресом для . входа в блоки 16 и 18 пастоянной да-

0 мяти, .реализованные на микросхемах 556 РТ7. В блоке J6 постоя.нной пам яти защиты велйчинь оптимальных кодов управления цифроаналоговым преобразователем (ЦАП). 5 и информационные раз5 ряды (ф ггаги),. поступающие на соответствующие входы шифратора 17 и участвующие в формировании выходных сигналов устройства,- В блоке 18 постоянной памяти защиты кодь масштабного0 коэффициента о(. , поступающего-на цИф-.

ровой вь1ход- масщтабного коэффициента , устройства. ,Таким обра-зом, линейная .. зависимость, между величиной ,jl и величиной опорного напряжения Uon,

5 вьщаваемого ЦАП 5, сохраняющаяся в случае ненасыщенной .работы элементов преобразователя. 3 код - н апряжениё .и преобразователя 2 напряжение - позволяет заранее рассчитать-и про30 щить блоки .16 и 18 постоянной памяти .т-аким образом, чтобы по измерен-,- . ному значению О, выдават ь опти- - мальные коды опорного напряжения

UftUppt (; Цопм„й .. и масштабного коэффициента ,

It-А.

I и «(1

ЧЛОХй

при которых Чк)

I А iwaKt -UAiOH.t..-й.

где

U :цк).

некоторая, .фиксированная заранее заданная малая величина, .определяемая техническими возможностями конкретной применяемой, вычислительной системы; -. , - .

1 К1-

lU: „и ,I- максимальная по абсолютной

V WdKC , .

величине компонента вектора узловых потенциалов, сфортмированного на R-сетке при . Uonppt после проведения цикла, оптимального авто матического масщтабиров ания .Йод оптимальным масштабом моделирования понш-шется масщтаб, при котором максимальная по абсолютной величине компонента вектора узловых потенциалов близка к предельному рабочему напряжению СЭ, тогда целике используется рабочий диапазон всех

flf

выделенных разрядов и коды U; узлов

потенциапов содержат максимальное число значащих разрядов. В процессе .моделирования на R-сетке при оптималных масштабах сокращается необходимое количество итераций за счет лучшей адаптации СЭ к решаемой задаче, вследствие чего повышается быстродействие устройства и точность решения, Таким образом, если 1 ,

логика дальнейшей работы устройства определяется блоками 16 и 18 постоянной памяти.

1

-Если , блоке 18 постоянной памяти производится вычисление табличным способом и вьщача оптг мального масштабного коэффициента at, а в блоке 16 постоянной памяти - вычисление табличным способом кода управления ЩШ 5 для получения оптимального опорного напряжения Uanopf Кроме того, из блока 16 по- стоянной памяти в этом случае выдаются информационные флаги, поступающие на соответствующие входы шифратора 17, которьй после получения сигнала о конце переходного процесса вызванного вводом в R-сетку токов при новом опорном напряжении , вьздает на первый.выход устройства информационный сигнал Сетка готова разрешающий съем с СЭ решения текущей итерации, причем ul; tl UwaKc-u.

ЕслиО 5.ио„„„„11и.Г,, то блок 16 постоянной памяти выдает код управления 11АП 5 для получения максимального опорного напряжения lfenwaite fMi{cUon,, а информационные флаги с выхода блока 16 постоянной памяти, поступающие.на соответствующие входы шифратора 17, определяют выдачу на первый и второй выходы устройства соответствующих информационных, сигналов. Сетка готова и Масштаб неоптимален, т.е. в этом случае максимальная компонента находится в пределах

0,5.и«о.,,,иимаке

При зтом на цифровом выходе масштаб- ного коэффициента устройства находит- ся код максимального масштабного коэффициента макс В данном случае пользователю предоставляется возможность принятия решения о целесообраз

0

5

0

,

0

5

0

ности дальнейших вычислений при зтом масштабе,

Если lu|SaKe 5-Uoi Bj, то блок

16 постоянной памяти выдает на шифратор 17 информационные флаги, с помощью которых тот формирует выходной сигнал устройства Исходньй масштаб некорректен, говорящий в этом случае

0 о невозможности проведения удовлетйо- рительногЬ масштабирования (при имеющихся исходш х данных) вследствие нахождения узловых потенциалов на R-сетке в зоне тумов. Код управления

5 ЦАП 5, код ei и сигнал Сетка готова при этом не формируются. Как и в случае наличия перенапряжения на Н- сетке необходимо провести перерасчет исходных данных и переэанесение их .в блок 4 памяти, после чего повторить режим запуска устройства.

Узел контроля возм:,тцений работает следующим образом.

Максимальная компонента поступает параллельно на усилитель 10 переменной составляющей и на диф- ферениднатор 9, который вьщает продифференцированный сигнал d(Uj JJ )/dt. Усилитель 10 переменной составляющей реализован на микросхеме К 140 УД 17. Далее производится контроль вгсожде- ния переменной составляющей U/l .,„

М{ЛпС

в нулевую зону установления посредством двухпорогового дискриминатора 14 нуля, реализованного на микросхеме К 597 САЗ.

К

Разрешение на измерение выдается двухпороговым дискриминатором 13 нуля в моменты экстремумов пересоставляющей, т.е, когда

меннои

d(U ,). Таким образом, второй .элемент И 15 выдает уровень фактического окончания переходного процесса в тот момент времени, когда сигналы с усилителя 10 переменной составляющей и с диф(3)еренциатора 9 войдут в свои нулевые зоны установления и измерения соответственно.

Использование в изобретении табличного способа вычисления оптимальных кодов опорного напряжения и масштабного кцэффициента, осуществление непрерывного аппаратного контроля перенапряжений, а также предлагаемое построение узла контроля возмущений,- позволяющего регистрировать момент фактического окончания переходного процесса, обеспечивают получение .оптимального распределения узловых

потенциалов, нз R-сетке в каждой итерации, ведущего к максимальной адаптации сеточной электромодели к решаемой задаче за минимально возможное время - время одного переходного процесса Все это повышает точность решения в каждой итерации, уменьшает длительность и сокращает общее количество итераций, вследствие чего по- вышаются быстродействие устройства и точность общего решения задачи.

Формула изобретения

Устройство для решения дифференциальных уравнений в частных производных, содержащее R-сетку, преобразователь напряжение ток, преобразовател код - напряжение, блок памяти, циф- роаналоговый преобразователь, блок сравнения, аналого-цифровой преобразователь, регистр, элемент И, шифратор и узел контроля возмущений, вклю- чающий дифференциатор и элемент И, причем первый граничный узел R-сетки соединен с выходом преобразователя напряжение - ток, первый: информационный вход которого соединен с первым выходом преобразователя код - напряжение, второй выход которого подключен к второму информаид- онному входу преобразователя напряжение - ток и ко второму граничному узлу R-сетки, N центральных узлон; которой соединены с соответствующими входами блока Сравнения, выход . которого подключен к информационному вх;оду аналого-цифрового преобразователя, выход элемента И соединен с первым входом сигнала перенапряжения .шифратора, а выход элемента И узла контроля возмущений - с вторым входо сигнала фактического окончания переходного процесса шифратора, первый выход которого является выходом готовности устройства, вход исходных даннь х которого является информационным входом блока памяти, выход которого соединен с первым информацион

с

5

25

0 30 35 40 45 50

ным входом преобразователя код - напряжение, второй вход опорного напряжения которого подключен к выходу цифроаналогового преобразователя, отличающеся тем, что, с целью повьш1ения быстродействия и точности решения, введены компаратор и блок постоянной памяти, а в узел контроля возмущений - усилитель переменной составляющей, первый и второй дискриминаторы нуля, причем выход блока сравнения через цепочку последовательно соединенных дифференциатора и второго дискриминатора нуля подключен к первому входу элемента И узла контроля возмущений, а также через цепочку последовательно соединенных усилителя переменной составляющей и первого дискриминатора нуля - к второму входу элемента И узла контроля возмущений, выход которого соединен с первым входом элемента И устройства, второй вход которого подключен к выходу компаратора, вход которого подключен к вьгходу блока сравнения, второй выход шифратора является выходом сигнала неоптимальности масштаба устройства, третий выход шифратора является выходом сигнала некорректности исходного масщтаба устройства, четвертый выход шифратора подключен к входу запуска аналого-цифрового преобразователя, стробирующий выход которого соединен с тактовым входом регистра, информационный вход которого подключен к кодовому выходу аналого-цифрового преобразователя, выход регистра соединен с адресными входами первого и второго блоков постоянной памяти, причем выход кодов управления первого блока постоянной памяти соединен с управляющими входами цифро- аналогового преобразователя и шифратора, а кодовый выход второго блока постоянной памяти является выходом кода масштабного коэфф.ициеНта устройства, вход пуска которого является входом установки в нулевое состояние регистра

код Л

ИМИ

.. 1

Фиг. 2

ML

йW

KIwyAI

yvc

П

-

Фиг.З

пт

2JC К597САЗ

15-J

-

f/5-з;

а

/5-2

(

/3)/гЛ

Фиг.5

Bt«.ffft.40

Фаг. 7

U

ЖГай.йjn

г

ltf f uanta

г-3

I .fenaMobxi

{Лсрсраечёп Г исхоЭкмх I данных

Фиг. В

1м «г«С|1гн

«« «ttf-iiir

.

К: :;у ::чг±.1

gMactvmaS неоптммэми Бы8ача квЗв

,

Фиг 9 / Ч

С It о чец

| Авторское свир етельство СССР К« 473453, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для решения дифференциальных уравнений в частных производных | 1982 |

|

SU1096663A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-11-15—Публикация

1988-12-30—Подача