Изобретение относится к аналоговой и гибридной вычислительной технике и предназначено для решения нелинейных задач теплопроводности.

Цель изобретения - упрощение устройства.

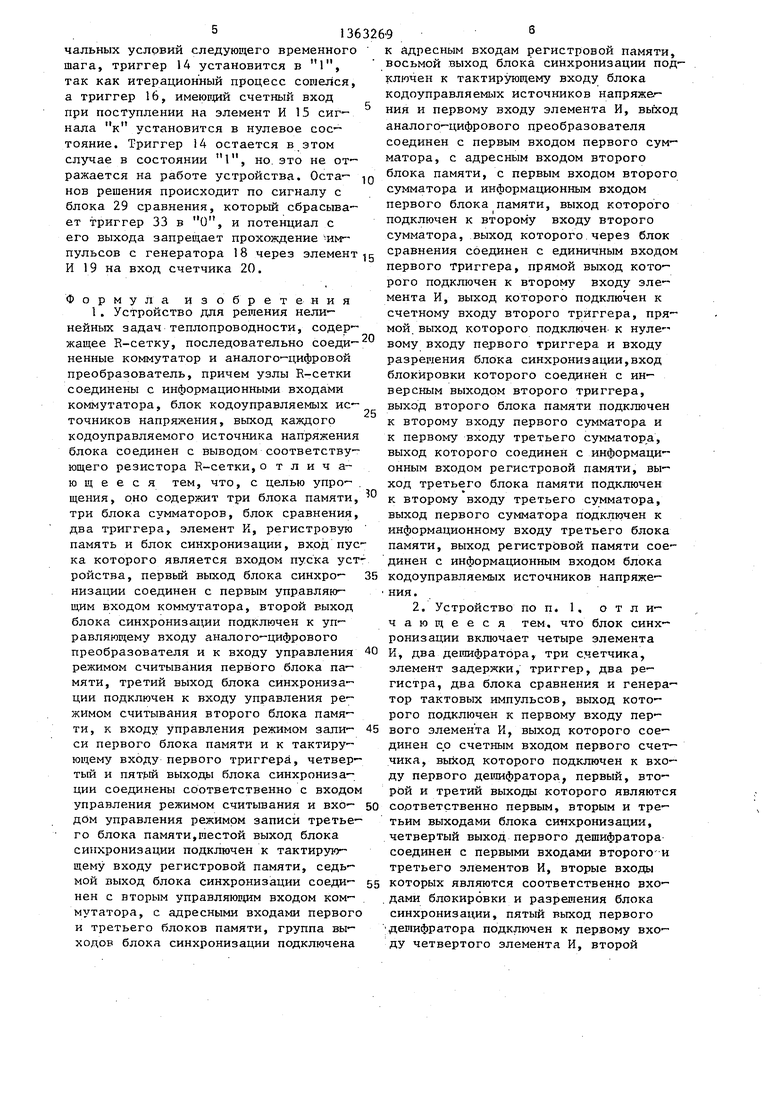

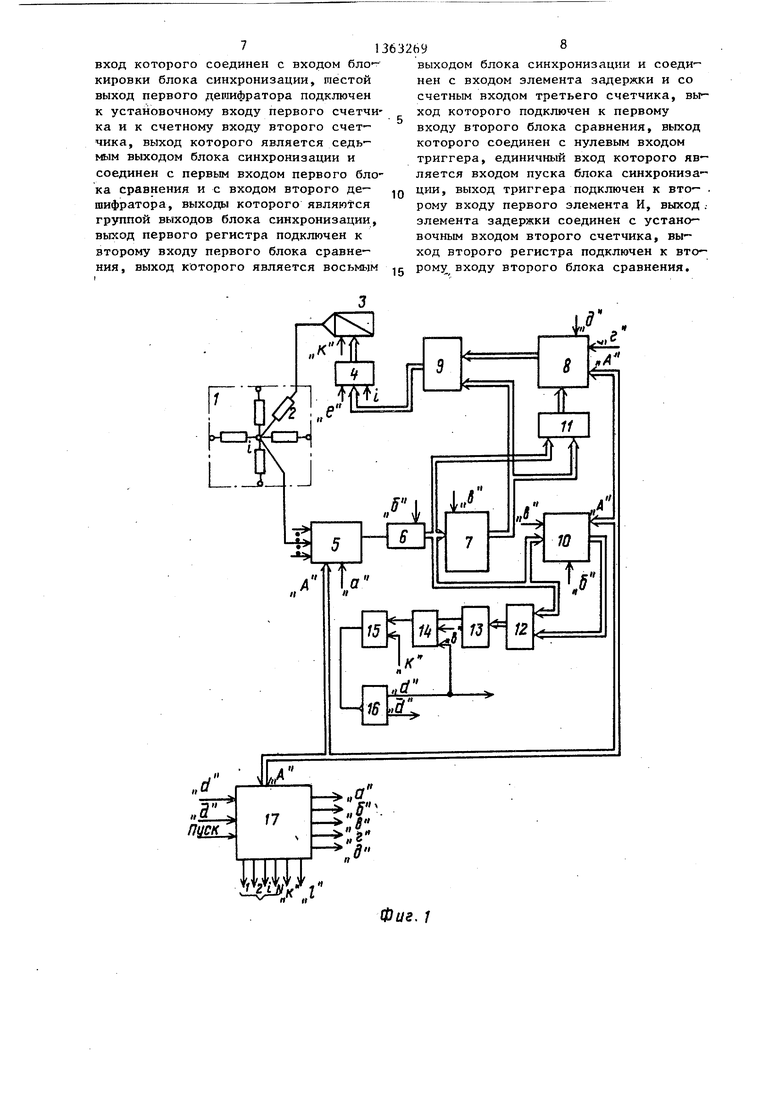

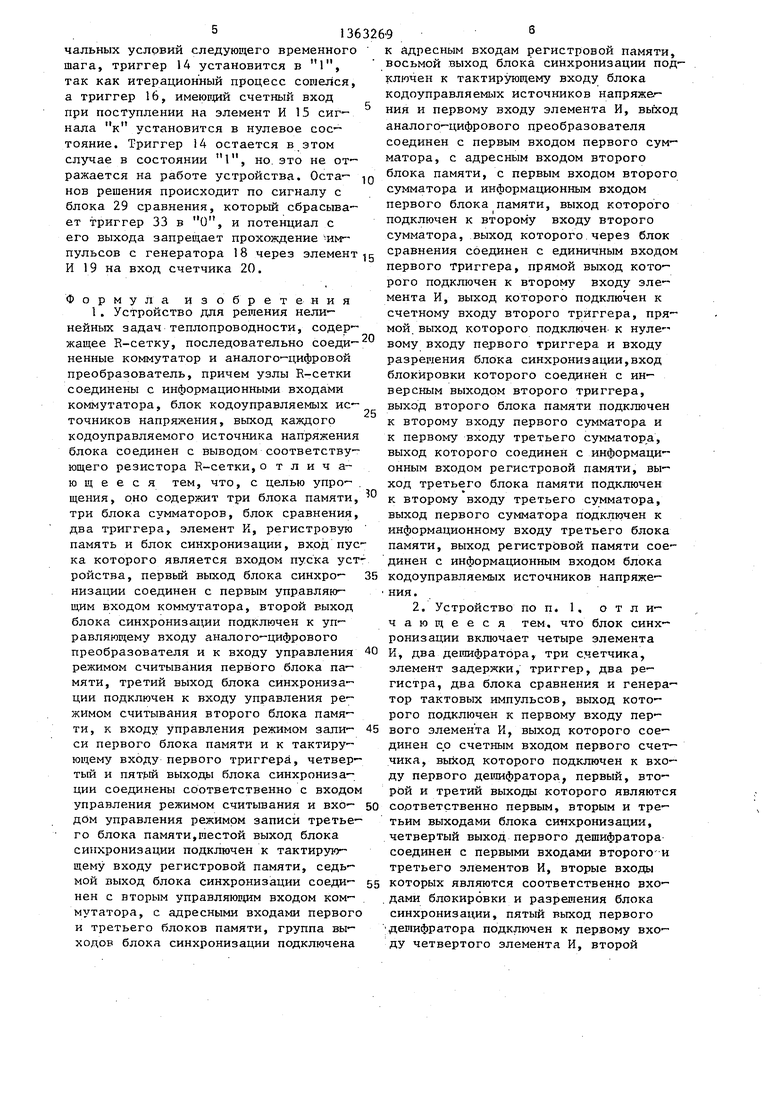

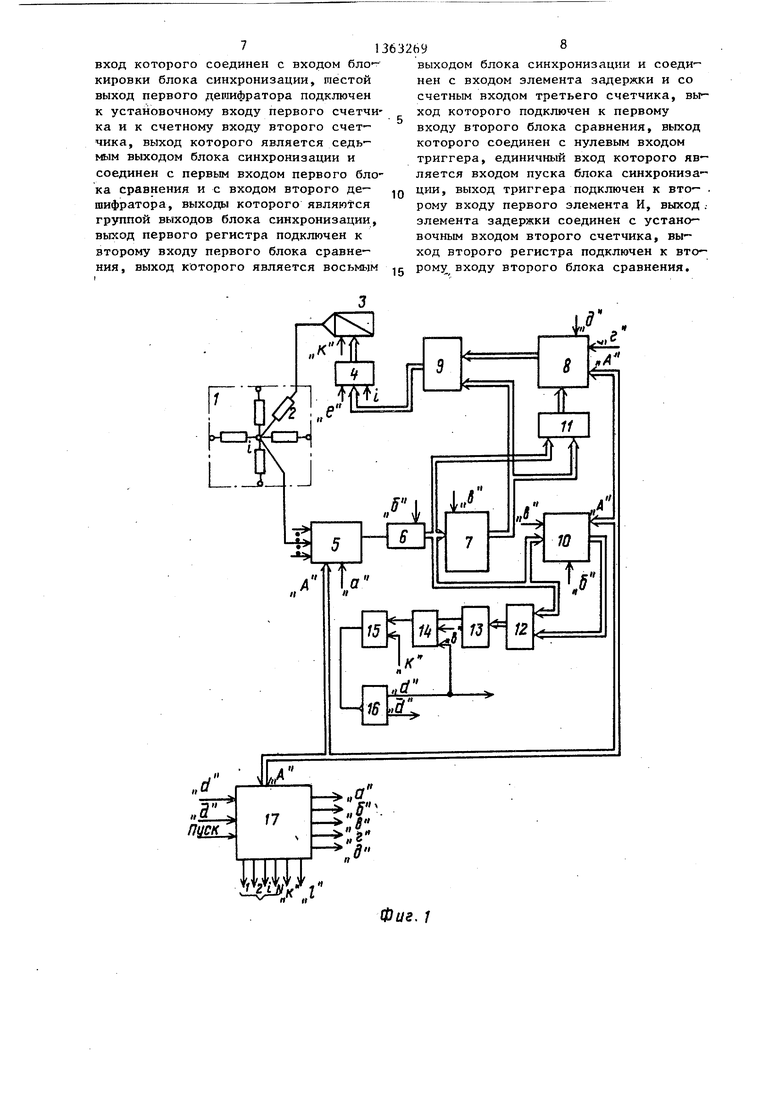

На фиг. 1 изображена блок-схема устройства; на фиг. 2 - блок синхронизации.

Устройство для решения нелинейных задач теплопроводности содер шт R- сетку 1, в каждый узел которой подключены временные резисторы 2, блок 3 кодоуправляемых источников напряжения, регистровую память 4, коммутатор 5, аналого-цифровой преобразователь 6 (АЦП), второй 7 и третий 8 блоки памяти, третий сумматор 9, первый

блок 10 памяти, первый 11 и второй 12 сумматоры, блок 13 сравнения, первый триггер 14, элемент И 15, второй триггер 16, блок 17 синхронизации.

Блок 17 синхронизации содержит генератор 18 тактовых импульсов, пер- вый элемент И 19, первый счетчик 20, первый дешифратор 21, второй 22 и третий 23 элементы И, второй счетчик 24, второй дешифратор 25, первый блок 26 сравнения, первый регистр 27, третий счетчик 28, второй блок 29 сравнения, второй регистр 30, Элемент 31

задержки, четвертый элемент И 32, триггер 33.

Нелинейное уравнение теплопроводности имеет вид

fifT 1 + Ь(Ф) 1 -г fTl dxj/ fJ ) ir

(1)

Используя подстановку для преобра зования левой части уравнения (1)

1

0 5л(Т)йТ(2)

1„

и подстановку для преобразования пра- 45 вой части уравнения (1)

Н. Jc(T)dT,

(3)

получим уравнение

Ч + i

зх ау з г

(4)

которое может быть смоделировано на Н-сетку.

Кодоуправляемый источник напряжения нужен в этом случае для задания соответствующих начальных условий или напряжения, полученного в данном уз-

ле сетки на предьщущей итерации. Формируют это напряжение два блока памяти и два сумматора.

Блок 7 памяти представляет собой табличную память, позволяющую переводить одну моделируемую величину в другую. Для моделирования уравнения (4), выраженного в конечно-разностной форме oW (i ) д() . (k)

-Lt-Ji- l-LLdii. + °jt liji2-Jj. +

h

h

.(11

.-6

(V)

e

w

ли

. ЬЛ + S l, t,,-i.n

, It) I 0

tJj.llL5ii

20

25Liji:iz :ij JrMi :Su

30

функцию Н надо связать с функцией 0.

Пусть . Тогда правая часть уравнения будет иметь вид

.(

- или

(fi

Jk-t) СИ

, fi,i,n (

s ,.--.t,n.

И для моделирования ее при реализации на R-сетке нужно на второй вывод временного резистора подать напряже-

35

45

ние, пропорциональное функхши G

((.-1/

у .l J Lt rL JflCLJirrri J UJ J niXJ-lrTlrl i

Если значение функции 0 в данной точке, полученное в (п-1)-й момент времени, а также значение функции F в этой же точке, рассчитанное по результатам моделирования на (п-1)-м шаге времени, сохранить в третьем блоке 8 памяти и на временном шаге 40 i на (К-1)-й итерации к разности этих значений в,

.t.n -Ps,-t;n.

(1t-1l

50

вить вновь определенное F j , то

через временной резистор 2 пойдет ток, пропорциональный правой части уравнения (5).

Таким образом, функцией третьего блока 8 памяти является хранение информации о величинах разности (Sj t s,r s,,n-« для всего массива узловых точек R-сетки.

Устройство работает следующим образом.

Производится подготовка устройст- ва к решению задачи, во время которой производится занесение начального распределения функции S-F в блок 8 памяти, функциональной зависимости F{9) - в блок 7 памяти, количество

31363269

точек, участвующих в рерлении

д н ни ув ся ни

данной задачи, - в регистр 27, коли чество временных шагов - в регистр 30 (на блок-схеме устройства не показаны перечисленные операции, а также непринципиальные моменты установки блоков и злементов в исходное состояние ).

По сигналу Пуск разрешается про-ig ботки информации следующей узловой

хождение тактовых импульсов с генератора 8 через элемент И 19 на вход счетчика 20 (микрокоманд) и далее на дешифратор 21 , с выходов которого поступают сигналы синхронизации на 15 функциональные блоки устройства, выполняющие в определенной последовательности операции, связанные с обработкой и обменом информацией между блоками устройства для одной, напри- уп мер i-й точки.

По сигналу а, поступающему с дешифратора 21,происходит пуск коммутатора 5 по адресу, сформированноточки. Этот процесс повторяется до появления на блоке 26 сравнения импульса к, свидетельствующего об окончании съема и обработки информации дая всех точек, задействованных в решении задачи. По сигналу к происходит одновременная запись (0 + +F) (,., источники 3 напряжения из регистровой памяти 4, после чего может быть получено решение -на R-сетке 1 для данной итерации. Сигнал к также поступает с блока 26 на один из входов элемента И 15 и в случае наличия на выходе триг-

30

35

му счетчиком 24. Ком1.1утатор 5 подклю-25 гера 14 1 устанавливает триггер 16 чает выбранную узловую точку R-сетки 1 к входу аналого-цифрового преобразователя (АЦП) 6, который производит преобразование по сигналу б с дешифратора 21. По этому же сигналу

считывается информация блока

. „

Ш памяти, которая тут же вычитается

из поступающей с выхода 6. Эта операция производится cvMMaTopoM 12. Полученная разность (0 - ) поступает на блок 13, где сравнивается с кодом машинного нуля, имеющего единицу в младшем разряде.

Если старр1ие разряды е равны нулю, то блок 1.3 вьщает сигнал на вход триггера 14, который устанавливается в единичное состояние, в противном случае он остается в нулевом состоянии. По сигналу в происходит считывание информации о функции F. (в) из блока 7 памяти по адресу, посту- пающему с выхода АЦП 6, а также запись блок.„Ш памяти для следукг- щеГо итерационного цикла по адресу 1-й точки..

40

тоже в единичное состояние, которое, в свою очередь, устанавливает триггер 14 в О. Это служит сигналом для организации цикла съема результатов решения с R-сетки 1 и записи информации в блок 8 памяти о разности

e5,t hH-Fsa,h.i- Отсутствие 1 на выходе триггера 16 говорит о том, что итерационный процесс еще не сошелся и нужно перейти к следующей итерации. Для этого достаточно, чтобы сигнал к через элемент 31 задержки устайовил счетчик 24 внулевое состояние. Очередная итерация производится по описанному алгоритму.

Когда итерационный процесс сошелся и нужно осуществить переход к следующему временному шагу, работа устройства меняется. Если сигналы

б

в с дешифратора 21

а J

полняют те же функции, то сигнал г проходить не будет, так как потенциал на выходе триггера 16 d будет равен О и элемент И 22 не пропустит сигнал г, разрешающий считывание из блока 8 памяти. Вместо этого на вход разрешения записи блока 8 памяти поступит сигнал д, прохождение которого разрешает потенциал d выхода 55 триггера 16. Сигнал е будет заблокирован сигналом d, и запись в память 4 не произойдет. После того, как Закончится цикл в блоке 8 памяти и бу- дет подготовлена информация для на-

По сигналу г происходит считывание информации о разности (0-Р)- из блока 8 памяти по адресу i-й узловой точки и передача ее в сумматор 9, где складываются величины (б-Р). Далее эта информация с

и F

(V.)

1,П

,п-л

выхода сумматора поступает на i-й вход регистровой памяти 4, где записывается по i-му адресу по сигналу синхронизации е.

ж

При появлении сигнала ж на выходе дешифратора 21 происходит установка счетчика 20 в нулевое состояние, а на выходе счетчика 24 код увеличивается на единицу, что является изменением адреса узловой точки. Далее блок 17 переходит к формированию сигналов синхронизации для обра-

точки. Этот процесс повторяется до появления на блоке 26 сравнения импульса к, свидетельствующего об окончании съема и обработки информации дая всех точек, задействованных в решении задачи. По сигналу к происходит одновременная запись (0 + +F) (,., источники 3 напряжения из регистровой памяти 4, после чего может быть получено решение -на R-сетке 1 для данной итерации Сигнал к также поступает с блока 26 на один из входов элемента И 15 и в случае наличия на выходе триг

гера 14 1 устанавливает триггер 16

тоже в единичное состояние, которое, в свою очередь, устанавливает триггер 14 в О. Это служит сигналом для организации цикла съема результатов решения с R-сетки 1 и записи информации в блок 8 памяти о разности

e5,t hH-Fsa,h.i- Отсутствие 1 на выходе триггера 16 говорит о том, что итерационный процесс еще не сошелся и нужно перейти к следующей итерации. Для этого достаточно, чтобы сигнал к через элемент 31 задержки устайовил счетчик 24 внулевое состояние. Очередная итерация производится по описанному алгоритму.

Когда итерационный процесс сошелся и нужно осуществить переход к следующему временному шагу, работа устройства меняется. Если сигналы

б

в с дешифратора 21 вы

я

а J

полняют те же функции, то сигнал г проходить не будет, так как потенциал на выходе триггера 16 d будет равен О и элемент И 22 не пропустит сигнал г, разрешающий считывание из блока 8 памяти. Вместо этого на вход разрешения записи блока 8 памяти поступит сигнал д, прохождение которого разрешает потенциал d выхода триггера 16. Сигнал е будет заблокирован сигналом d, и запись в память 4 не произойдет. После того, как Закончится цикл в блоке 8 памяти и бу- дет подготовлена информация для на-

чальных условий следующего временного тага, триггер 14 установится в 1, так как итерационный процесс сошелся, а триггер 16, имеюкряй счетный вход при поступлении на элемент И 15 сигнала к установится в нулевое состояние. Триггер 14 остается в этом случае в состоянии 1, но. это не отражается на работе устройства. Останов решения происходит по сигналу с блока 29 сравнения, который сбрасьгоа- ет триггер 33 в О, и потенциал с его выхода запрещает прохождение -импульсов с генератора 18 через элемент И 19 на вход счетчика 20.

Формула изобретения

1. Устройство для решения нелинейных задач теплопроводности, содержащее R-сетку, последовательно соединенные коммутатор и аналого-цифровой преобразователь, причем узлы R-сетки соединены с информационными входами коммутатора, блок кодоуправляемых источников напряжения, выход каждого кодоуправляемого источника напряжения блока соединен с выводом соответствующего резистора R-сетки,отличающееся тем, что, с целью упро- щения, оно содержит три блока памяти, три блока сумматоров, блок сравнения, два триггера, элемент К, регистровую память и блок синхронизации, вход пуска которого является входом пуска устройства, первый выход блока синхро- низации соединен с первым управляющим входом коммутатора, второй выход блока синхронизации подключен к управляющему входу аналого-цифрового преобразователя и к входу управления режимом считывания первого блока памяти, третий выход блока синхронизации подключен к входу управления режимом считывания второго блока памяти, к входу управления режимом зали- си первого блока памяти и к тактирующему входу первого триггера, четвертый и выходы блока синхронизации соединены соответственно с входом управления режимом считывания и вхо- дОм управления режимом записи третьего блока памяти,шестой выход блока синхронизации подключен к тактирующему входу регистровой памяти, седьмой выход блока синхронизации соединен с вторым управляюсщм входом коммутатора, с адресными входами первог и третьего блоков памяти, группа выходов блока синхронизации подключена

0

5

5

550

к адресным входам регистровой памяти, восьмой выход блока синхронизации подключен к тактирующему входу блока кодоуправляемых источников напряжения и первому входу элемента И, вьгход аналого-цифрового преобразователя соединен с первым входом первого сумматора, с адресным входом второго блока памяти, с первым входом второго сумматора и информационным входом первого блока памяти, выход которого подключен к второму входу второго сумматора, выход которого через блок сравнения соединен с единичным входом первого триггера, прямой выход которого подключен к второму входу элемента И, выход которого подключен к счетному входу второго триггера, прямой, выход которого подключен к нулевому входу первого триггера и входу разрешения блока синхронизации,вход блокировки которого соединен с инверсным выходом второго триггера, выход второго блока памяти подключен к второму входу первого сумматора и к первому входу третьего сумматора, выход которого соединен с информационным входом регистровой памяти, выход третьего блока памяти подключен к второму входу третьего сумматора, выход первого сумматора подключен к информационному входу третьего блока памяти, выход регистровой памяти соединен с информационным входом блока кодоуправляемых источников напряжения.

2. Устройство по п. 1. отличающееся тем. что блок синхронизации включает четыре элемента К, два дешифратора, три счетчика, элемент задержки, триггер, два регистра, два блока сравнения и генератор тактовых импульсов, выход которого подключен к первому входу пер- 45 вого элемента И, выход которого соединен с.о счетным входом первого счетчика, выход которого подключен к входу первого дешифратора, первый, второй и третий выходы которого являются соответственно первым, вторым и третьим выходами блока синхронизации, четвертый выход первого дешифратора соединен с первыми входами второго и третьего элементов И, вторые входы которых являются соответственно входами блокировки и разрешения блока синхронизации, пятый выход первого дешифратора подключен к первому входу четвертого элемента И, второй

0

0

55

вход которого соединен с входом блокировки блока синхронизации, шестой выход первого дершфратора подключен к установочному входу первого счетчика и к счетному входу второго счетчика, выход которого является седьмым выходом блока синхронизации и соединен с первым входом первого блока сравнения и с входом второго дешифратора, выходы которого являются группой выходов блока синхронизации, выход первого регистра подключен к второму входу первого блока сравнения, выход которого является восьмым

8

выходом блока синхронизации и соединен с входом элемента задержки и со счетным входом третьего счетчика, вы- ход которого подключен к первому входу второго блока сравнения, выход которого соединен с нулевым входом триггера, единичный вход которого является входом пуска блока синхронизации, выход триггера подключен к вто- . рому входу первого элемента И, выход . элемента задержки соединен с установочным входом второго счетчика, выход второго регистра подключен к второмт входу второго блока сравнения.

Га

L

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения нелинейных задач теории поля | 1983 |

|

SU1156101A1 |

| Устройство для решения краевых задач | 1983 |

|

SU1149286A1 |

| Узловой элемент цифровой сетки для решения краевых задач | 1984 |

|

SU1246111A1 |

| Устройство для решения систем алгебраических уравнений | 1984 |

|

SU1203552A1 |

| Устройство для решения системы линейных алгебраических уравнений | 1986 |

|

SU1405073A1 |

| Устройство для решения дифференциальных уравнений | 1982 |

|

SU1104513A1 |

| Вычислительное устройство для решения дифференциальных уравнений | 1985 |

|

SU1277134A1 |

| Устройство для вычисления функции | 1984 |

|

SU1180884A1 |

| Вычислительный блок матричного устройства для решения дифференциальных уравнений в частных производных | 1989 |

|

SU1605253A1 |

| Устройство для моделирования биматричных игр | 1986 |

|

SU1388847A1 |

Изобретение относится к гибридной вычислительной технике и предназначено для моделирования нелинейных задач теплопроводности. Цель изобретения - упрощение схемы. Поставленная цель достигается тем, что устройство включает три блока памяти, три блока сумматоров, блок сравнения, два триггера, элемент И, регистровую память, блок синхронизации, состоящий из генератора тактовьгх импульсов, четырех элементов И, трех счетчиков, двух дешифраторов, двух блоков сравнения, двух регистров, элемента задержки и триггера. 1 з.п, ф-лы, 2 ил. i (Л О5 О5 со ю С5 СО

bil

17

ffliiV

.а I

:1

Фиг. /

Составитель И.Дубинина Редактор Е.Кспча Техред А.Кравчук

Заказ 6365/43 Тираж 671,Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Vue.2

Корректор А.Обручар

| Козлов Э.С | |||

| и др | |||

| Назначение и | |||

| принципы построения аналого-цифрового вычислительного комплекса Сатурн | |||

| В кн.: Средства аналоговой и аналого- цифровой вычислительной техники | |||

| М.: Машиностроение, 1968, с | |||

| Переносный кухонный очаг | 1919 |

|

SU180A1 |

| Устройство для моделирования теплопроводности | 1974 |

|

SU491963A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-30—Публикация

1986-07-28—Подача